- Преподавателю

- Информатика

- МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПО ВЫПОЛНЕНИЮ ПРАКТИЧЕСКИХ РАБОТ ПО УЧЕБНОЙ ДИСЦИПЛИНЕ ОП. 09. ЦИФРОВАЯ СХЕМОТЕХНИКА

МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПО ВЫПОЛНЕНИЮ ПРАКТИЧЕСКИХ РАБОТ ПО УЧЕБНОЙ ДИСЦИПЛИНЕ ОП. 09. ЦИФРОВАЯ СХЕМОТЕХНИКА

| Раздел | Информатика |

| Класс | 11 класс |

| Тип | Другие методич. материалы |

| Автор | Рымашевская С.Э. |

| Дата | 07.08.2015 |

| Формат | docx |

| Изображения | Есть |

МИНИСТЕРСТВО ТРАНСПОРТА РОССИЙСКОЙ ФЕДЕРАЦИИ

МИНИСТЕРСТВО ТРАНСПОРТА РОССИЙСКОЙ ФЕДЕРАЦИИ

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА

ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ

САМАРСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ПУТЕЙ СООБЩЕНИЯ

ФИЛИАЛ

ОРЕНБУРГСКИЙ ИНСТИТУТ ПУТЕЙ СООБЩЕНИЯ

ОРЕНБУРГСКИЙ ТЕХНИКУМ ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА

(ОТЖТ ОрИПС - филиала СамГУПС)

Методические указания ПО ВЫПОЛНЕНИЮ практических РАБОТ

по учебной дисциплине

ОП.09. ЦИФРОВАЯ СХЕМОТЕХНИКА

для студентов специальности

220415 Автоматика и телемеханика на транспорте (на железнодорожном транспорте)

Базовая подготовка

среднего профессионального образования

Оренбург

2014

Методические указания по выполнению практических работ по учебной дисциплине ОП.09.Цифровая схемотехника разработаны на основе рабочей программы учебной дисциплины ОП.09. Цифровая схемотехника для студентов специальности 220415 Автоматика и телемеханика на транспорте (на железнодорожном транспорте) и Рекомендаций по планированию и проведению лабораторных и практических занятий от 13.10.2013 года.

Разработчик:

ОТЖТ ОрИПС - филиала СамГУПС преподаватель С.Э. Рымашевская_

(место работы) (занимаемая должность) (инициалы, фамилия)

Рассмотрено и одобрено на заседании предметной (цикловой) комиссии _________________________________________________________

Протокол №_______ от «_____» _________ 20____г.

Председатель ПЦК ________________________ /______________

Введение

Данное методическое пособие разработано для студентов специальности 220415 Автоматика и телемеханика на транспорте при выполнении лабораторных работ и практических занятий по дисциплине «Цифровая схемотехника» и составлено в соответствии с рабочей программой по данной дисциплине.

Лабораторные работы и практические занятия по дисциплине «Цифровая схемотехника» направлены на систематизацию и закрепление определенных практических умений и навыков; самостоятельную обработку экспериментальных данных, анализ полученных результатов, выводы по работе. При этом студенты должны уметь пользоваться учебной, справочной и технической литературой.

Для проведения лабораторных работ и практических занятий учебную группу рекомендуется делить на подгруппы численностью 12-15 человек.

К выполнению лабораторных работ или практических занятий студенты приступают только после прохождения инструктажа по технике безопасности и охране труда, с ознакомлением с правилами поведения студентов при подготовке и проведения практического или лабораторного занятия, требований к рабочему месту, ответственности за сохранность приборов и оборудования, с оформлением соответствующей записи в журнале инструктажа.

Перед началом занятия студент должен знать:

-

правила охраны труда при работе с электрическими устройствами и приборами;

-

последовательность ее выполнения;

-

распределение обязанностей между членами в учебной бригаде;

-

характер ожидаемых результатов.

Подготовка к лабораторным работам

Ознакомиться с описанием соответствующей лабораторной работы и установить, в чем состоит ее основная цель и задача.

Изучить теоретический материал, относящийся к данной лабораторной работе, по лекционному курсу и соответствующим литературным источникам.

До проведения лабораторных работ выполнить подготовку, содержащую: схемы, таблицы измерений и расчетные формулы, порядок выполнения.

Требования к выполнению лабораторных работ

К выполнению лабораторной работы допускаются только подготовившиеся к этой работе студенты, прошедшие инструктаж по технике безопасности.

Перед сборкой схемы ознакомиться с электрическим оборудованием и измерительными приборами, предназначенными для проведения лабораторной работы. Приступая к сборке схемы, необходимо прежде всего убедиться в том, что напряжение на стенде отключено. Строго руководствоваться порядком выполнения лабораторной работы. При сборке схемы необходимо обеспечивать достаточную плотность и надежность контактов. После окончания сборки схема должна быть предъявлена для проверки. Схема включается под напряжение только с разрешения преподавателя, ведущего занятия, или дежурного лаборанта.

Запись показаний приборов в процессе выполнения лабораторной работы следует проводить по возможности одновременно и быстро, строго соблюдая при этом правила эксплуатации измерительных средств. Результаты измерений заносятся в отчет.

После окончания работы электрическая схема должна быть разобрана, рабочее место убрано, дополнительные приборы, исследуемые микросхемы и соединительные провода сданы.

В течение всего времени занятий в лаборатории студенты обязаны находиться на своих рабочих местах. Выходить из помещения лаборатории во время занятий студенты могут только с разрешения преподавателя.

Требования к отчетам по лабораторным работам и практическим занятиям

Отчет оформляется в письменной форме в соответствии с правилами и требованиями образовательного учреждения и с соблюдением требований ЕСКД и ГОСТов.

При составлении отчета по работе необходимо руководствоваться следующими положениями:

В отчете должны быть указаны порядковый номер и название лабораторной работы или практического занятия, цель работы, оборудование, порядок выполнения, вывод.

Схемы и графики должны быть вычерчены карандашом с помощью чертежных инструментов с соблюдением буквенных и графических условных обозначений или выполнены на персональном компьютере.

Студенты, не предъявившие в начале лабораторной работы или практического занятия оформленного отчета по предыдущей работе, к выполнению следующей не допускаются.

Текст выполняется на листах формата А4 (210х 297 мм) по ГОСТ 2.301.

Текст выполняют одним из следующих способов:

- машинописным - через полтора-два интервала . шрифт пишущей машинки должен быть четким, высотой не менее 2,5 мм, лента только черного цвета (полужирная). Формулы в машинописный текст вносят от руки;

- с применением печатающих и графических устройств вывода ЭВМ (ГОСТ 2.004).

Допускается выполнять текст рукописным способом чертежным шрифтом по ГОСТ 2.304 с высотой букв не менее 2,5 мм, а цифр - 5 мм. Цифры и буквы необходимо выполнять тушью или пастой (чернилами) черного цвета.

На компьютере текст должен быть оформлен в текстовом редакторе Microsoft Office Word.

Тип шрифта:

-

GOST type B (курсив).

Шрифт основного текста: обычный, размер 14 ПТ. Шрифт заголовков разделов: 22 ПТ. Шрифт заголовков подразделов: 14 ПТ. Межсимвольный интервал: обычный. Межстрочный интервал: полуторный. Формулы должны быть оформлены в редакторе формул и вставлены в документ как объект.

Размеры шрифта для формул:

- обычный - 14 ПТ;

- крупный индекс - 10 ПТ;

- мелкий индекс - 8 ПТ;

- крупный символ - 20 ПТ;

- мелкий символ - 14 ПТ.

Иллюстрации должны быть вставлены в текст:

- либо командами «Вставка-рисунок», которые позволяют вставить рисунки из коллекции, из других программ и файлов, со сканера, созданные кнопками на панели рисования, автофигуры, объекты Word Art, диаграммы (все иллюстрации, вставляемые как рисунок, должны быть преобразованы в формат графических файлов, поддерживаемых Word);

- либо командами «Вставка-объект», при этом необходимо, чтобы объект, в котором создана вставляемая иллюстрация, поддерживался редактором Word стандартной конфигурации.

Расстояние от верхней или нижней строки текста пояснительной записки до верхней или нижней рамки листа должно быть не менее 10мм. Расстояние от рамки формы до границ текста в начале и в конце строк должно быть не менее 3 мм. Абзацы в тексте начинают отступом, равным 15-17 мм.

Страницы следует нумеровать арабскими цифрами, соблюдая сквозную нумерацию по всему тексту. Номер страницы проставляют в правом нижнем углу без точки в конце.

Опечатки, описки и графические неточности, обнаруженные в процессе выполнения, допускается исправлять подчисткой или закрашиванием белой краской и нанесением в том же месте исправленного текста машинописным способом или черными, помарки и следы не полностью удаленного прежнего текста не допускаются. Можно наклеивать рисунки, фотографии.

Инструктаж по охране труда

1. Перед началом лабораторных занятий необходимо ознакомиться с правилами по охране труда.

2. Все переключения в схемах следует производить только при выключенном питании.

3. Включать напряжение можно только с разрешения преподавателя.

4. Запрещается прикасаться к токоведущим участкам схем, находящимся под напряжением.

5. Вся аппаратура, используемая на рабочем месте, должна быть надежно заземлена.

6. При обнаружении любой неисправности необходимо отключить питание и доложить преподавателю.

7. Наличие напряжения на участках схем следует проверять только с помощью специальных индикаторов.

8. Запрещается пользоваться приборами и оборудованием, которые не требуется для выполняемой работы, и переносит приборы с одного рабочего места на другое.

9. Разбирать, схему разрешается только после отключения питания.

Практическое занятие №1

Кодирование целых, дробных и смешанных чисел в различных системах счисления

Цель: научиться кодировать числа в различных системах счисления.

Оборудование: раздаточный материал.

Краткие теоретические сведения

Арифметические действия, выполняемые в двоичной системе, подчиняются тем же правилам, что и в десятичной системе. Только в двоичной системе счисления перенос единиц в старший разряд возникает чаще, чем в десятичной. Вычитание многоразрядных двоичных чисел производится с учетом возможных заёмов из старших разрядов. Действия умножения и деления в двоичной арифметике можно выполнять по общепринятым для позиционных систем правилам.

Сложение двоичных чисел. Способ сложения столбиком такой же, как и для десятичного числа. То есть, сложение выполняется поразрядно, начиная с младшего. Если получается больше 1, то записывается 0 и 1 добавляется к старшему разряду. Вот так выглядит таблица сложения в двоичной системе:

Таблица 1 Сложение двоичных чисел

0+0=0

0+1=1

1+0=1

1+1=10 (перенос в старший разряд)

Пример 1: 10011 + 10001.

1

0

0

1

1

1

0

0

0

1

1

0

0

1

0

0

Переведём все три числа в десятичную систему и проверим правильность сложения.

10011 = 1*24 + 0*23 + 0*22 + 1*21 + 1*20 = 16 + 2 + 1 =19

10001 = 1*24 + 0*23 + 0*22 + 0*21 + 1*20 = 16 + 1 = 17

100100 = 1*25 + 0*24 + 0*23 + 1*22 + 0*21 + 0*20 =32+4=36

17 + 19 = 36 верное равенство

Вычитание двоичных чисел. Вычитание выполняется поразрядно и если в разряде не хватает единицы, то она занимается в старшем.

Пример 2:

1

1

0

1

-

1

1

0

1

1

1

Первый разряд. 1 - 0 =1. Записываем 1.

Второй разряд 0 -1. Не хватает единицы. Занимаем её в старшем разряде. Единица из старшего разряда переходит в младший, как две единицы (потому что старший разряд представляется двойкой большей степени ) 2-1 =1. Записываем 1.

Третий разряд. Единицу этого разряда мы занимали, поэтому сейчас в разряде 0 и есть необходимость занять единицу старшего разряда. 2-1 =1. Записываем 1.

Проверим результат в десятичной системе:

1101 - 110 = 13 - 6 = 7 (111) Верное равенство.

Умножение в двоичной системе счисления. Таблица умножения для двоичных чисел ещё проще, чем для сложения.

Таблица 1 Умножение двоичных чисел

0*0=0

0*1=0

1*0=0

1*1=1

Для того, чтобы умножить двоичное число на 2 (десятичная двойка это 10 в двоичной системе) достаточно к умножаемому числу слева приписать один ноль.

Пример 3: 10101 * 10 = 101010

Проверка.

10101 = 1*24 + 0*23 + 1*22 + 0*21 +1*20 = 16 + 4 + 1 = 21

101010 =1*25 + 0*24 + 1*23 + 0*22 +1*21 +0*20 = 32 + 8 + 2 = 42

21 * 2 = 42

Умножение - это ряд последовательных сдвигов. Общее правило таково: как и для десятичных чисел, умножение двоичных выполняется поразрядно. И для

каждого разряда второго множителя к первому множителю добавляется один ноль справа. Пример 4:(пока не столбиком):

1011 * 101 Это умножение можно свести к сумме трёх поразрядных умножений:

1011 * 1 + 1011 * 0 + 1011 * 100 = 1011 +101100 = 110111 В столбик это же самое можно записать так:

1

0

1

1

1

0

1

1

0

1

1

+

0

0

0

0

1

0

1

1

1

1

0

1

1

1

Проверка:

101 = 5 (десятичное) 1011 = 11 (десятичное)

110111 = 55 (десятичное) 5*11 = 55 верное равенство

Порядок выполнения

-

Выполнить арифметическую операцию сложения в двоичной системе.

-

Выполнить арифметическую операцию вычитания в двоичной системе.

-

Выполнить арифметическую операцию умножения в двоичной системе.

-

Ответить на контрольные вопросы.

Содержание отчёта

-

Номер, название и цель практической работы.

-

Сложение, вычитание и умножение чисел в двоичной системе.

-

Вывод.

Контрольные вопросы

-

С какого разряда начинается сложение?

-

В каком разряде занимается единица при вычитании?

-

Как производится перевод чисел из десятичной системы в двоичную.

Практическое занятие №2

Кодирование положительных и отрицательных двоичных чисел в прямом, обратном,

дополнительном и модифицированном кодах со знаковым и без знакового разряда

Цель: научиться кодировать числа в различных кодах.

Оборудование: раздаточный материал.

Краткие теоретические сведения

Минимизация (упрощение) булевой функции - это такие тождественные преобразования её формулы, которые приводят к предельному уменьшению числа вхождений аргументов. В результате преобразований получается минимальная форма. Если ограничиться функцией четырех переменных аргументов, то для минимизации эффективней пользоваться картами Карно. Для этого достаточно научиться находить на карте группы единиц, которым соответствуют простые импликанты. Правила их нахождения просты:

а) два минтерма склеиваются, если они являются соседними, т. е. расположенными рядом (но не на диагонали) либо на концах строки или столбца. На рис. 1 обведены склеивающиеся минтермы 11 и 15, 3 и 11; склеиваются также минтермы 4и12,8и12;

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Рис. 1 Рис. 2 Рис. 3

б) четыре единицы на карте объединяются и образуют одну конъюнкцию, если они расположены в строку или столбец, а также квадратом. На рис. 2 слева единицы дают конъюнкцию АС, остальные - АС. На рис. 3 единицы, расположенные в строку, образуют конъюнкцию BD, в колонку - АС. На рис. 4 единицы расположены квадратами: АВ и АВ. На рис. 5 единицы также образуют квадрат ВС, в чём можно убедиться, если карту, свернуть в трубку так, чтобы её левая и правая стороны совпали. Аналогично на рис. 6 единицы дают квадрат A D, если карту свернуть в цилиндр вокруг горизонтальной оси. Если же карту свернуть в цилиндр вокруг горизонтальной и вертикальной осей одновременно, то придётся признать, что размещение четырёх единиц по углам карты также есть квадрат, образующий конъюнкцию СD (рис. 7);

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Рис. 4 Рис. 5 Рис. 6

в) восемь единиц на карте объединяются, если все они расположены в зоне, относящейся к какой-либо букве или её инверсии. На рис. 8 восемь единиц объединяются, так как занимают всю зону буквы С, поэтому дизъюнкцию соответствующих восьми минтермов можно заменить буквой С. На рис. 9 единицами занята вся область буквы D, на рис. 10 - А.

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Рис.7 Рис. 8 Рис. 9

1

1

1

1

1

1

1

1

Рис. 10

Теперь можно переходить к отысканию простых импликант. Пусть задана функция: f= (0,1,3,6,7,8,12,13,14,15).

Нанесём её на карту Карно (рис. 11).

1

1

1

1

1

1

1

1

1

1

Рис.11

Начнём с нулевого минтерма. Он объединяется с минтермом m1, поскольку единицы являются соседними. Получим первую простую импликанту АВС. Минтерм m0 является соседним и по отношению к минтерму m8 , что дает простую импликанту ВСD.

Минтерм m1 объединяется и с минтермом m0 и m3. Получаем две простые импликанты ABD и ABC. Импликанту АВС вторично не записываем. Новой является только простая импликанта ABD.

Переходим к минтерму m3. У него также два варианта склеивания - с минтермами m1 и m7. Новой является импликанта ACD.

Минтерм m6 входит в группу единиц, расположенных квадратом. Поэтому простой импликантой будет конъюнкция ВС, но такие импликанты, как BCD и ABC не являются простыми.

Седьмой минтерм имеет три соседние единицы. Однако новых простых импликант он не даёт, поскольку объединение его с минтермом т3 есть простая импликанта ACD, которая уже была записана ранее, а импликанты ABC и BCD не являются простыми, так как минтерм m7 входит в квадрат единиц, также рассмотренный ранее.

Минтерм m12 входит в квадрат единиц, дающих конъюнкцию АВ. Это новая простая импликанта. Кроме того, минтерм m12 является соседним по отношению к минтерму m8, что даёт новую простую импликанту ACD. Минтерм m13 новых импликант не даёт. Минтерм m14 входит в два квадрата: АВ и ВС. Новых импликант нет. То же самое относится к минтерму m15.

Таким образом, найдены все простые импликанты, дизъюнкция которых образует сокращённую дизъюнктивную нормальную форму:

F = ABC + BCD + ABD + ACD + BC+ACD + AB

Порядок выполнения

-

Минимизировать логические функции методом карт Карно.

-

Составить схему.

-

Ответить на контрольные вопросы.

Содержание отчёта

-

Номер, название и цель практической работы.

-

Схемы карт Карно.

-

Вывод.

Контрольные вопросы

-

Поясните принцип минимизации.

-

Что получается в результате минимизации.

Практическое занятие №3

Выполнение арифметических операций с многоразрядными двоичными

кодированными числами со знаковым и без знакового разряда

Цель: научиться выполнять арифметические операции над кодированными числами.

Оборудование: раздаточный материал.

Краткие теоретические сведения

Под системой счисления понимается способ представления любого числа посредством некоторого алфавита символов, называемых цифрами. Существуют различные системы счисления. От их особенностей зависят наглядность представления числа при помощи цифр и сложность выполнения арифметических операций.

Римская непозиционная система счисления является примером системы с очень сложным способом записи чисел и громоздкими правилами выполнения арифметических операций.

Огромными преимуществами в наглядности представления чисел и в простоте выполнения арифметических операций обладают позиционные системы счисления. Этим объясняется то выдающееся значение для развития вычислений, которое имело создание арабами позиционной десятичной системы счисления, используемой нами в повседневной жизни.

Система счисления называется позиционной, если одна и та же цифра имеет различное значение, определяющееся позицией цифры в последовательности цифр, изображающей число. Это значение меняется в однозначной зависимости от позиции, занимаемой цифрой, по некоторому закону. Помимо десятичной системы существуют другие позиционные системы. Некоторые из них нашли применение в вычислительной технике.

Количество s различных цифр, употребляемых в позиционной системе, называется ее основанием. Эти цифры обозначают s целых чисел, обычно 0, 1, ... , (s - 1). В десятичной системе используются десять цифр: О, 1, 2, 3, 4, 5, 6, 7, 8, 9 и поэтому эта система имеет основанием число десять.

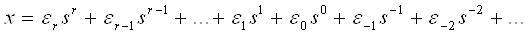

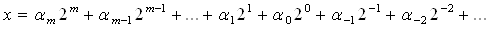

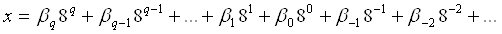

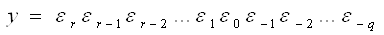

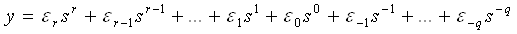

В общем случае позиционной системы с основанием s любое число х может быть представлено в виде полинома от основания s:

где в качестве коэффициентов εi могут стоять любые из s цифр, используемых в системе счисления.

Принято пользоваться эквивалентной, но более простой формой представления числа в виде последовательности соответствующих цифр:

В этой последовательности запятая отделяет целую часть числа от дробной (коэффициенты при положительных степенях s, включая нуль, от коэффициентов при отрицательных степенях). Запятая опускается, если нет отрицательных степеней. Позиции цифр, отсчитываемые от запятой, называют разрядами. В позиционной системе счисления значение каждого разряда больше значения соседнего справа разряда в число раз, равное основанию s системы.

С учетом сказанного в десятичной системе счисления запись 6097, 108 означает число:

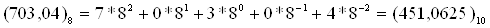

В электронных вычислительных машинах применяют позиционные системы счисления с недесятичным основанием: двоичную, шестнадцатеричную, восьмеричную и некоторые другие. В дальнейшем для обозначения используемой системы счисления будем заключать число в скобки и в индексе указывать основание системы счисления.

Наибольшее распространение в ЦВМ имеет двоичная система счисления. В этой системе используются только две («двоичные») цифры: (нуль) и 1 (единица).

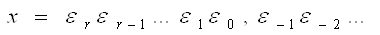

В двоичной системе любое число может быть, представлено соответствующей последовательностью двоичных цифр

где αi могут быть либо 0, либо 1. Эта запись соответствует сумме степеней числа 2, взятых с указанными в ней коэффициентами:

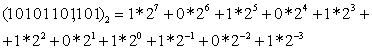

Например, двоичное число

как следует из приведенного разложения его по степеням числа 2, соответствует десятичному числу:

Изображения некоторых чисел в десятичной, двоичной, восьмеричной и шестнадцатеричной системах счисления показаны в таблице:

Десятичное

изображение

Двоичное

изображение

Восьмеричное изображение

Шестнадцатеричное

изображение

Десятичное

изображение

Двоичное

изображение

Восьмеричное изображение

Шестнадцатеричное

изображение

0

0

0

0

11

1011

13

B

1

1

1

1

12

1100

14

C

2

10

2

2

13

1101

15

D

3

11

3

3

14

1110

16

E

4

100

4

4

15

1111

17

F

5

101

5

5

16

10000

20

10

6

110

6

6

17

10001

21

11

7

111

7

7

18

10010

22

12

8

1000

10

8

1/4

0,01

0,2

0,4

9

1001

11

9

7/8

0,111

0,7

0,E

10

1010

12

A

4,5

100,1

4,4

4,8

Как видно из таблицы, а также из только что рассмотренного примера, двоичное изображение числа требует большего (для многоразрядного числа примерно в 3,3 раза) количества разрядов, чем его десятичное представление. Тем не менее применение двоичной системы позволяет уменьшить общее количество аппаратуры и создает большие удобства для проектирования цифровых вычислительных машин, так как для представления в машине разряда двоичного числа может быть использован любой простой элемент, имеющий всего два устойчивых состояния. Такими элементами, например, являются реле, триггерные схемы и т.п. Для представления десятичного разряда потребовалось бы четыре таких элемента.

Помимо двоичной системы счисления в ЦВМ используются также другие системы с недесятичным основанием - восьмеричная и шестнадцатеричная, имеющие основанием соответственно числа 8 и 16. В восьмеричной системе употребляются восемь цифр: 0, 1, 2, 3, 4, 5, 6, 7.

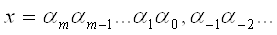

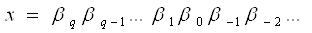

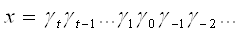

Любое число в восьмеричной системе представляется последовательностью цифр:

в которой βi могут принимать значения от 0 до 7. Этой записи соответствует разложение числа x по степеням числа восемь с приведенными ниже коэффициентами:

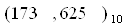

Например, восьмеричное число:

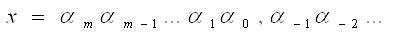

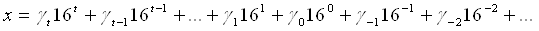

В шестнадцатеричной системе для изображения чисел употребляется 16 цифр от 0 до 15. При этом, чтобы одну цифру не изображать двумя знаками, приходится вводить специальные обозначения для цифр, больших девяти. Обозначим первые десять цифр этой системы цифрами от 0 до 9, а старшие пять цифр - латинскими буквами: десять - А, одиннадцать - В, двенадцать - С, тринадцать - D, четырнадцать - Е, пятнадцать - F. Записи произвольного числа в шестнадцатеричной системе в виде последовательности цифр:

где γi может принимать любые из 16 значений от 0 до F (пятнадцать), соответствует разложение числа х по степеням числа 16 с указанными ниже коэффициентами:

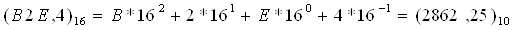

Например, шестнадцатеричное число:

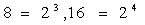

Основание любой системы счисления, записанное в этой же системе, имеет вид 10 (число два в двоичной системе есть 10, число восемь в восьмеричной системе есть 10 и т.д.). Общие методы перевода чисел из одной системы в другую будут изложены в следующем параграфе. Здесь мы ограничимся только рассмотрением правил преобразования восьмеричных и шестнадцатеричных чисел в двоичные и наоборот. Эти правила исключительно просты, поскольку основания восьмеричной и шестнадцатеричной систем есть целые степени числа два:

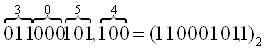

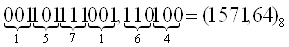

Для перевода восьмеричного числа в двоичную форму достаточно заменить каждую цифру восьмеричного числа соответствующим трехразрядным двоичным числом. Таким же образом для перехода от шестнадцатеричной системы к двоичной каждая цифра шестнадцатеричного числа заменяется соответствующим четырехразрядным двоичным числом. При этом отбрасывают ненужные нули. Например, восьмеричное число 305,4 в двоичной форме записи имеет вид:

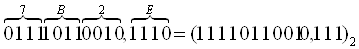

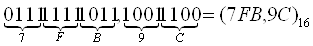

а шестнадцатеричное число 7В2,Е в двоичной системе запишется следующим образом:

Для перехода от двоичной к восьмеричной (или шестнадцатеричной) системе поступают следующим образом: двигаясь от запятой влево и вправо, разбивают двоичное число на группы по три (четыре) разряда, дополняя при необходимости нулями крайние левую и правую группы. Затем каждую группу из трех (четырех) разрядов заменяют соответствующей восьмеричной (шестнадцатеричной) цифрой.

Приведем примеры:

а) Перевод двоичного числа 1101111001, 1101 в восьмеричное:

б) Перевод двоичного числа 11111111011,100111 в шестнадцатеричное:

Двоичные числа, наборы цифр которых разбиты на группы по три (четыре) разряда, а крайние группы при необходимости дополнены нулями, можно считать восьмеричными (шестнадцатеричными) числами, в которых цифра каждого разряда записана в двоичной системе

в виде трех (четырех) разрядного двоичного числа. Такие формы записи чисел носят название двоично-восьмеричной и двоично-шестнадцатеричной системы. Они называются также двоично-кодированными системами.

В вычислительных системах также применяются специальные формы кодирования десятичных чисел. Этот вопрос будет рассмотрен ниже.

В настоящее время для большинства вычислительных машин основной системой счисления является двоичная. Двоичная система и двоичный алфавит используются во многих машинах для представления и хранения чисел и команд и при выполнении арифметических и логических операций.

Восьмеричная и шестнадцатеричная системы используются при составлении программ для более короткой и удобной записи двоичных кодов - команд, так как эти системы не требуют специальных операций для перевода в двоичную систему.

Числовые данные, необходимые для решения задачи, вводятся в машину обычно в десятичной системе в виде специальных кодов. Перевод десятичных чисел в двоичные выполняется машиной.

Результаты расчета выводятся из машины в десятичной системе. Перевод данных из двоичной системы в десятичную производится машиной.

При выводе из запоминающего устройства команд они печатаются в шестнадцатеричной (восьмеричной) системе. Числа также могут выводиться в шестнадцатеричной (восьмеричной) системе.

Двоичная арифметика

Правила выполнения арифметических действий над двоичными числами задаются таблицами двоичных сложения, вычитания и умножения:

Таблица двоичного сложения

Таблица двоичного

вычитания

Таблица двоичного умножения

0+0=0

0+1=1

1+0=1

1+1=0 +

+единица переносится

в старший разряд

0-0=0

1-0=1

1-1=0

0-1=1 +

+единица занимается

из старшего разряда

0*0=0

0*1=0

1*0=0

1*1=1

Правила арифметики во всех позиционных системах аналогичны. Поэтому сложение двух чисел в двоичной системе можно выполнять столбиком, начиная с младшего разряда, подобно тому, как мы это делаем в десятичной системе. В каждом разряде в соответствии с правилами, указанными таблицей двоичного сложения, производится сложение двух цифр слагаемых или двух этих цифр и единицы, если имеется перенос из соседнего младшего разряда. В результате получается цифра соответствующего разряда суммы и, возможно, также единица переноса в старший разряд. Приведем пример на сложение двух двоичных чисел.

Переносы:

Справа показано сложение тех же чисел, представленных в десятичной системе.

Вычитание чисел в двоичной системе выполняется подобно вычитанию в десятичной системе. При вычитании в данном разряде при необходимости занимается единица из следующего старшего разряда. Эта занимаемая единица равна двум единицам данного разряда. Занимание производится каждый раз, когда цифра в разряде вычитаемого больше цифры в том же разряде уменьшаемого. Поясним сказанное примером:

Умножение двоичных многоразрядных чисел производится путем образования частичных произведений и последующего их суммирования. В соответствии с таблицей двоичного умножения каждое частичное произведение равно нулю, если в соответствующем разряде множителя стоит нуль, или равно множимому, сдвинутому на соответствующее число разрядов влево, если в разряде множителя стоит единица. Таким образом, операция умножения многоразрядных двоичных чисел сводится к операциям сдвига и сложения. Положение запятой определяется так же, как при умножении десятичных чисел. Сказанное поясняется примером:

10111

10111

10101

____________

10111

00000

+ 10111

00000

10111

________________________

111100011

Деление чисел в двоичной системе производится аналогично делению десятичных чисел.

Достаточно рассмотреть деление двух целых двоичных чисел, так как делимое и делитель всегда могут быть приведены к такому виду путем перенесения запятой в делимом и делителе на одинаковое число разрядов и дописывания нулей в недостающие справа разряды.

Особенности выполнения деления двоичных чисел поясняются примером:

1100,011 : 10,01 = ?

1100011 10010

1100011 10010

10010 101,1

____________________

11011

10010

______________

10010

10010

______________

00000

Благодаря простоте правил двоичного сложения, вычитания и умножения применение в ЦВМ двоичной системы счисления позволяет упростить схемы арифметических устройств.

Правила перевода

Перейдем к рассмотрению правил перевода чисел из, одной системы счисления в другую.

Необходимость в таких преобразованиях возникает из-за того, что ЦВМ работает в двоичной системе счислений, программа записывается в шестнадцатеричной или восьмеричной системе, а подготовка исходных данных для расчетов и выдача результатов расчета из машины производятся в десятичной системе.

Обычно преобразования чисел из одной системы счисления в другую выполняются автоматически устройствами машины.

Однако при программировании задач, а также при вмешательстве оператора в процесс решения задачи на ЦВМ может возникать необходимость ручного перевода отдельного числа или небольшой группы чисел из одной системы в другую.

Правила перевода зависят от того, какая арифметика используется при выполнении арифметических операций, связанных с преобразованием чисел, - арифметика той системы счисления, в которой представлено исходное число, или арифметика системы счисления, в которую число переводится.

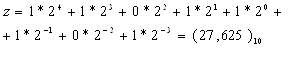

Пусть необходимо перевести число y, представленное в системе счисления с основанием s:

в h-систему, выполняя нужные для этого арифметические действия в новой h-системе. Для этого достаточно число представить в виде соответствующей суммы степеней s:

в которой основание s и все коэффициенты εi выражены в новой h-системе, и выполнить в h-системе все необходимые для вычисления этой суммы действия.

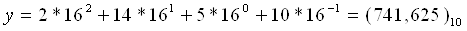

Пример 1. Перевести в десятичную систему шестнадцатеричное число у = (2Е5,А)16 . Для этого представляют у в виде:

Пример 2. Перевести в десятичную систему двоичное число z = (11011,101)2 :

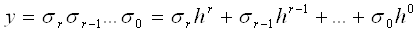

Рассмотрим теперь перевод числа из s-системы в h-систему посредством арифметических операций исходной s-системы. В этом случае правила для перевода целых чисел и дробей различны.

Перевод целых чисел

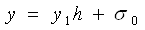

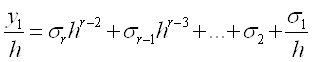

Пусть целое число у, представленное в s-системе, требуется перевести в h-систему. Искомая запись числа у в h-системе имеет вид:

Разделив у на h, получим:

Отсюда

где у1 есть частное от деления числа у на основание системы h, а младшая цифра искомого представления числа у в h-системе есть остаток от этого деления.

Если теперь разделить у1 на h, то получим:

В силу

остаток от второго деления есть цифра σ2 следующего разряда в представлении числа у в h-системе и т.д. Таким образом, получаем правило: для перевода целого числа из s-системы счисления в h-систему нужно последовательно делить это число и получаемые частные на Основание h новой системы, представленное в старой s-системе, до тех пор, пока частное не станет меньше h. Старшей цифрой в записи числа в h-системе служит последнее частное, а следующие за ней цифры дают остатки, выписываемые s последовательности, обратной их получению.

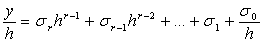

Перевод дробных чисел

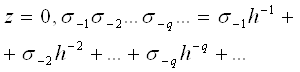

Перевод в h-систему правильной дроби z представленной в системе счисления с основанием s, означает запись этой дроби в виде:

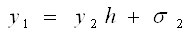

Умножая z на h получаем:

где σ-1 и z1 соответственно целая и дробные части этого произведения. При этом целая часть σ-1 есть старшая цифра в представлении числа z в h-системе.

Если теперь умножить на h правильную дробь z1, то целая часть произведения дает следующую цифру σ-2 в представлении числа в h системе.

Следовательно, можно сформулировать правило: для перевода правильной дроби из s-системы в систему счисления с основанием h нужно умножить исходную дробь и дробные части получающихся произведений на основание h, представленное в старой s-системе. Целые части получающихся произведений дают последовательность цифр в представлении дроби в h-системе.

Обычно перевод дробей из одной системы в другую производят приближенно.

При переводе неправильной дроби переводят отдельно целую и дробную части, руководствуясь соответствующими правилами.

Прямой, обратный и дополнительный коды

При проектировании вычислительных устройств необходимо решить вопрос о способе представления в машине положительных и отрицательных чисел и о признаке переполнения разрядной сетки. Указанный вопрос решается применением специальных колов для представления чисел. При помощи этих кодов операция вычитания (или алгебраического сложения) сводится к арифметическому сложению. В результате упрощаются арифметические устройства машин.

Для представления двоичных чисел в машине применяют прямой, обратный и дополнительный коды. Во всех этих кодах предусматривается дополнительный разряд для представления знака числа, причем знак «+» кодируется цифрой 0, а знак « - » - цифрой 1.

Положительные числа при прямом, обратном и дополнительном кодах имеют один и тот же вид, а отрицательные - различный.

Прямой код (G)пр двоичного числа G = ± 0, γ1, γ2, … , γn (γi = 1 или 0) определяется условиями:

G при G ≥ 0

(G)пр =

(1 - G) при G ≤ 0

Положительное двоичное число с запятой, фиксированной перед старшим разрядом,

G+ = + 0, γ1, γ2, … , γn

в прямом коде представляется в виде:

(G+) пр = 0, γ1, γ2, … , γn (1)

Аналогично отрицательное двоичное число:

G- = - 0, γ1, γ2, … , γn (1a)

в прямом коде представляется в виде:

(G-) пр = 1, γ1, γ2, … , γn (2)

Способы представления чисел (1) и (2) называются прямым кодом соответственно положительных и отрицательных двоичных чисел.

Сложение и вычитание в прямом, обратном и дополнительном кодах

Сложение в прямом коде чисел, имеющих одинаковые знаки, выполняется достаточно просто. Мантиссы складываются и сумме присваивается код знака слагаемых. Значительно более сложной является операция алгебраического сложения в прямом коде чисел с раз-

личными знаками. В этом случае приходится определять большое по модулю число, производить вычитание мантисс и присваивать разности знак большего (по модулю) числа. Таким образом, если положительные и отрицательные числа представлены в прямом коде, операции над кодами знаков и мантиссами выполняются раздельно.

Операция вычитания (алгебраического сложения) сводится к операции простого арифметического сложения при помощи обратного и дополнительного кодов, используемых для представления отрицательных чисел в машине. При этом операция сложения распространяется и на разряды знаков, рассматриваемых как разряды целой части числа.

Чтобы представить двоичное отрицательное число (1а) в обратном коде, нужно поставить в знаковый разряд единицу, а во всех других разрядах заменить единицы нулями, а нули - единицами:

(G-) обр = 1, σ1, σ 2, … , σ n (3)

σi = 1 при γi = 0 и σi = 0 при γi = 1.

При записи отрицательного числа в дополнительном коде ставят единицу в разряд знака, а цифровую часть числа заменяют дополнением модуля числа до целой единицы.

Отрицательное число G- = - 0, γ1, γ2, … , γn в дополнительном коде имеет вид:

(G-) доп = 1, ε1, ε 2, … , ε n (4)

где

0, ε1, ε 2, … , ε n = 1 - 0, γ1, γ2, … , γn (4a)

Установим связь между самим отрицательным числом G- и числами (G-)обр и (G-)доп , представляющими его обратный и дополнительный коды.

Вычитая (1а) из (3), имеем:

(G-) обр - G- = 1, σ1, σ 2, … , σ n - ( - 0, γ1, γ2, … , γn) = 1,11…1 = 2 - 2-n (так как σi + γi = 1)

Следовательно,

(G-) обр = G- + 2 - 2-n (4b)

Вычитая (1a) из (4), имеем:

(G-) доп - G- = 1, ε1, ε 2, … , ε n - ( - 0, γ1, γ2, … , γn) (5)

Учитывая (4a), получаем:

(G-) доп = G- + 2 (5а)

Из (5) и (5а) следует:

(G-) доп = (G-) обр + 2-n

где n - число разрядов в числе. Таким образом, дополнительный код может быть получен из обратного путем добавления к нему единицы младшего разряда.

Рассмотрим представление нуля. В процессе вычислений могут возникнуть «положительный» и «отрицательный» нули:

+ 0,00…0 ; - 0,00…0

Представление «положительного» нуля одинаково для прямого, обратного и дополнительного кодов:

(+ 0) пр = 0,00…0

Отрицательный нуль изображается: в прямом коде

(- 0) пр = 0,00…0

в обратном коде

(- 0) обр = 1,11…1

в дополнительном коде

(- 0) доп = 1,11…1 + 2-n = 0,00…0

так как перенос из разряда знака теряется.

Используя обратный или дополнительный код, можно операции вычитания и сложения чисел различных знаков свести к арифметическому сложению кодов чисел.

Рассмотрим использование обратного кода при алгебраическом сложении двух двоичных чисел G и Q, когда одно из них или оба числа отрицательны. Для этого случая может быть сформулировано следующее правило (предполагаем, что модуль алгебраической суммы меньше единицы).

При алгебраическом сложении двух двоичных чисел с использованием обратного кода положительные слагаемые представляются в прямом коде, а отрицательные - в обратном и производится арифметическое суммирование этих кодов, включая разряды знаков, которые при этом рассматриваются как разряды целых единиц. При возникновении переноса из разряда знака единица переноса прибавляется к младшему разряду суммы кодов (такой перенос называется круговым или циклическим). В результате получается алгебраическая сумма в прямом коде, если эта сумма положительна, и в обратном коде, если она отрицательна.

Рассмотрим теперь использование дополнительного кода для алгебраического сложения. Приведем соответствующее правило (полагаем, что модуль алгебраической суммы меньше единицы).

При алгебраическом сложении двух двоичных чисел с использованием дополнительного кода положительные слагаемые представляются в прямом коде, а отрицательные - в дополнительном и производится арифметическое суммирование этих кодов, включая разряды знаков, которые при этом рассматриваются как разряды целых единиц. При возникновении переноса из разряда знака единица переноса отбрасывается. В результате получается алгебраическая сумма в прямом коде, если эта сумма положительна, и в дополнительном коде, если эта сумма отрицательна.

В самом деле, если G- < 0 и Q- < 0 , то согласно (4b):

(G-) доп + (Q-) доп = G- + 2 + G- + 2 = 2 + (G- + Q- + 2)

Так как -1 < G- + Q- < 0, то величина, стоящая в скобках, меньше двух, но больше единицы. Двойка, стоящая вне скобки, образует перенос из разряда знака, который будет отброшен. В результате получаем:

(G-) доп + (Q-) доп = (G- + Q-) + 2 = (G- + Q-) доп

G+ > 0, а Q- < 0, то

(G+) пр + (Q-) доп = (G+ + Q-) + 2

Если при этом 0 < G+ + Q- < 1, то стоящая вне скобки двойка дает единицу переноса из разряда знака, которая отбрасывается. При этом получаем:

(G+) пр + (Q-) доп = (G+ + Q-) пр

(G+ + Q- > 0)

Если же -1 < G+ + Q- < 0, то (G+ + Q- ) + 2 < 2 и переноса из разряда знака не возникает. В этом случае:

(G+) пр + (Q-) доп = (G+ + Q-) доп

(G+ + Q- < 0).

Применение дополнительного или обратного кода для представления отрицательных чисел упрощает операцию алгебраического сложения. Алгебраическое сложение чисел с разными знаками заменяется арифметическим сложением кодов, при этом автоматически получается код знака результата. Однако остается нерешенным вопрос о выработке признака переполнения разрядной сетки.

При сложении кодов теряется единица переноса из разряда целых единиц и результат ошибочно воспринимается как положительное число, меньшее единицы.

Отметим, что при алгебраическом сложении двух чисел G и Q, каждое из которых по модулю меньше единицы, может возникнуть переполнение разрядной сетки, но при этом модуль получаемой суммы всегда меньше двух. Это обстоятельство облегчает построение кодов, по виду которых можно судить о переполнении разрядной сетки.

Для получения признака переполнения разрядной сетки применяют модифицированные прямой, дополнительный и обратный коды. Эти коды отличаются от ранее рассмотренных кодов тем, что для представления знака используются два разряда.

При этом знак плюс обозначается 00, а знак минус - 11. При алгебраическом сложении чисел знаковые разряды рассматриваются как разряды целой части числа.

При возникновении переноса единицы из старшего разряда знака эта единица отбрасывается, если отрицательные числа представляются модифицированным дополнительным кодом, или производится циклический перенос в младший разряд мантиссы, если отрицательные числа изображаются модифицированным обратным кодом.

При алгебраическом сложении на переполнение разрядной сетки (модуль алгебраической суммы больше единицы) указывает несовпадение цифр в знаковых разрядах. Комбинации 01 в знаковых разрядах соответствует положительное число, а комбинации 10 - отрицательное число.

В этих случаях модуль суммы:

1 ≤ |x| < 2

Отметим также особенности нормализации и выполнения сдвига для отрицательных чисел, представленных в дополнительном (обратном) коде.

У нормализованного положительного или отрицательного числа с мантиссой, изображаемой в прямом коде, цифра в старшем S-ичном разряде мантиссы должна быть отлична от нуля. Для отрицательных мантисс, представленных в обратном или дополнительном коде, условие нормализации |q| ≥ 1/S выполняется, если цифра в старшем S-ичном разряде мантиссы есть нуль.

В случае чисел с плавающей запятой комбинации 01 и 10 в знаковых разрядах мантиссы указывают на нарушение нормализации влево, а комбинации цифр 00 и 1 σs1 (σs1 ≠ 0) в младшем знаковом разряде и старшем S-ичном цифровом разряде мантиссы сигнализируют о нарушении нормализации вправо. Для восстановления нормализации производится сдвиг мантиссы вправо (или влево) на нужное число разрядов, при этом порядок увеличивается (уменьшается) на соответствующее число единиц,

Если отрицательные числа представляются в дополнительном (обратном) коде, сдвиг производится по особым правилам («модифицированный сдвиг»), с тем чтобы в результате сдвига дополнительного (обратного) кода числа х на m S-ичных разрядов получился дополнительный (обратный) код числа Smx или S-mх соответственно для сдвига влево или вправо.

При модифицированном сдвиге дополнительного (обратного) кода вправо в освобождающиеся старшие разряды мантиссы записываются единицы, а при сдвиге влево единицы записываются в освобождающиеся младшие разряды.

Деление в прямом, обратном и дополнительном кодах

Деление в вычислительной машине обычно сводится к выполнению последовательности вычитаний делителя сначала из делимого, а затем из образующихся в процессе деления частичных остатков и сдвига частичных остатков на один разряд влево.

Необходимо отметить, что в машинах, оперирующих над числами с запятой, фиксированной перед старшим разрядом, деление возможно только в одном случае, если делимое по модулю меньше делителя. В противном случае частное превышает единицу и выходит за пределы разрядной сетки числа. Если в результате вычитания выясняется, что делимое или очередной частичный остаток больше или равны делителю, то в очередной разряд частного записывается единица и полученный в результате вычитания частичный остаток сдвигается влево на один разряд. Если в результате вычитания выясняется, что делимое или очередной частичный остаток меньше делителя, то в очередной разряд частного записывается нуль, к полученной разрядности добавляется делитель, чтобы восстановить предыдущий частичный остаток, и результат сдвигается влево на один разряд. Метод выполнения деления, когда в случае получения отрицательного остатка при вычитании (частичный остаток меньше делимого) к нему прибавляется делитель, называется методом деления с восстановлением остатка.

Рассмотрим пример деления с восстановлением остатка (см. таблицу). Для выполнения операции вычитания будем использовать дополнительный код. Деление с восстановлением остатка требует в наиболее неблагоприятном случае трёх тактов для формирования одного разряда частного: такта вычитания, такта сложения и такта сдвига.

Рассмотренный метод носит название деления с восстановлением остатка.

Недостатком этого метода является необходимость введения специального третьего такта для восстановления остатка, который значительно замедляет ход вычисления.

Обычно в вычислительных машинах для деления широко используется другой метод, называемый методом выполнения деления без восстановления остатка. Этот метод основан на прямом копировании действий при ручном делении («в столбик»).

При этом методе, если результат вычитания получился отрицательный, частичный остаток не восстанавливается путём прибавления делителя, а на следующем шаге деления вместо вычитания делимого производится его прибавление к частичному остатку. Если результат при этом остался отрицательным, то в очередную цифру частного записывается нуль и на следующем шаге также выполняется сложение. Если результат сложения получился положительным, то в очередной разряд частного записывается единица и на следующем шаге производится вычитание.

Можно показать, что частичные остатки при делении без восстановления остатка получаются такими же, как и остатки после сдвига восстановленного остатка при делении с восстановлением остатка.

Действительно, поскольку сдвиг частичного остатка на один разряд влево эквивалентен умножению его на два, получим:

2a - b = 2(a -b) + b

где a - частичный остаток; b - делитель.

Аналогично:

Деление без восстановления остатка всегда требует для получения одной цифры частного только двух тактов: такта сложения или вычитания и такта сдвига. Тем самым скорость вычисления этим методом оказывается выше чем в методе деления с восстановлением остатка.

Деление правильных дробей выполняется также, как деление целых чисел. Разница же заключается в том, что делимое имеет, как правило, такую же длину, как и делитель. Однако можно предположить, что делимое имеет ещё n младших разрядов, равных 0. Тогда становится ясно, что алгоритм деления дробей ничем не отличается от алгоритма деления целых чисел.

Исходя из рассмотренных методов деления в вычислительных машинах наиболее скоростной и простой метод является метод деления без восстановления остатка, так как при использовании данного метода для получения одной цифры частного необходимо выполнить всего лишь два такта, в то время как в методе с восстановлением частичного остатка для получения одной цифры частного требуется три такта.

Практическое занятие №4

Построение схем цифровых логических устройств методом синтеза

Цель: исследования функционирования цифрового оборудования.

Оборудование: раздаточный материал.

Краткие теоретические сведения

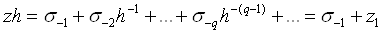

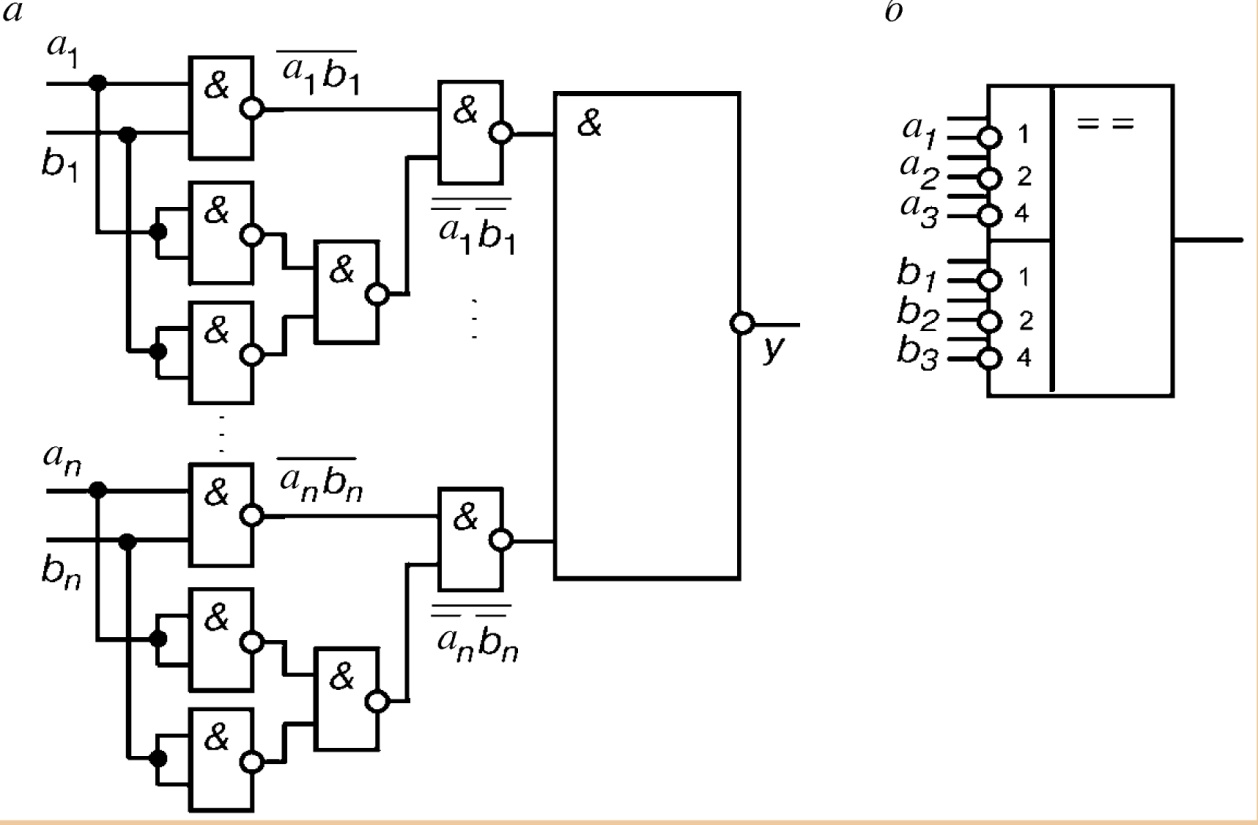

Цифровой компаратор предназначен для определения равенства двоичных чисел.

Два числа равны при равенстве цифр в одноименных разрядах

(аi = bi , где аi - цифра в i-м разряде одного числа; bi - цифра в том же разряде другого числа).

Равенство аi = bi имеет место при аi = 1, bi = 1 или при аi = 0, bi = 0.

Поэтому логическая функция, выражающая это равенство, равна единице, если единице равно произведение этих цифр или произведение их инверсных значений: y=aibi+aibi . Заметим, что записанная функция - функция «Равнозначность». Так как числа равны при равенстве цифр в первых, во вторых разрядах и в n-х разрядах, то логическая функция, выражающая равенство двух чисел - логическая функция, описывающая компаратор, имеет вид:

y = (a1 b1 + а1 b1) (a2 b2 + а2 b2) ... (an bn + аn bn).

Чтобы построить компаратор только на элементах И-НЕ, запишем ее в другой форме, используя теорему де Моргана:

a1b1 + а1 b1 an bn + аn bn = y

где отрицание левой части (при изменении в правой части y на у) сделано для той же цели.

Схема, реализующая это выражение, приведена на рис. 3.а Если необходимо, чтобы при равенстве кодов на выходе компаратора была логическая 1, то к выходу схемы следует присоединить инвертор.

Условное изображение цифрового компаратора приведено на рис. 1 а,

Рис. 1 - Условное изображение цифрового компаратора

Порядок выполнения

-

Изучить раздаточный материал.

-

Построить схему цифрового компаратора.

-

Ответить на контрольные вопросы.

Содержание отчёта

-

Номер, название и цель практического занятия.

-

Схема цифрового компаратора.

-

Вывод.

Контрольные вопросы

-

Для чего предназначен цифровой компаратор.

-

Какой теоремой пользуемся для представления компаратора на элементах И-НЕ.

-

В каком случае к выходу схемы следует присоединить

инвертор.

Лабораторное занятие №1

Исследование работы интегральных триггеров на логических элементах

Цель: исследование функционирования RS- триггеров, выполненных на базовых элементах ТТЛ «ИЛИ-НЕ» и «И-НЕ».

Оборудование: раздаточный материал

Краткие теоретические сведения

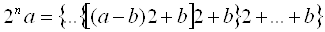

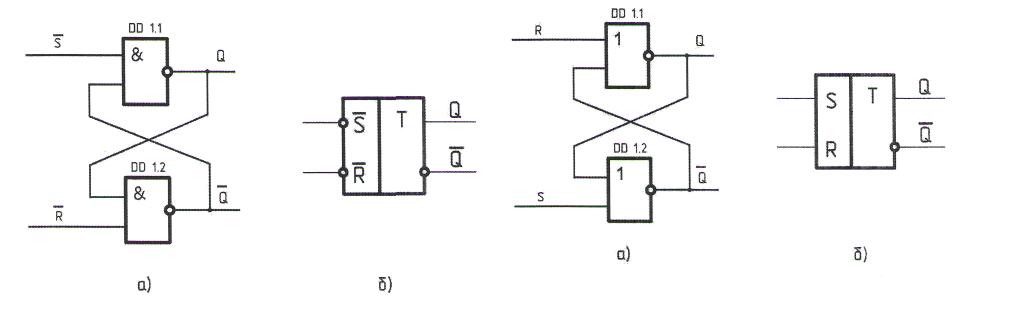

RS-триггер - это триггер с раздельной установкой состояний логического нуля и единицы (с раздельным запуском).

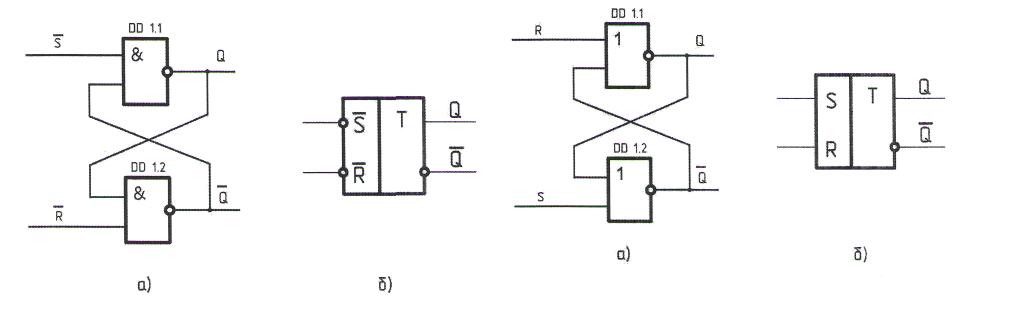

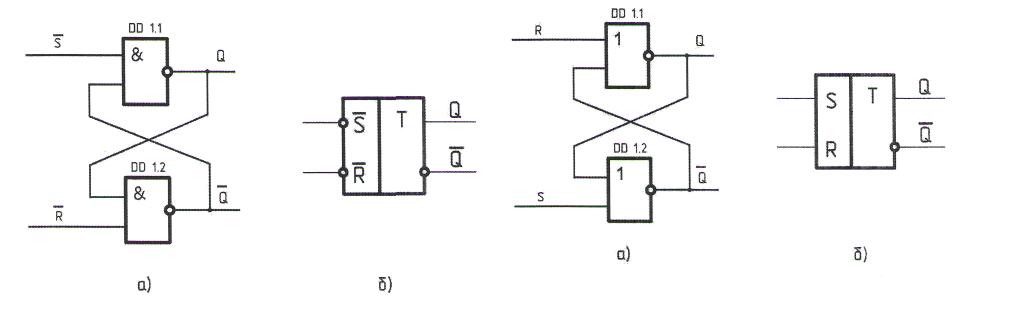

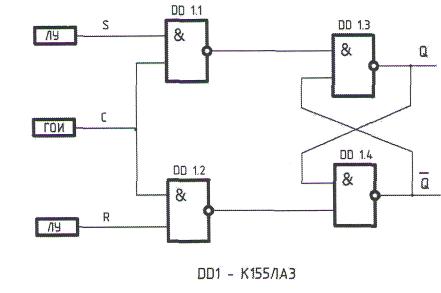

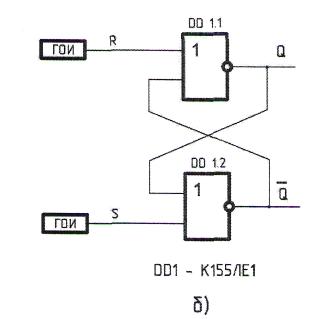

Асинхронные RS-триггеры. Они являются наиболее простыми триггерами. В качестве самостоятельного устройства применяются редко, но являются основой для построения более сложных триггеров. В зависимости от логической структуры различают RS-триггеры с прямыми и инверсными входами. Схема триггера с прямыми входами, построенного на двух логических элементах 2ИЛИ-НЕ, приведена на рис. 1 а), а его условное обозначение - на рис. 1 б). Выход каждого из логических элементов подключен к одному из входов другого элемента, что обеспечивает триггеру два устойчивых состояния.

Рис.1

Состояния триггера, построенного на логических элементах ИЛИ-НЕ, под воздействием определенной комбинации входных сигналов приведены в табл. 1.

Таблица 1

В таблице Qn (Qn ) обозначены уровни, которые были на выходах триггера до подачи на его входы так называемых активных уровней. Активным называют логический уровень, действующий на входе логического элемента и однозначно определяющий логический уровень выходного сигнала (независимо от логических уровней, действующих на остальных входах). Для элементов ИЛИ-НЕ активным уровнем является высокий уровень - 1. Уровни, подача которых на один из входов не приводит к изменению логического уровня на выходе элемента, называют пассивными. Уровни Qn+1 (Qn+1) обозначают логические уровни на выходах триггера после подачи информации на его входы.

Для триггера с прямыми входами режим записи логической единицы реализуется при S = 1, R = 0, режим записи логического нуля - при S = 0, R = 1. При S = R = 0 обеспечивается хранение информации. Комбинация входных сигналов S = R = 1 является запрещенной.

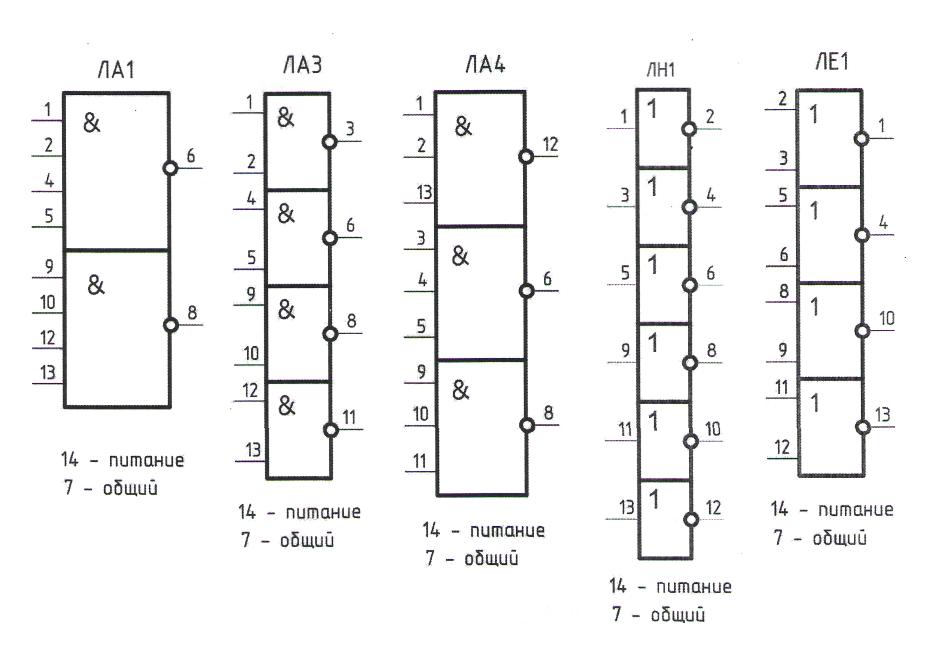

Условное обозначения микросхем ЛА3 и ЛЕ1 и их цоколевка приведены на рис.2

Рис. 2. Синхронные RS-триггеры.

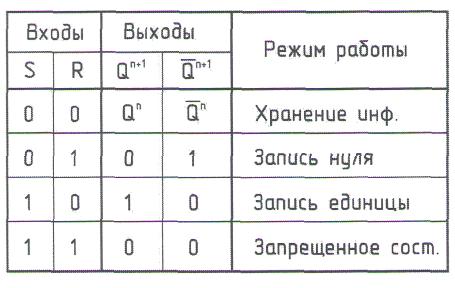

Триггерные ячейки - это основа делителей частоты, счетчиков и регистров. В этих устройствах записанную ранее информацию по специальному сигналу, называемому тактовым, следует передать на выход и переписать в следующую ячейку. Для осуществления такого режима в RS-триггер необходимо ввести дополнительный вход С, который может быть статическим или динамическим, т. е. получим синхронный RS -триггер.

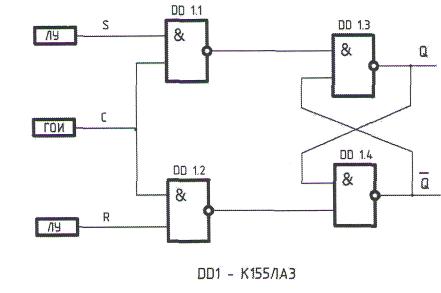

Схема синхронного RS-триггера на логических элементах И-НЕ со статическим управляющим входом и его условное обозначение приведена на рис. 3. Элементы DD1.1 и DD1.2 образуют схему управления, а элементы DD1.3 и DD1.4 - асинхронный RS-триггер. Триггер имеет прямой статический управляющий вход и прямые информационные входы, т. е. активным уровнем сигнала является уровень логической единицы.

Рис. 3

Если на вход С подать сигнал логической единицы (С = 1), то работа триггера аналогична работе простейшего асинхронного RS-триггера. При С = 0 информационные входы S и R не оказывают влияние на состояние триггера. Комбинация сигналов S = R = С = 1 является запрещенной. Табл. 2 отражает состояния такого триггера.

Рис. 4

1. Исследование функционирования асинхронного RS-триггера

1.1. Зарисуйте схему, показанную на рис. 4 . Проставьте на входах и выходах логических элементов номера выводов. Выберите ГОИ, которые Вы будете использовать и проставьте их номера на схемах.

1.2. Осуществите управление режимами работы триггеров. Фиксируйте моменты изменения состояния триггеров с помощью светодиодных индикаторов.

2. Исследование функционирования синхронного RS-триггера со статическим управляющим входом

2.1. Зарисуйте схему, показанную на рис. 5. Проставьте на входах и выходах логических элементов номера выводов. Выберите ГОИ и источники ЛУ, которые Вы будете использовать и проставьте их номера на схемах.

2.2. Соберите схему показанную на рис. 5. Определите какие управляющие импульсы (единичные или нулевые) требуются для записи информации в триггер и подключите вход С триггера к соответствующему выходу ГОИ.

2.3. Осуществите управление режимами работы триггера. Фиксируйте моменты изменения состояния триггера с помощью светодиодных индикаторов.

Рис. 5

Порядок выполнения

Исследование функционирования асинхронного RS-триггера.

Исследование функционирования синхронного RS-триггера со статическим управляющим входом.

Ответить на контрольные вопросы.

Содержание отчёта

-

Наименование работы и цель работы.

-

Исследуемые схемы.

-

Таблицы наблюдений.

-

Сравнение экспериментальных данных с результатами расчетов.

-

Выводы по работе.

Контрольные вопросы

-

Какое устройство называют триггером.

-

Типы триггеров.

-

Какие режимы работы триггеров.

-

Чем отличается синхронный RS-триггер от асинхронного?

-

УГО различных типов триггеров.

Лабораторное занятие №2

Исследование функциональных схем счетчиков

Цель работы: изучение функционирования двоично-десятичного счетчика.

Оборудование: универсальный стенд ЦС-02, микросхема ИЕ2.

Краткие теоретические сведения

Счетчиком называют устройство, предназначенное для подсчета числа импульсов, поданных на вход.

Основой любого счетчика является линейка из нескольких триггеров. Между триггерами могут быть введены дополнительные обратные связи, позволяющие получить любой коэффициент деления, а не только равный  . Например, счетчик, состоящий из четырех триггеров, может иметь максимальный коэффициент деления

. Например, счетчик, состоящий из четырех триггеров, может иметь максимальный коэффициент деления  . Чтобы получить коэффициент деления 10, необходимо ввести обратные связи. Необходимое число триггеров для получения заданного коэффициента деления определяется условием:

. Чтобы получить коэффициент деления 10, необходимо ввести обратные связи. Необходимое число триггеров для получения заданного коэффициента деления определяется условием:

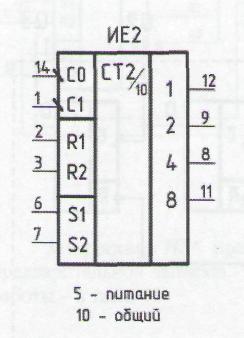

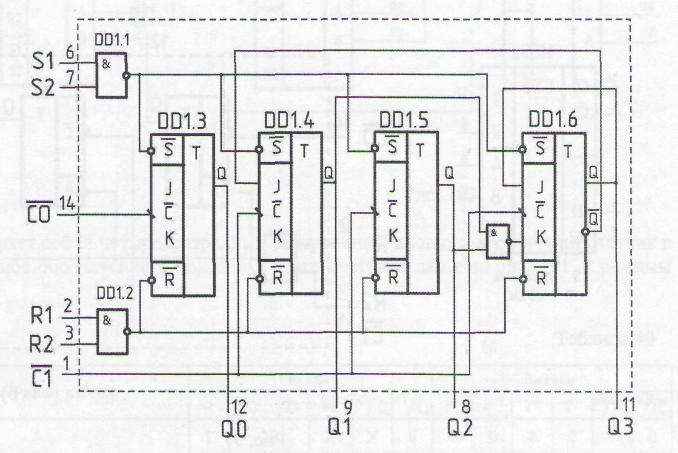

Микросхема ИЕ2 - это четырехразрядный двоично-десятичный счетчик. Его условное обозначение и цоколёвка приведены на рис. 1, а внутренняя структура на рис. 2. Счетчик состоит из четырех комбинированных триггеров типа JK. Первый триггер может работать самостоятельно и образует делитель входной последовательности импульсов с коэффициентом деления  = 2. Тактовый вход первого триггера

= 2. Тактовый вход первого триггера  (вывод 14) инверсный динамический, поэтому переключение триггера происходит отрицательным фронтом входного импульса. Выход Q0 первого триггера - вывод 12. Остальные три триггера образуют синхронный делитель на пять {

(вывод 14) инверсный динамический, поэтому переключение триггера происходит отрицательным фронтом входного импульса. Выход Q0 первого триггера - вывод 12. Остальные три триггера образуют синхронный делитель на пять { = 5). Тактовые входы

= 5). Тактовые входы  (вывод 1) инверсные динамические, управляются синхронно отрицательным фронтом входного импульса.

(вывод 1) инверсные динамические, управляются синхронно отрицательным фронтом входного импульса.

5 - питание

10 - общий

Рис.1. Условное обозначение и цоколёвка микросхемы ИЕ2

Рис.2. Внутренняя структура микросхемы ИЕ2

Счетчик имеет два входа R для синхронного сброса (обнуления), это выводы 2 и 3, а также два синхронных входа S предварительной установки двоичного кода (1001 = 9), выводы 6 и 7. Высокий уровень напряжения, поданный на входы R1 и R2, производит сброс данных по всем триггерам одновременно. Подача высокого уровня напряжения на входы S1 и S2 запрещает прохождение тактовых сигналов, а также сигналов от входов R1 и R2 на счетчик. На выходах устанавливается код 1001 = 9. Так как выход первого триггера внутренне не соединен с последующими тремя триггерами, то возможны три независимых режима работы микросхемы.

Для использования ИЕ2 как двоично-десятичного счетчика с весом двоичных разрядов 8-4-2-1 необходимо вывод 12 (выход первого триггера) соединить с выводом 1 (тактовым входом трех триггеров) внешней перемычкой. Входная последовательность импульсов подается на тактовый вход первого триггера (вывод 14). Режимы работы ИЕ2 можно проследить по табл. 1 - это сброс выходных данных в нуль, установка предварительного кода 1001 = 9 и счет.

При использовании счетчика как делителя на 2 и на 5 внешние перемычки не нужны. В перовом случае входная последовательность подается на тактовый вход первого триггера (вывод 14), а выходная снимается с выхода первого триггера (вывод 12). Во втором случае три последующих триггера образуют делитель на 5. Входная последовательность подается на синхронный тактовый вход трех триггеров (вывод 1), а выходная снимается с выхода третьего триггера (вывод 11). Оба делителя работают независимо.

Таблица 1

Входы

Выходы

Режим работы

R1

R2

S1

S2

C

8

4

2

1

1

1

0

0

0

0

0

Сброс в нуль

1

1

0

0

0

0

0

1

1

1

0

0

1

Предварительная установка кода 1001

0

0

Счёт

Счёт входных импульсов

0

0

0

0

0

0

Контрольные вопросы

-

Показать входы и выходы на Рис. 1. и Рис. 2.

-

Дать определение счетчика.

-

Что является основой счетчика?

Содержание отчета:

-

Номер, название и цель лабораторного занятия.

-

Условное обозначение и цоколёвка микросхемы ИЕ2

-

Схем внутренней структуры микросхемы ИЕ2.

-

Таблица режима работы ИЕ2.

-

Ответы на контрольные вопросы

-

Вывод.

Лабораторное занятие №3

Исследование функциональных схем регистров

Цель: исследование принципа построения регистров.

Оборудование: универсальный стенд ЦС-02, микросхема К155ТМ7.

Краткие теоретические сведения

Регистр - устройство, предназначенное для кратковременного хранения и преобразования многоразрядных двоичных чисел.

В качестве запоминающих элементов в регистрах используются триггеры, которые работают в режиме записи информации. Это JK-, D- и RS-триггеры.

Кроме триггеров в регистрах имеются вспомогательные элементы, которые обычно строятся на основе комбинационных схем. Вспомогательные элементы используются для осуществления следующих операций:

-

ввода и вывода из регистра хранимой информации;

-

преобразования кода числа, хранящегося в регистре;

-

сдвига числа влево или вправо на определенное число разрядов;

-

преобразования последовательного кода числа в параллельный и наоборот и другие.

Регистры классифицируют по различным признакам, основными из которых являются способ ввода информации в регистр и ее вывод и способ представления вводимой и выводимой информации По способу ввода и вывода информации регистры подразделяются на:

-

параллельные (регистры памяти);

-

последовательные (регистры сдвига);

-

параллельно-последовательные.

Вывод информации из регистров может осуществляться как в прямом, так и в обратном коде.

В простейшем последовательном (сдвиговом) регистре триггеры соединены последовательно, т. е. выходы предыдущего триггера передают информацию на входы последующего. Управляющие входы С триггеров соединены параллельно. Такой регистр имеет один информационный вход и один информационный выход.

Если ко входу каждого триггера добавить разрешающую логику, то можно осуществить параллельную загрузку данных в регистр. Можно предусмотреть логическую схему параллельного отображения выходных данных. Как правило, выходные элементы такой схемы имеют z-состояния, позволяющие поочередно выдавать информацию на многопроводную шину данных. В z-состоянии выходы регистра отключаются от схемы.

Последовательные регистры могут быть реверсивные, т. е. записанную информацию можно сдвигать по линейке триггеров вправо или влево. Для выбора режима работы регистра предусматривают специальные входы.

Существуют многорежимные регистры, у которых входные и выходные линии данных объединены в одну линию (порт - данных). Эта линия по соответствующей команде (т. е. имеется дополнительный вход управления) может быть и входной, и выходной.

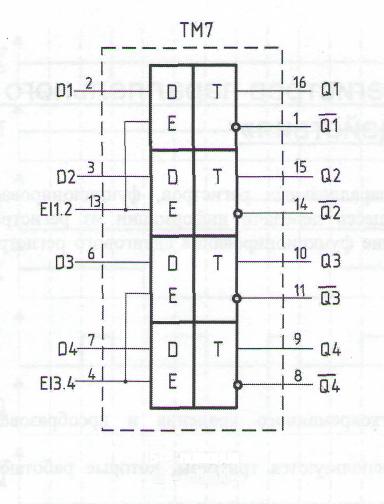

Микросхема ТМ7 содержит четыре D-триггера, статические входы синхронизации которых попарно соединены и обозначены как входы разрешения загрузки EI.

Если на такой вход разрешения EI подается напряжение высокого уровня, то информация, поступающая на входы D передается на выходы триггеров. В триггерах будет зафиксирована информация, имевшаяся на входах D, если состояние входа EI переключить от напряжения высокого уровня к низкому. При напряжении низкого уровня на входе разрешения EI на выходах триггеров сохраняется информация, записанная ранее и сигналы на входах D не влияют на состояние триггера (состояние входов D

безразличное). Каждый триггер микросхемы ТМ7 имеет прямые Q и инверсные Q выходы.

Такие триггеры используются в качестве четырехразрядного регистра хранения информации с попарным тактированием разрядов. Для использования микросхемы ТМ7 в качестве четырехразрядного буферного регистра все управляющие входы разрешения EI должны быть соединены.

Функциональная схема и цоколевка микросхемы ТМ7 приведены на рис. 1. Режимы работы триггеров даны в табл. 1.

5 - питание

12 - общий

Рис.1. Функциональная схема и цоколёвка микросхемы ТМ7

Таблица 1. Режим работы триггеров

Режим работы

Входы

Выходы

Разрешение передачи

данных на выход

D

El

1

1

1

0

Защелкивание данных

(хранение информации)

0

1

0

1

0

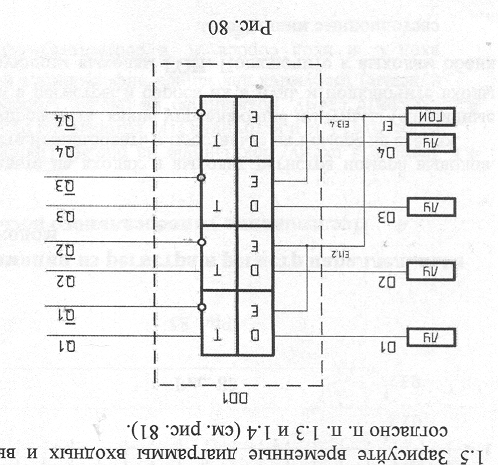

Рис.2. Схема подключения микросхемы ТМ7

Исследование принципа построения параллельных регистров

-

Зарисуйте схему, показанную на рис.2. Проставьте на входах и выходах микросхемы ТМ7 номера выводов. Выберите ГОИ и источники ЛУ, которые Вы будете использовать и проставьте их номера на схемах.

-

Соберите схему, показанную на этом рисунке. Определите, какие управляющие импульсы (единичные или нулевые) требуются для записи информации в регистр и подключите вход разрешения записи EI регистра к соответствующему выходу ГОИ. Подключите к выходам регистра светодиодные индикаторы.

Контрольные вопросы

-

Что такое регистр?

-

Какие вспомогательные элементы, помимо регистров, используются в триггерах и для чего?

-

На какие типы подразделяются регистры по способу ввода и вывода информации?

Содержание отчёта

-

Номер, название и цель лабораторного занятия.

-

Функциональная схема и цоколёвка микросхемы ТМ7.

-

Таблица режима работы триггеров.

-

Схема подключения микросхемы ТМ7.

-

Ответы на контрольные вопросы.

-

Вывод.

Лабораторное занятие №4

Исследование функциональных схем шифраторов и дешифраторов

Цель: исследование принципа построения шифраторов и дешифраторов.

Оборудование: универсальный стенд ЦС-02; микросхемы ИД3, 514ИД2.

Краткие теоретические сведения

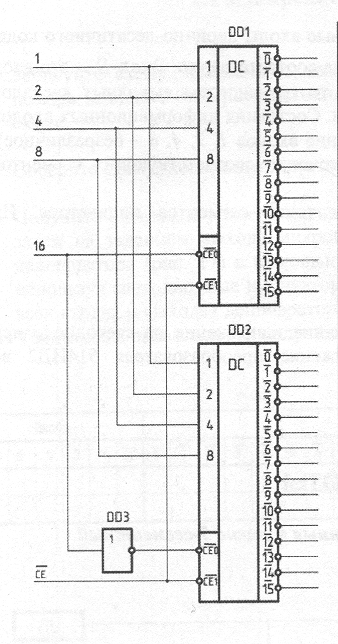

Дешифраторы предназначены для преобразования двоичного кода, поданного на его входы в активный уровень сигнала, появляющийся на том выходе, номер которого соответствует входному коду. Если активный уровень выходного сигнала дешифратора равен нулю, то в его условном обозначении на выходах рисуют кружки. Дешифраторы различаются по емкости (количество разрядов входного кода), по числу каналов (один или два), а также форматом входного кода ( двоичный или двоично-десятичный). Если двоичный дешифратор имеет n входов, то он может иметь не более 2n выходов. Многие дешифраторы можно применять как демультиплексоры (функциональный узел осуществляющий коммутацию информации с одного входа на один из нескольких выходов. Демультиплексоры в виде самостоятельной ИС не изготавливаются).

Микросхемы типа ИД представляют собой дешифраторы.

Микросхема ИД3 - это дешифратор-демультиплексор. Цоколевка и условное обозначение приведены на рис. 1. Состояния ИД3 приведены в табл. 1.

Рис. 1. Условное обозначение и цоколевка микросхемы ИД3

Эта микросхема позволяет преобразовать четырехразрядный двоичный код, поступивший на входы 1, 2, 4, 8, в напряжение низкого уровня, появляющееся на одном из шестнадцати выходов  . Вход 1 - это вход младшего разряда, а вход 8 - это вход старшего разряда двоичного кода. Кроме четырех информационных входов 1, 2, 4, 8 устройство имеет еще два входа

. Вход 1 - это вход младшего разряда, а вход 8 - это вход старшего разряда двоичного кода. Кроме четырех информационных входов 1, 2, 4, 8 устройство имеет еще два входа  разрешения дешифрации.

разрешения дешифрации.

Входы  играют роль стробирующих входов, если на них подан низкий уровень напряжения. Если хотя бы на одном из входов

играют роль стробирующих входов, если на них подан низкий уровень напряжения. Если хотя бы на одном из входов  установить высокий уровень, то на всех выходах

установить высокий уровень, то на всех выходах  будет высокий уровень напряжения независимо от того, какой код подан на входы 1, 2, 4, 8. Такой режим используется при наращивании числа разрядов дешифрируемого кода.

будет высокий уровень напряжения независимо от того, какой код подан на входы 1, 2, 4, 8. Такой режим используется при наращивании числа разрядов дешифрируемого кода.

На рис. 2 приведена схема дешифрации пятиразрядного кода на двух микросхемах ИД3. Инвертор DD3 в зависимости от сигнала на входе 16 схемы разрешает работать либо микросхеме DD1, либо микросхеме DD2. Для большего увеличения числа разрядов входного кода вместо инвертора DD3 можно применить дешифратор на требуемое количество входов и к каждому его выходу подключить вход  соответствующей микросхемы ИД3. Максимальное количество микросхем ИД3 в такой схеме будет равно числу выходов дешифратора, который выбирает нужную микросхему ИД3.

соответствующей микросхемы ИД3. Максимальное количество микросхем ИД3 в такой схеме будет равно числу выходов дешифратора, который выбирает нужную микросхему ИД3.

Входы  можно использовать как информационные, когда микросхема ИД3 служит демультиплексором данных. Входы 1, 2, 4, 8 в этом случае используются как адресные, чтобы направить поток данных, передаваемых со входа

можно использовать как информационные, когда микросхема ИД3 служит демультиплексором данных. Входы 1, 2, 4, 8 в этом случае используются как адресные, чтобы направить поток данных, передаваемых со входа  , на один из выходов

, на один из выходов  . На второй вход

. На второй вход  , неиспользуемый в этом включении, необходимо подать напряжение низкого уровня.

, неиспользуемый в этом включении, необходимо подать напряжение низкого уровня.

Рис.2. - Схема дешифрации пятиразрядного кода на двух микросхемах ИД3

Таблица 1 - Состояния ИД3

Входы

Выходы

8

4

2

1

1

1

×

×

×

×

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

×

×

×

×

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

×

×

×

×

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

1

0

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

1

0

0

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

0

0

0

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

0

0

0

1

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

0

0

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

0

0

1

0

0

0

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

0

0

1

0

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

0

0

1

0

1

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

0

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

0

0

1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

0

0

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

0

0

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

× - любое состояние

Микросхема 514ИД2 представляет собой преобразователь двоично-десятичного кода в семисегментный код.

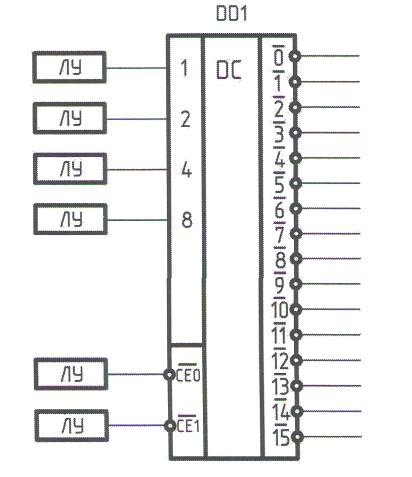

Она применяется для управления цифровыми полупроводниковыми индикаторами с общим анодом. Условное обозначение и цоколевка микросхемы 514ИД2 приведены на рис. 3, схема одного из выходов 514ИД2 - на рис. 3, схема подключения индикатора к этой микросхеме - на рис. 4 , а состояния - в табл. 2.

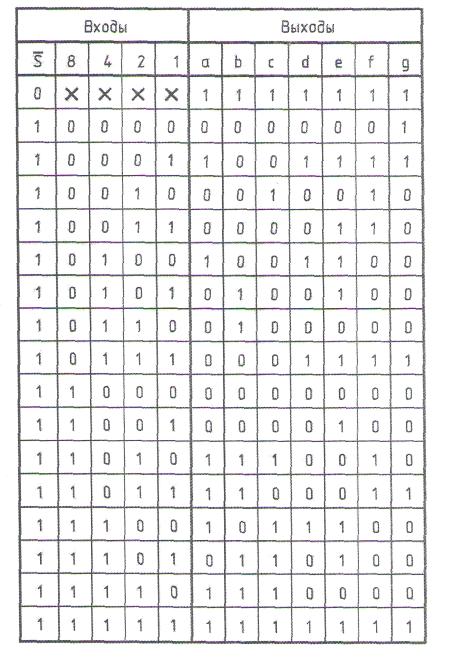

Таблица 2 - Состояния микросхемы 514ИД2

Рис.3. - Условное обозначение и цоколёвка микросхемы 514ИД2

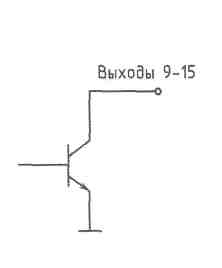

Рис.4. - Схема одного из выходов микросхемы 514ИД2

У преобразователя 514ИД2 входы 1, 2, 4, 8 - это информационные входы двоично-десятичного кода. Причем 1 - это вход младшего, а вход 8 - это вход старшего разряда соответственно. Вход  - это вход гашения. Если на этот вход подать низкий уровень напряжения, то транзисторы выходных каскадов преобразователя рис.3 закрываются и сегменты индикатора гасятся. Состояния информационных входов при этом на выходные сигналы преобразователя не влияют (состояние входов 1, 2, 4, 8 - безразличное). Выходы преобразователя а, b, с, d, e, f, g, h служат для подключения соответствующих сегментов индикатора.

- это вход гашения. Если на этот вход подать низкий уровень напряжения, то транзисторы выходных каскадов преобразователя рис.3 закрываются и сегменты индикатора гасятся. Состояния информационных входов при этом на выходные сигналы преобразователя не влияют (состояние входов 1, 2, 4, 8 - безразличное). Выходы преобразователя а, b, с, d, e, f, g, h служат для подключения соответствующих сегментов индикатора.

Резисторы R1 ... R7 на рис. 6 служат для ограничения токов сегментов индикатора. Их сопротивления могут быть определены из следующего соотношения:

,

,

где  - напряжение источника питания,

- напряжение источника питания,  - прямое падение напряжения на светодиоде при постоянном токе через сегмент

- прямое падение напряжения на светодиоде при постоянном токе через сегмент  ,

,  - выходное напряжение преобразователя 514ИД2 во включенном состоянии,

- выходное напряжение преобразователя 514ИД2 во включенном состоянии, , - прямой ток через светодиод.

, - прямой ток через светодиод.

Исследование работы четырехразрядного дешифратора ИД3

1. Зарисуйте схему, показанную на рис. 5. Проставьте на входах и выходах дешифратора номера выводов. Выберите источники ЛУ, которые Вы будете использовать и проставьте их номера на схеме.

Рис. 5. Схема подключения микросхемы 514ИД3

2. Соберите схему, показанную на этом рисунке.

3. Получите активный уровень сигнала на заданном преподавателем выходе дешифратора. Для этого проставьте необходимые сигналы на входах дешифратора в схеме (рис. 5) и установите их с помощью источников ЛУ. Определите состояние всех выходов дешифратора с помощью светодиодных индикаторов. Проставьте в схеме рис. 5 значения сигналов (1 или 0) на всех выходах дешифратора для заданного случая.

4. Убедитесь в правильности полученных результатов, сравнивая их с соответствующей строкой табл. 1.

Контрольные вопросы

-

Какие существуют дешифраторы по способу построения?

-

Что обозначают цифры 1,2,4,8 на входах шифратора?

-

Что представляет микросхема ИД3, где она применяется?

-

Что представляет микросхема 514ИД2, где она применяется?

Содержание отчёта

-

Номер, название и цель лабораторного занятия.

-

Функциональная схема и цоколевка микросхемы ИД3.

-

Состояния ИД3.

-

Условное обозначение и цоколёвка микросхемы 514ИД2.

-

Схема подключения микросхемы 514ИД2.

-

Сравнение экспериментальных данных с результатами теоретического анализа.

-

Ответы на контрольные вопросы.

-

Вывод.

Лабораторное занятие №5

Исследование функциональных схем мультиплексоров и демультиплексоров

Цель: исследование функционирования мультиплексора и демультиплексора.

Оборудование: универсальный стенд ЦС-02, микросхема К155КП7.

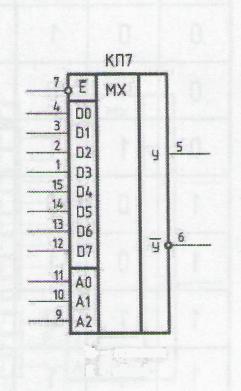

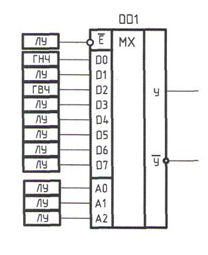

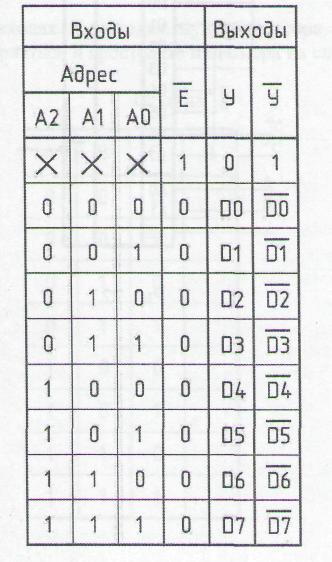

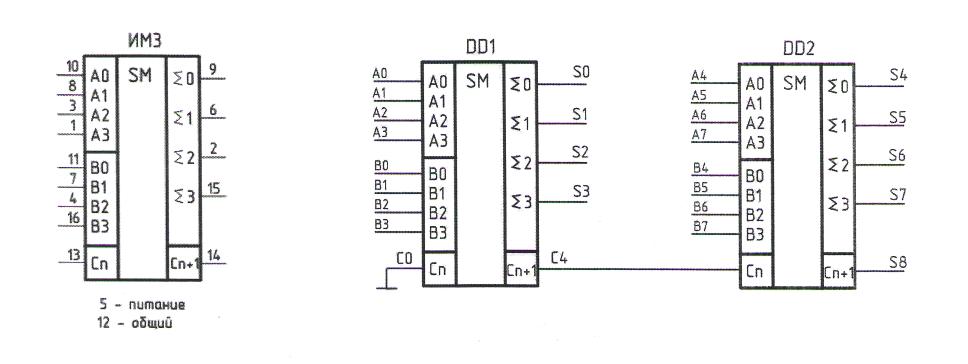

Краткие теоретические сведения