- Преподавателю

- Информатика

- Конспект на тему Запоминающие устройства

Конспект на тему Запоминающие устройства

| Раздел | Информатика |

| Класс | 12 класс |

| Тип | Конспекты |

| Автор | Сиразетдинова Э.Р. |

| Дата | 10.02.2016 |

| Формат | doc |

| Изображения | Есть |

Запоминающие устройства

izlov.ru/docs/100/index-12956.html#94067

19.1 Статические ОЗУ

19.1.2 Структурная схема ОЗУ с одномерной адресацией

19.1.3 Структурная схема ОЗУ с двумерной адресацией

19.1.4 Временные диаграммы работы ОЗУ

19.2 Динамические ОЗУ

19.2.2 Обобщенная структура динамического ОЗУ

19.2.3 Временные диаграммы динамического ОЗУ

19.3 Постоянные ЗУ

19.3.1 Однократно программируемые ПЗУ

19.3.2 Программируемые ПЗУ

19.3.3 Репрограммируемые ПЗУ

19.3.4 Обобщенная структурная схема ПЗУ

19.3.5 Обобщенные временные диаграммы работы ПЗУ

19.6 Построение памяти заданной структуры.

Запоминающие устройства (ЗУ) предназначены для хранения информации и обмена ею с другими частями ЭВМ или компьютерных систем.

По функциональному назначению ЗУ подразделяют на внешние, буферные и внутренние.

Внешние ЗУ служат для хранения больших объемов информации и программного обеспечения (магнитные барабаны, магнитные диски, лазерные диски и т.д.).

Буферные ЗУ предназначены для промежуточного хранения данных при обмене между внешней и внутренней памятью.

Внутренние ЗУ, являются неотъемлемой частью ЭВМ и непосредственно управляют ею.

В ЭВМ нового поколения во внутренних ЗУ используются полупроводниковые интегральные микросхемы, которые по сравнению с традиционными магнитными ЗУ имеют заметные преимущества: высокая информационная емкость, низкая стоимость, совместимость по уровням сигналов с процессором ЭВМ, высокая надежность.

В полупроводниковых ЗУ накопителем информации служит запоминающий элемент памяти (ЗЭ).

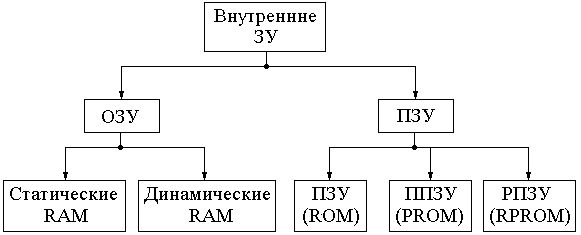

Внутренние ЗУ по выполняемым функциям делят на оперативные и постоянные.

Рисунок 19.1 - Запоминающие устройства

ОЗУ выполняет запись, считывание и хранение произвольной двоичной информации, обеспечивающей хранение программ для текущей обработки информации и массивов обрабатываемых данных.

По способу хранения информации ОЗУ делят на статические и динамические.

В статических ОЗУ запоминающий элемент представляет собой бистабильный элемент (обычно триггер), поэтому обеспечивается считывание информации без ее разрушения.

В динамических ОЗУ для хранения информации используются инерционные свойства реактивных элементов (обычно заряд и разряд конденсатора), что требует периодического восстановления (регенерации) состояния запоминающих элементов при хранении и считывании.

ПЗУ осуществляет хранение и выдачу постоянной записываемой информации, содержание которой не изменяется во время работы системы. Это используемые в процессе работы стандартные подпрограммы и микропрограммы, табличные значения различных функций и констант.

ПЗУ делят по способу занесения информации:

- ПЗУ, программируемое заводом-изготовителем (ROM);

- ПЗУ, программируемые пользователем однократно (PROM);

- репрограммируемые ПЗУ (RPROM).

По способу обращения ЗУ подразделяют на адресные и ассоциативные.

В адресных ЗУ обращение к запоминающему элементу производится по его физическим координатам, задаваемым внешним двоичным кодом адреса. Адресные ЗУ бывают с произвольной выборкой, которые допускают любой порядок следования адресов и с последовательным обращением, в котором выборка запоминающих элементов возможна только в порядке возрастания или убывания адреса. В ЗУ с последовательным обращением информация считывается в том же порядке, в котором она была записана (стек), или в обратном порядке (магазин).

В ассоциативных ЗУ поиск информации производится по признакам, заключающимся в самой хранимой информации, независимо от физических координат ЗУ.

19.1 Статические ОЗУ

19.1.1 Запоминающие элементы статических ОЗУ

Запоминающий элемент представляет собой бистабильный элемент и при считывании информация не разрушается.

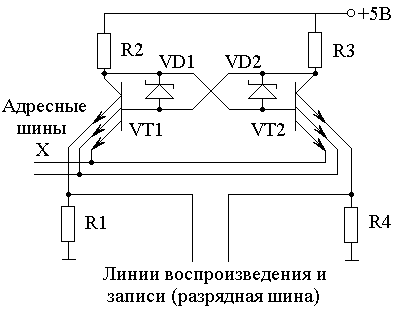

На рисунке 19.2 представлена схема запоминающего элемента на биполярных транзисторах.

Разрядная шина предназначена для считывания состояния триггера и для записи в него новой информации. Если на одну или обе адресные шины подано низкое напряжение (уровень логического '0'), то триггер будет находиться в устойчивом состоянии и ток открытого транзистора замыкается на землю через эмиттеры, подключенные к адресным шинам.

Если напряжение на адресных шинах повысить до уровня логической '1', то эмиттеры, подключенные к разрядной шине, будут управлять током транзисторов.

Рисунок 19.2 - Схема запоминающего элемента на биполярных транзисторах

Предположим, что на адресные шины подан уровень логической '1' и необходимо считать состояние триггера. Если транзистор VT1 открыт, то ток пойдет через левый резистор (R1). В это время транзистор VT2 будет закрыт и, таким образом, через резистор R4 ток совсем не будет идти. Это означает, что напряжение на резисторе R1 будет больше, чем напряжение на резисторе R2.

Из изложенного следует, что состояние триггера можно определить, измеряя напряжение на резисторах R1 и R2. Это обычно выполняется схемой усилителя, называемого усилителем считывания.

Используя линии разряда, можно также записывать информацию в ячейку. Предположим, что на адресных шинах логическая '1', и установим напряжение на R1 выше, чем на R4. Тогда транзистор VT2 откроется и закроет транзистор VT1.

Как можно заметить, одни и те же две разрядные шины используются и для считывания состояния триггера и для установки заданного значения в выбранную ячейку.

ЗЭ строят и на основе МОП - структур. На их базе создают ЗУ большой и сверхбольшой емкости.

Основной недостаток ЗЭ на МОП - транзисторах - потребление тока в режиме хранения, так как один из ключевых транзисторов в триггере находится в открытом состоянии. Для уменьшения потребляемой мощности необходимо увеличить сопротивление нагрузки, но это приводит к снижению быстродействия. Поэтому используют схемы на КМОП - транзисторах, где ток в режиме хранения почти отсутствует, а потребляется только в момент переключения.

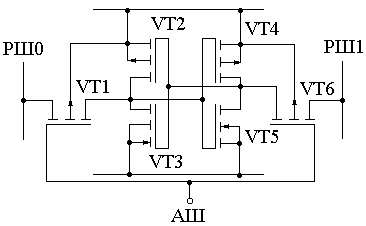

Схема ЗЭ на КМОП-транзисторах приведена на рисунке 19.3.

Рисунок 19.3 - Схема ЗЭ на КМОП-транзисторах

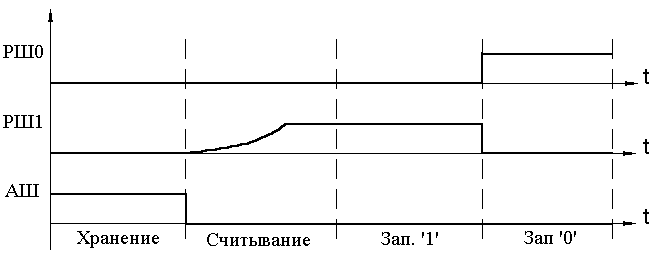

В состав ЗЭ входит триггер на КМОП - транзисторах и два двунаправленных ключа. В режиме хранения VT1 и VT6 закрыты. Перед считыванием на разрядной шине нуля (РШ0) и разрядной шины единицы (РШ1) устанавливается нулевой потенциал. Затем потенциал на адресной шине (АШ) снижается до нуля, открываются ключи VT1 и VT6. При хранении '1' начинается заряд паразитной емкости РШ1. После увеличения напряжения на РШ1 до порога срабатывания усилителя считывания, подключенного к этой шине, информация с усилителя поступает на последующие каскады схемы вывода данных. Записывается информация в ЗЭ при открытых VT1 и VT6 и разноименных уровнях напряжений на РШ0 и РШ1.

Временные диаграммы работы ЗЭ на КМОП-транзисторах показаны на рисунке 19.4.

Рисунок 19.4 - Временные диаграммы работы ЗЭ на КМДП-транзисторах.

19.1.2 Структурная схема ОЗУ с одномерной адресацией

На основе ЗЭ строят ОЗУ большой емкости. Рассмотрим обобщенные структурные схемы ОЗУ, наиболее часто применяемые в микросхемах, выпускаемых промышленностью.

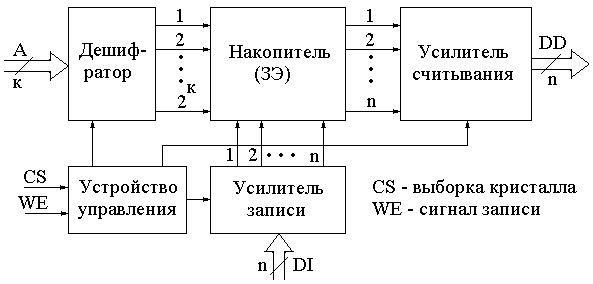

Структурная схема ОЗУ с одномерной адресацией приведена на рисунке 19.5.

Рисунок 19.5 - Структурная схема ОЗУ с одномерной адресацией

Достоинства - простота базовой ячейки на ЗЭ и минимальное число шин управления, необходимых для реализации накопителя, высокое быстродействие.

Недостатки - значительное усложнение дешифратора с увеличением объема накопителя, а также значительное число внутренних связей и внешних выводов накопителя, по которым передаются данные.

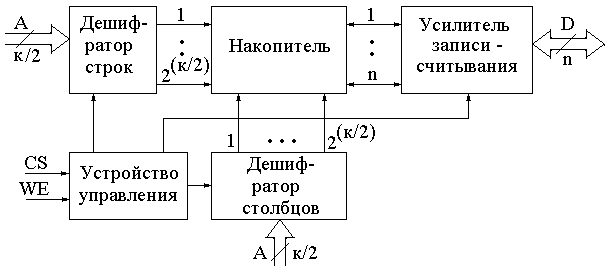

19.1.3 Структурная схема ОЗУ с двумерной адресацией

Структурная схема ОЗУ с двумерной адресацией приведена на рисунке 19.5.

Выборка ЗЭ происходит по принципу совпадения сигналов возбуждения соответствующих шин по двум координатам.

Преимущества - упрощена схема дешифраторов (так, например, при n=10 в схеме с одномерной адресацией необходимо 210=1024 десятивходовых элементов, а в схеме с двумерной адресацией 2+25=64 пятивходовых элементов).

Н едостатки - более сложная конструкция ЗЭ и меньшее быстродействие из-за усложнения усилителя записи-считывания и устройства управления.

едостатки - более сложная конструкция ЗЭ и меньшее быстродействие из-за усложнения усилителя записи-считывания и устройства управления.

Рисунок 19.6 - Структурная схема ОЗУ с двумерной адресацией.

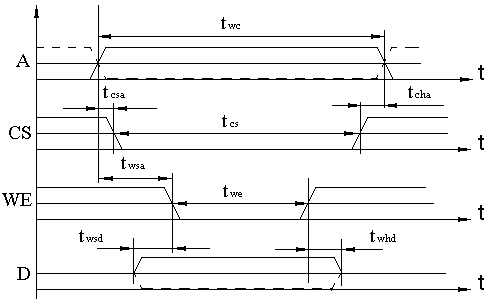

19.1.4 Временные диаграммы работы ОЗУ

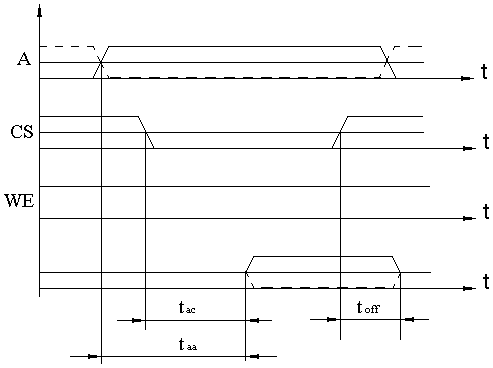

Работой ОЗУ управляют внешними сигналами. Обобщенные временные диаграммы приведены на рисунках 19.7 и 19.8

Рисунок 19.7 - Временные диаграммы работы ОЗУ в режиме записи

Основные временные параметры:

twc, tcs, twе - длительности сигналов адреса, выборки кристалла, записи;

tcsa - время сдвига сигнала CS относительно адреса;

tcha - время сохранения адреса относительно сигнала CS;

twsa - время сдвига сигнала WE относительно адреса;

twsd - время сдвига сигнала WE относительно данных;

twsh - время сдвига сигнала данных относительно сигнала записи.

Рисунок 19.8 - Временные диаграммы работы ОЗУ в режиме считывании.

Рисунок 19.8 - Временные диаграммы работы ОЗУ в режиме считывании.

Основные временные параметры

tac - время выборки разрешения сигнала CS

taa - время выборки адреса;

toff - время восстановления.

Основной параметр ОЗУ - время цикла записи, которое определяют как минимально допустимое время между моментом подачи сигнала выборки при записи и моментом начала последующей операции считывания (записи) (время между передними фронтами CS).

Достоинства статических ОЗУ - очень просты в эксплуатации, обладают высокой помехоустойчивостью, не требуют дорогих и сложных схем обслуживания, благодаря чему достигается умеренная стоимость всей системы памяти.

Недостаток - малая информационная стоимость (например, одна из лучших современных микросхем КР537РУ10 имеет информационную емкость 16к).

19.2 Динамические ОЗУ

19.2.1 Запоминающий элемент динамических ОЗУ

Разработка микросхем памяти сверхбольшой емкости требует изменения подхода к их структуре. Для увеличения информационной емкости микросхем необходимо уменьшение числа элементов в ЗЭ и площади, занимаемой ими. Это достигается при использовании динамических запоминающих элементов, в которых информация хранится в виде заряда соответствующих емкостей. Управление зарядом конденсатора и его разрядом осуществляется полевым транзистором. Сопротивление закрытого МОП - транзистора составляет  -

-  Ом и входное сопротивление затвора превышает

Ом и входное сопротивление затвора превышает  Ом, поэтому заряд на емкости конденсатора может сохраняться доли секунд. Наличие утечки в структуре требует восстановления заряда (регенерации).

Ом, поэтому заряд на емкости конденсатора может сохраняться доли секунд. Наличие утечки в структуре требует восстановления заряда (регенерации).

Известны различные модификации ЗЭ динамических ОЗУ, отличающихся количеством транзисторов, числом и функциональным назначением общих шин, быстродействием, мощностью потребления и площадью, занимаемой на кристалле.

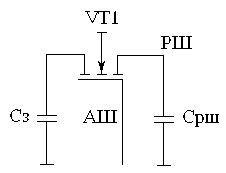

Рассмотрим ЗЭ, применяемый для создания динамических ЗУ большой емкости.

Схема приведена на рисунке 19.9

Рисунок 19.9 - Запоминающий элемент для создания динамических ЗУ

Рисунок 19.9 - Запоминающий элемент для создания динамических ЗУ

Запоминание '1' или '0' осуществляется с наличием или отсутствием заряда на емкости Сз. Информация в ЗЭ заносится при передаче соответствующего потенциала разрядной шиной РШ через открытый транзистор VT1 конденсатору Сз. В моменте считывания конденсатор Сз подключается через открытый транзистор VT1 к РШ, имеющей паразитную емкость Срш, и заряженной до уровня Uрш'0'. Если в ЗЭ хранилась '1', то напряжение на РШ при считывании увеличивается на величину  . При считывании '0' напряжение на РШ уменьшается на величину

. При считывании '0' напряжение на РШ уменьшается на величину  . Обычно

. Обычно ![]()

200...250 мВ, поэтому требуются высокочувствительные усилители считывания.

200...250 мВ, поэтому требуются высокочувствительные усилители считывания.

Недостатком такого ЗЭ является то, что при считывании информации происходит ее разрушение, поэтому регенерация необходима как для длительного хранения информации, так и после каждого ее считывания.

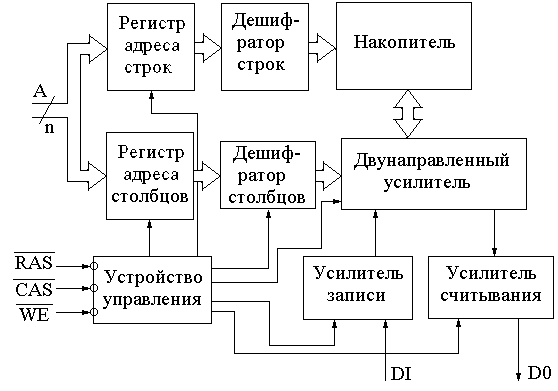

19.2.2 Обобщенная структура динамического ОЗУ

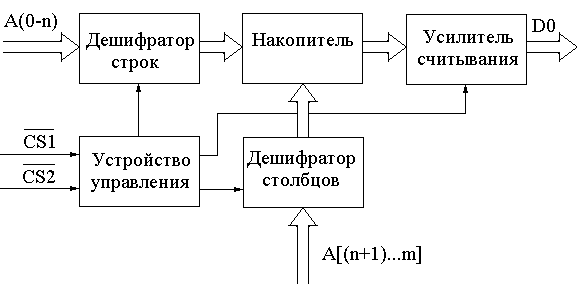

Рассмотрим обобщенную структуру динамического ОЗУ, приведенную на рисунке 19.10..

Рисунок 19.10 - Обобщённая структурная схема динамического ОЗУ.

Рисунок 19.10 - Обобщённая структурная схема динамического ОЗУ.

В динамических ОЗУ из-за достаточно жестких ограничений по числу выводов практикуется передача адресной информации по частям (обычно в начале адреса строк, а затем адреса столбцов).

Как видно из рисунка 19.10 адреса строк и столбцов подаются по одним и тем же выводам микросхемы в два приема.

Режимы работы задаются комбинацией сигналов  ,

,  и

и  .

.

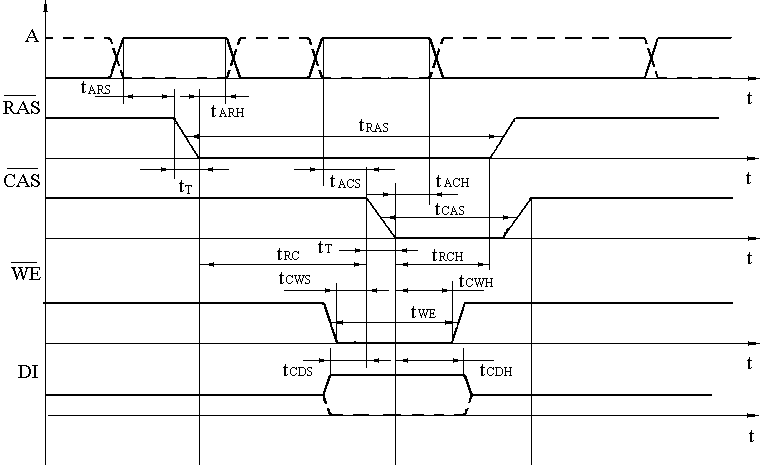

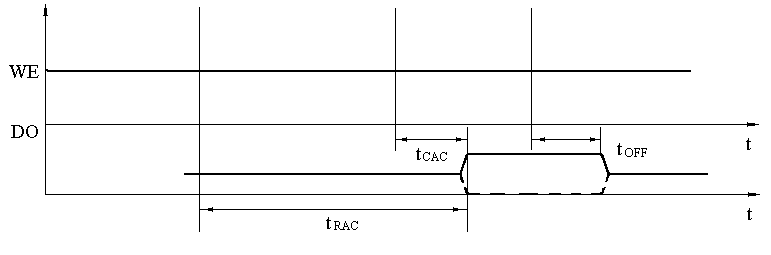

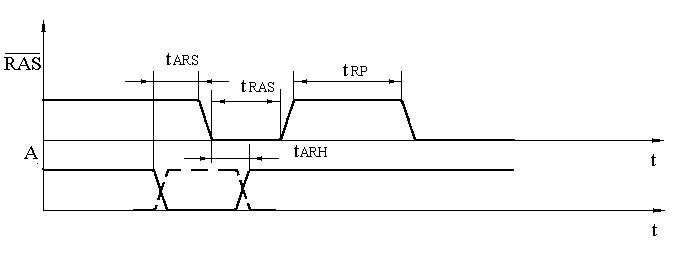

19.2.3 Временные диаграммы динамического ОЗУ

Временные диаграммы динамического ОЗУ в режимах записи, считывания и регенерации приведены на рисунках 19.11, 19.12 и 19.13 соответственно.

Поступление по шине А адреса строки фиксируется в регистре адреса строк (по отрицательному фронту сигнала RAS), это следует из анализа временных диаграмм и работы ОЗУ.

Рисунок 19.11 - Временные диаграммы работы динамических ОЗУ в режиме записи

Р исунок 19.12 - Временные диаграммы работы динамических ОЗУ в режиме считывания

исунок 19.12 - Временные диаграммы работы динамических ОЗУ в режиме считывания

Д ля обращения к ЗЭ с целью записи или считывания необходимо после адресации строки сформировать на шине А адрес столбца. Этот код по сигналу CAS=0 с помощью дешифратора столбцов обеспечит выбор одного из N двунаправленных усилителей. При этом режим работы ОЗУ определяется уровнем сигнала WE, который присутствует к моменту формирования сигнала CAS=0. Если WE=1, то будет иметь место считывание информации из адресованного ЗЭ с передачей через выходной буферный усилитель на выход D0. При WE=0 будет произведена запись информации, присутствующей на входе DI.

ля обращения к ЗЭ с целью записи или считывания необходимо после адресации строки сформировать на шине А адрес столбца. Этот код по сигналу CAS=0 с помощью дешифратора столбцов обеспечит выбор одного из N двунаправленных усилителей. При этом режим работы ОЗУ определяется уровнем сигнала WE, который присутствует к моменту формирования сигнала CAS=0. Если WE=1, то будет иметь место считывание информации из адресованного ЗЭ с передачей через выходной буферный усилитель на выход D0. При WE=0 будет произведена запись информации, присутствующей на входе DI.

Рисунок 19.13 - Временные диаграммы работы динамических ОЗУ в режиме регенерации.

Регенерация производится по сигналу RAS=0. В этом случае информация из всех ЗЭ адресованной строки передаётся в N двунаправленных усилителей с последующей записью информации в те же ЗЭ. Таким образом, формируя на адресной шине последовательность адресов строк и передавая в ЗУ эти адреса с помощью сигнала RAS=0, можно за N тактов обеспечить полную регенерацию. Это время не должно превышать 2 мс.

К достоинство динамических ОЗУ следует отнести максимальную информационную ёмкость; простоту накопителя; меньшую потребляемую мощность, поскольку динамический ЗЭ не потребляет тока.

К недостаткам динамических ОЗУ следует отнести необходимость применения сложных схем управления и схем, обеспечивающих регенерацию информации.

19.3 Постоянные ЗУ

Постоянные ЗУ предназначены для хранения и выдачи постоянно записанной информации, содержимое которой не меняется во время работы цифрового устройства.

Запоминающие элементы ПЗУ определяют способ занесения информации.

19.3.1 Однократно программируемые ПЗУ

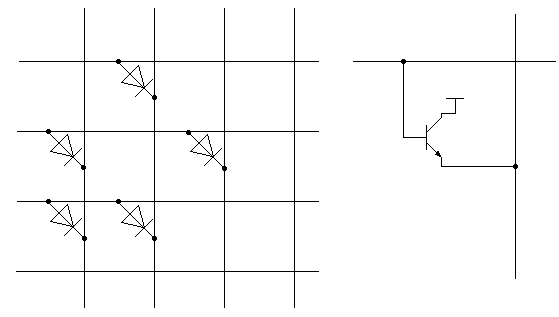

N включены ЗЭ несущие информацию о "1" или "0". В качестве ЗЭ используют диоды, биполярные транзисторы, МОП-структуры, аморфные полупроводники и др.N, образованную при пересечении N входных разрядов и n выходных (разрядов) информационных шин. В местах пересечения шин nВ ПЗУ, которые применяют при крупномасштабном производстве, информация заносится в процессе их изготовления. Обычно ЗЭ объединяются в двухкоординатную матрицу n.

Обычно в ПЗУ на кристалле полупроводника в начале создаются все ЗЭ, а затем на заключительных технологических операциях с помощью индивидуальных для конкретных заказчиков фотошаблонов формируется требуемая сеть соединений, определяющая записываемую информацию. При достаточно большой серийности такие ПЗУ оказываются более дешёвыми по сравнению с другими разновидностями ПЗУ. Их достоинством является также более простая структура и, как следствие этого, более высокая надёжность (такой тип микросхем обозначают РЕ).

Рисунок 19.14 - Запоминающие элементы однократно программируемых ПЗУ.

19.3.2 Программируемые ПЗУ

На этапах изготовления образцов изделий, также в условиях мелкосерийного производства изделий ВТ широко применяются программируемые ПЗУ (тип микросхем РТ), программирование которых осуществляется пользователем. В качестве ЗЭ используют те же элементы, что и ПЗУ. Программирование ППЗУ осуществляют пережиганием плавких перемычек, путём избирательного разрушения диодов или закорачивания одного из взаимно (обратно) включённых диодов, пробоем диодов и переходов транзисторов.

По сравнению с ПЗУ они имеют следующие недостатки:

- характеризуются более сложной структурой, во-первых, в связи с необходимостью введения в каждый ЗЭ элементов, разрушаемых в процессе программирования, во-вторых, из-за дополнительных элементов, через которые осуществляют программирование;

- необходимы дополнительные затраты, связанные с процессом программирования, которое осуществляется в определённых режимах с помощью специальных программаторов;

- необходимость выполнения специальных циклов термотренировки для устранения возможности восстановления некоторых перемычек (элементов) после программирования.

С целью сокращения необходимого числа выводов корпусов для программирования используются те же выводы, по которым считывается информация из ППЗУ.

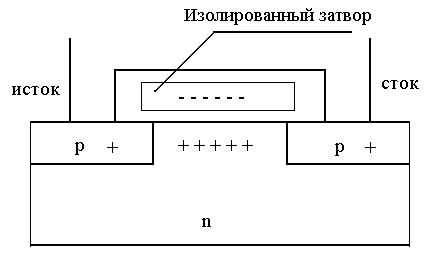

19.3.3 Репрограммируемые ПЗУ

Для многих применений, как в условиях массового производства, так и мелкосерийного очень удобными являются репрограммируемые ПЗУ, допускающие выполнения многих циклов перепрограммирования с предшествующим стиранием ненужной информации (число циклов репрограммирования у различных типов РПЗУ колеблется от десятков до десятков тысяч).

З Э таких РПЗУ имеют различные принцип действия и конструкцию. Наиболее широкое распространение получили лавинно-инжекционные МОП-транзисторы (ЛИИЗМОП-транзисторы) с изолированным затвором. Конструкция такого транзистора показана на рисунке 19.15.

Э таких РПЗУ имеют различные принцип действия и конструкцию. Наиболее широкое распространение получили лавинно-инжекционные МОП-транзисторы (ЛИИЗМОП-транзисторы) с изолированным затвором. Конструкция такого транзистора показана на рисунке 19.15.

Рисунок 19.15 - Конструкция лавинно-инжекционные МОП-транзистора с изолированным затвором.

Транзистор может находиться в одном из двух устойчивых состояний. Свойства такого транзистора в значительной степени определяются изолированным затвором, который со всех сторон окружён окислом и не имеет электрического контакта с другими элементами схемы.

Информация (заряд затвора) в ЗЭ заносится с помощью отрицательного напряжения, которое прикладывается между стоком и истоком транзистора. Это вызывает лавинную инжекцию электронов и изолированный затвор и на нем накапливается отрицательный заряд, который вызывает появление проводящего инверсного слоя в транзисторе. В результате этого канал становится проводящим, транзистор открыт (хранит логический '0'). Поскольку изолированный затвор окружен изолятором, то заряд сохраняется в течение длительного времени (5…50 лет). Стереть информацию можно посредством ультрафиолетового облучения с энергией, достаточной для «выбивания» электронов из поликристаллического кремния изолированного затвора в направлении двуокиси кремния, или электрическим сигналом требуемой полярности.. При этом транзистор переходит в состояние логической '1'.

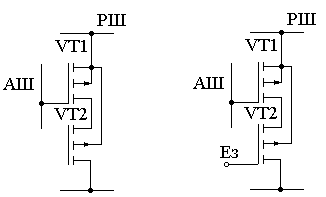

З Э состоит из адресного транзистора VT1 и собственно запоминающего транзистора VT2 типа ЛИИЗМОП с изолированным затвором (рисунок 19.16а).

Э состоит из адресного транзистора VT1 и собственно запоминающего транзистора VT2 типа ЛИИЗМОП с изолированным затвором (рисунок 19.16а).

Рисунок 19.16 - Запоминающие элементы на ЛИИЗМОП транзисторах:

а) с ультрафиолетовым стиранием, б) с электрическим стиранием

ЗЭ на ЛИИЗМОП-транзисторе и стиранием информации электрическим путем показан на рисунке 19.16б. Запоминающий транзистор VT2 содержит управляющий электрод, который применяют для записи и стирания информации. При хранении информации этот электрод не используется.

К недостаткам репрограммируемых ПЗУ следует отнести сложную структуру ЗЭ, необходимость введения элементов программирования, а также более высокую стоимость по сравнению с другими разновидностями ПЗУ. Поэтому они применяются в первую очередь там, где свойство перепрограммируемости являются определяющим.

19.3.4 Обобщенная структурная схема ПЗУ

Обобщенная структурная схема приведена на рисунке 19.17. На схеме показаны два управляющих сигнала CS. Выбор микросхемы задается одновременной подачей разрешающих значений обоих из них. Использование таких сигналов упрощает объединение микросхем при построении памяти заданной емкости и разрядности.

Рисунок 19.17 - Обобщённая структурная схема ПЗУ

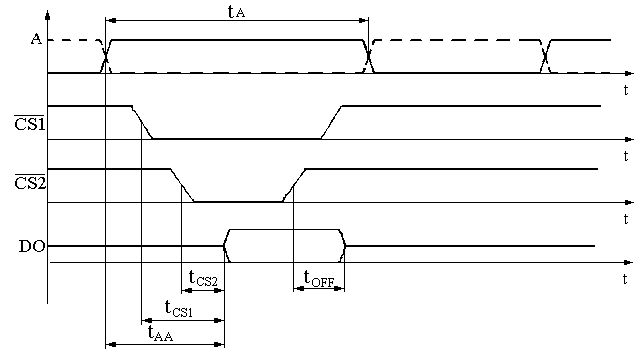

19.3.5 Обобщенные временные диаграммы работы ПЗУ

Обобщенные временные диаграммы работы ПЗУ приведены на рисунке 19.18. Для считывания информации необходимо подать адрес ЗЭ и сигналы выбора микросхемы.

Обобщенные временные диаграммы работы ПЗУ приведены на рисунке 19.18. Для считывания информации необходимо подать адрес ЗЭ и сигналы выбора микросхемы.

Рисунок 19.18 - Обобщённые временные диаграммы работы ПЗУ

Основными временными параметрами являются:

tA - длительность сигнала адреса;

tAA - время выборки адреса;

tCS1- время выборки разрешения по входу CS1;

tCS2 - время выборки разрешения по входу CS2;

tOFF - время восстановления.

19.6 Построение памяти заданной структуры.

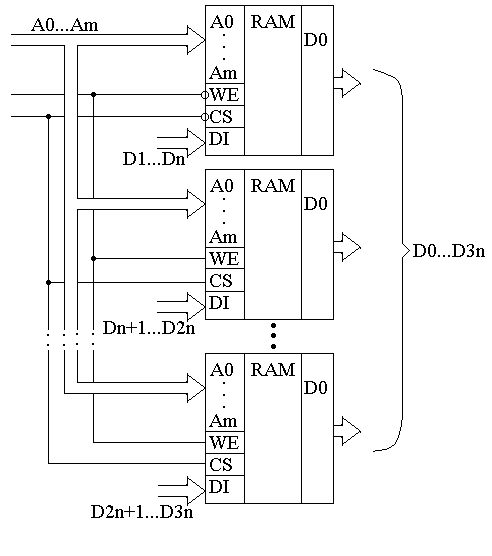

Отдельные микросхемы запоминающих устройств объединяют между собой в составе памяти микропроцессорных систем. Часть микросхем образует ОЗУ, другая функционирует в памяти на основе ПЗУ, ППЗУ, РПЗУ. Соотношение между этими составными частями зависит от конкретной конфигурации микропроцессорной системы. При этом может потребоваться применение однотипных микросхем для увеличения разрядности чисел. В этом случае на адресные шины всех микросхем параллельно подают группы кодов адресов этой части микросхем, а на входы управления также параллельно подают требуемые сигналы управления. Информационные входы и выходы объединяют в соответствующие информационные шины, причем разрядности объединяемых микросхем суммируются (рисунок 19.19).

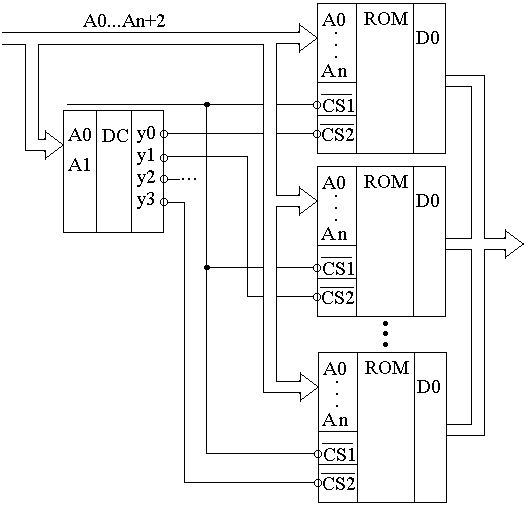

Очень часто возникает необходимость объединения микросхем ЗУ с целью увеличения общей емкости хранимых чисел. Соответствующие разряды информационных шин при таком объединении включают параллельно. Разряды шин адреса должны быть подключены так, чтобы одна группа кодов адресов соответствовала ячейкам памяти одной микросхемы, другая - ячейкам памяти следующей микросхемы и т.д. С этой целью старшие разряды адреса с помощью дешифратора можно использовать для управления поочередным выбором отдельных микросхем .

На практике реализация памяти заданной структуры зачастую требует комбинации объединения микросхем с целью увеличения, как разрядности, так и емкости хранимых слов (рисунок 19.20).

‹--Рисунок 19.19 - Применение микросхем для увеличения разрядности чисел

‹--Рисунок 19.19 - Применение микросхем для увеличения разрядности чисел

Р исунок 19.20 - Применение микросхем для увеличения общей ёмкости

исунок 19.20 - Применение микросхем для увеличения общей ёмкости

хранимых чисел.--›

22