- Преподавателю

- Информатика

- Конспект лекций: Архитектура аппаратных средств

Конспект лекций: Архитектура аппаратных средств

| Раздел | Информатика |

| Класс | - |

| Тип | Конспекты |

| Автор | Барсукова Т.И. |

| Дата | 30.12.2015 |

| Формат | doc |

| Изображения | Есть |

Конспект лекций

Архитектура аппаратных средств

Разработал преподаватель

Барсукова Татьяна Ивановна

Вычислительные устройства и приборы, история вопроса

История ВТ отсчитывается с опубликования работы Джона фон Неймана. Впервые

возможность построения цифровой ВМ была доказана английским математиком Тьюрингом

в 1936 году. Он показал, что любой алгоритм реализуется с помощью его дискретного

автомата, который был назван машиной Тьюринга. Независимо это же доказал Пост (машина

Поста).

Физически первая цифровая ВМ была сконструирована в 1935 году фирмой Белл (США).

Такого же вида машина была сконструирована для специальных задач под руководством К.

Цунзе (1941, Германия). Попытка построения универсальной ЭВМ была предпринята

Айтнетом (США). Она получила название "Марк-1". Спроектирована и изготовлена в

Гарвардском университете.

Характеристики ВМ (работали с 23 разрядными десятичными цифрами):

1. Программа вводилась покамандно с перфоленты.

2. Сложение 2-х чисел 0.3 секунды

3. Умножение 2-х чисел 6 секунд

4. Деление 2-х чисел 11 секунд.

Релейная основа была ненадежна. Для ЭВМ были разработаны специальные реле. На

которых была разработана ВМ "Марк-2".

Реальный отсчет ВТ ведется с перехода от реле к триггерам. Триггер был изобретен в 1918

году в России Бонч-бруевичем.

Первая ЭВМ, разработанная на электронных компонентах, изготовлена в 1942 году

("Эниак"). Серийный выпуск в 1945-1946 годах. Разработана в Пенсельванском университете

под руководством Маушли и Энкера. В 1943 году под руководством Тьюринга была

разработана ЭВМ "Колос". После рассекречивания архивов в 70-х годах оказалось, что

первая ЭВМ была разработана в 1939 году выходцем из Германии Антоносовым, которая

получила название "ABC".

Первое поколение ЭВМ.

Ламповые ЭВМ, промышленный выпуск начат в начале 50-х годов.

- 3 -

В нашей стране началом выпуска можно считать начало 50-х годов "МЭСМ". Разработана

под руководством Лебедева. В 1952-1953 годах на этой основе, под руководством

Мельникова и Бурцева была разработана "БЭСМ-1" (Большая электронная счетная машина).

А на ее основе был произведен серийный выпуск машины "БЭСМ-2". В это же время в США

выпускают машину "Эдвак". Технические характеристики машины "БЭСМ-2" были гораздо

выше. Это было связано с тем, что в "БЭСМ-2", использовались два совершенно новых

принципа: конвейеризации и стека. Для "БЭСМ-2", быстродействие АЛУ составляло порядка

10000 операций в секунду.

В 1953 году была разработана машина "Стрела" под руководством Василевского. А так же в

Московском Энергетическом институте под руководством академика Брука были

разработаны ЭВМ получившие название "М". В Минске был создан завод по производству

ЭВМ, серийное производство машин "Минск". В городе Пензе было создано ОКБ (отдел

конструкторского бюро) под руководством академика Рамеева, где разработали и выпускали

серийно ЭВМ "Урал".

Структура ЭВМ первого поколения полностью соответствовали машине фон Неймана.

Технические характеристики машин были значительно ниже характеристик современных

ПК. Программирование велось в машинных кодах. Емкость ОЗУ - 2 тысячи слов. Ввод

информации с перфоленты и кинопленки.

Второе поколение ЭВМ.

Связывают с переходом от ламповых к транзисторным ЭВМ. Транзисторы позволяли

обеспечить большую надежность, быстродействие и меньшее энергопотребление (среднее

время отказа около 100 часов, тогда как на машинах первого поколение около 10 часов,

энергоемкость на два порядка ниже, по сравнению с машинами первого поколения). Переход

к печатному монтажу также улучшило надежность.

Начинается бурное развитие математического и программного обеспечения. Высшая точка:

создание алгоритмических языков (Fortran, ALGOL). Создаются простейшие компиляторы и

интерпретаторы. Становится нецелесообразна работа пользователя у пульта управления.

Основным режимом становится работа через операторов. Появляются многопрограммные

ЭВМ. Многопрограммность достигается за счет программной обработки. Для работы в

пакетном режиме создаются первые мониторы и supervisor'ы. Вследствие чего происходит

резкое увеличение использование ЭВМ второго поколения.

Третье поколение ЭВМ.

В конце 60-х годов появляются первые машины третьего поколения. Переход к третьему

поколению ЭВМ связывают с серьезными архитектурными изменениями. Изменение

технической базы связано с переходом на интегральную схематехнику. Правда степень

интеграции была небольшой. Вследствие чего произошло заметное увеличение надежности.

В машинах третьего поколения формируется концепция канала, начинается работа с

распараллеливанием процессора, появляется микропрограммное управление, иерархируется

память, впервые вводится понятие агрегатирования.

АЛУ

СОЗУ

Память

Устройство управления

Преобразование адресов

Канал

ВЗУ УВВ

Пульт

Управления

СПП

- 4 -

…

ком. обмена …

МК - мультиплетный канал (медленные устройства)

СК - селекторный канал (высокоскоростные устройства)

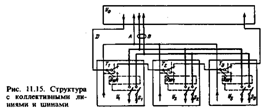

Канал является основным структурным элементом.

В структуре процессора и оперативной памяти появляются специальные устройства, которые

организуют адресные механизмы (обеспечивающие адресацию, перемещение программы в

памяти, взаимную защиту). В процессоре появляется несколько АЛУ (целочисленные, с

плавающей арифметикой, для работы с адресами). Правда, эти устройства параллельно не

работают, но для выполнения той или иной обработки выбирается определенное АЛУ. В

памяти четко выделяется основная память, к которой процессор обращается

непосредственно, и массовая память, емкость которой значительно больше емкости

основной памяти, но непосредственно процессору она недоступна. Тем более данные с

внешних устройств непосредственно недоступны процессору. Так как память иерархична, то

создаются механизмы для управления памятью. Развивается и внутренняя память процессора

(создаются предпосылки кэширования). В конце третьего поколения ЭВМ появляется

концепция управления виртуальной памяти, развиваются внешние устройства и

терминальное оборудование. Самое главное в тот период: унификация ЭВМ по

конструктивно - технологическим параметрам. ЭВМ третьего поколения начинают

выпускаться сериями или семействами, совместимыми моделями.

Дальнейшее развитие математического и программного обеспечения приводит к созданию

пакетных программ для решения типовых задач, проблемно - ориентированных

программных языков (для решения задач отдельной категории) и впервые создаются

уникальные программные комплексы, - операционные системы (разработаны IBM).

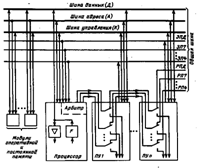

Четвертое поколение ЭВМ.

В конце 70-х кодов появляются первые ЭВМ четвертого поколения. Связано с переходом на

интегральные схемы средней и большой степени интеграции.

Характерные свойства ЭВМ четвертого поколения:

1. Мультипроцессорность

2. Параллельно - последовательная обработка

3. Языки высокого уровня

4. Появляются первые сети ЭВМ

Технические характеристики ЭВМ четвертого поколения:

1. Средняя задержка сигнала 0.7 нс./вентиль (вентиль - типовая схема)

2. Впервые основная память - полупроводниковая. Время выработки данного из такой

памяти 100-150 нс. Емкость 1012 -1013 символов.

3. Впервые применяется аппаратная реализация оперативной системы

4. Модульное построение стало применяться и для программных средств

Основная внимание машин четвертого поколения было направлено на сервис (улучшение

общения ЭВМ и человека).

Пятое поколение ЭВМ.

В конце 80-х годов появляются первые ЭВМ пятого поколения.

Пятое поколение ЭВМ связывают с переходом к микропроцессорам. С точки зрения

структурного построения характерна максимальная децентрализация управления. С точки

зрения программного и математического обеспечения - переход на работу в программных

средах и оболочках. Производительность

Процессор Оперативная

память

МК

СК

УВВ УВВ

ВЗУ ВЗУ

- 5 -

108 - 109 операций в секунду. Для пятого и шестого поколения характерны

многопроцессорные структуры созданные на упрощенных микропроцессорах, которых очень

много (решающие поля или среды). Создаются ЭВМ ориентированные на языки высокого

уровня.

В этот период существуют две диаметрально противоположных тенденции:

1. Персонификация ресурсов

2. Коллективизация ресурсов (коллективный доступ - сети)

Классы вычислительных машин

Определение. Электронная вычислительная машина (компьютер) - это комплекс технических средств, предназначенных для автоматической обработки информации в процессе решения вычислительных и информационных задач.

По принципу действия ЭВМ классифицируются на

-

Аналоговые ВМ;

-

Цифровые ВМ;

-

Гибридные ВМ.

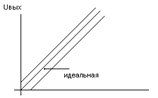

Критерий такой классификации - форма представления обрабатываемой информации. Аналоговые вычислительные машины работают с информацией, представленной в непрерывной (аналоговой форме), то есть в виде непрерывного ряда значений какой-либо физической величины: силы тока, напряжения (чаще всего), угла поворота какого-либо механизма и т.п.Достоинства АВМ: простота эксплуатации, приемлемое быстродействие. Недостатки: отсутствие универсальности, низкая точность вычислений. Цифровые вычислительные машины работают с информацией, представленной в дискретной форме - в виде двоичного кода. Гибридные вычислительные машины - аналого-цифровые ВМ, сочетающие в себе достоинства АВМ и ЦВМ. Точнее будет говорить о гибридной вычислительной системе, так как структурная схема аналого-цифровых машин включает в себя собственно АВМ и ЦВМ, а также набор устройств, преобразующих информацию из одной формы в другую. Одна из машин является основной, отсюда деление ГВС на аналого-ориентированные и цифро-ориентированные. Гибридные вычислительные машины используют для управления сложными технологическими объектами (управление прокатным станом), а также для описания случайных процессов или управления динамическими системами в реальном времени (например, решение задач самонаведения).

По назначению ЭВМ принято классифицировать на

-

Общего назначения (универсальные);

-

Проблемно-ориентированные (для решения круга задач некоторой предметной области);

-

Специализированные (для решения узкого круга задач, многие вещи реализованы аппаратно).

По размерам и вычислительной мощности ЭВМ разделяют на:

-

Суперкомпьютеры;

-

Большие ЭВМ;

-

Малые ЭВМ;

-

Микро ЭВМ;

-

Мобильные ЭВМ;

Большие ЭВМ

За рубежом (а теперь и у нас) они получили названия «мэйнфреймы» (mainframe). Современные большие ЭВМ, как правило, обладают следующими характеристиками:

-

Производительность не менее 100 миллионов операций в секунду;

-

Основная память емкостью 1 - 10 Гбайт;

-

Внешняя память емкость. Не менее 100 Гбайт;

-

Поддержка многопользовательского режима работы от 16 до 1000 пользователей.

Применение больших ЭВМ

-

Решение научно-технических задач;

-

Работа в вычислительных сетях с пакетной обработкой информации;

-

Работа с большими базами данных;

-

Управление вычислительными сетями и их ресурсами (наиболее актуальное направление. Отсюда терминологическая путаница: мэйнфреймы часто называют большими серверами в специальной литературе. При этом смешивается различные основания классификации ЭВМ - по сфере применения и по размеру и производительности).

Важно помнить: около 70% электронной информации всего мира в настоящее время хранится в мэйнфреймах. Объемы продаж их в последние годы возрастают

Современные большие ЭВМ:

-

Советские ЕС ЭВМ (архитектура аналогичная IBM 360/379). До сих пор используются в различных учреждениях и производствах, являются хранилищем огромного количества информации, которая представляет собой стратегическую ценность для России.

-

Большие машины IBM 3-его поколения. Серия IBM ES/9000. Созданы в 1990 году, производительность - свыше миллиарда операций в секунду.

-

Большие машины IBM 4-го поколения. Серия IBM S/390. Серия заявлена в 1997 году. Позволяет создавать большие (по производительности) ЭВМ значительно более компактных размеров. Быстродействие: от 50 до 500 миллионов операций в секунду (в зависимости от количества установленных процессоров). Предусмотрена возможность параллельного объединения таких ЭВМ в мощную вычислительную систему - до 32 машин. В 1993 году фирма IBM заключила с РФ договор, по которому передала право сборки машин серии S/390 на предприятиях России.

-

Средние машины IBM AS/400. Серия заявлена в 1999 году. Быстродействие - сотни миллионов операций в секунду, за счет объединения до 12 процессоров типа Pentium II или Power PC.

-

Машины Fujitsu M 1800 (Япония), Amdahl Millenium (Япония), Comparex M200, Comparex C2000 (Германия). Производительность 0.5 - 1 миллиард операций в секунду. В России машины фирмы Comparex Information Systems используются в РАО Газпром, ФАПИ и т.д.

Требования к современным большим ЭВМ (в порядке убывания значимости):

-

Надежность;

-

Производительность;

-

Емкость и время обращения к основной памяти;

-

Емкость и время обращения к внешней памяти;

-

Количество каналов и эффективность системы ввода-вывода (в современных больших ЭВМ - до 256 каналов);

-

Аппаратная и программная совместимость с другими компьютерами ЭВМ.

Тенденции развития класса больших ЭВМ

-

Миниатюризация при возрастании производительной мощности;

-

Сохранение и укрепление позиций на рынке ЭВМ:

-

До 70% всей «компьютерной» информации хранится в мэйнфреймах;

-

В последние годы отмечается рост продаж больших ЭВМ (хотя их доля в общем парке ЭВМ продолжает снижаться).

-

-

Размывание критериев отнесения ЭВМ к классу больших. Во-первых, современные большие ЭВМ - зачастую многопроцессорные вычислительные комплексы. Во-вторых, производительность, габариты и цена машин внутри класса очень сильно разнятся. Каждый производитель предлагает собственную классификацию своей продукции (см. выше серию IBM AS/400, которые фирма называет «средними ЭВМ»).

Малые ЭВМ

Промежуточное звено между большими ЭВМ и микро ЭВМ. На сегодняшний день очень трудно указать характеристики ЭВМ, которые могли бы быть определяющими для отнесения того или иного компьютера к рассматриваемому классу. Многие современные ЭВМ, которые производитель заявляет, как «малые» нисколько не уступают компьютерам, созданным 10-15 лет назад и единодушно признанным «большими».

Перечислим некоторые особенности малых ЭВМ:

-

Основа - один или несколько микропроцессоров (32, 64 или 128-разрядных);

-

Аппаратная реализация многих системных функций ввода-вывода информации;

-

Возможность простого расширения до многопроцессорных и многомашинных вычислительных систем;

-

Высокая скорость обработки прерываний;

-

Повышенная (по сравнению с микро-ЭВМ) точность вычислений.

Применение малых ЭВМ:

-

Управление технологическими процессами (включая управление большим количеством периферийных устройств);

-

Выполнение вычислений в многопользовательских вычислительных системах, в том числе многопользовательских САПР, системах ИИ и т.п.

-

Управление вычислительными сетями и их ресурсами.

Примеры современных малых ЭВМ:

-

Семейство VAX 8000, VAX 9000. Могут объединять от 1 до 32 микропроцессоров, обеспечивая производительность до миллиарда операций в секунду.

-

IBM 4381. Однопроцессорные машины, в настоящее время уже признаются устаревающими. Например, в Госкомстате РФ в 2000 году вместо таких машин перешли к использованию системы IBM S/390.

-

HP 9000 - Малая ЭВМ, которую производитель рекомендует в качестве сервера.

Микрокомпьютеры

Выделяют несколько подклассов микрокомпьютеров:

-

Персональные ЭВМ (ПК);

-

Рабочие станции (workstation, однопользовательские микрокомпьютеры, часто специализированные для выполнения определенного вида работ);

-

Серверы (мощные микрокомпьютеры, выделенные для обработки запросов от рабочих станций сети);

-

Многопользовательские микрокомпьютеры (мощные микрокомпьютеры, оборудованные несколькими видеотерминалами и функционирующие в режиме разделения времени, что позволяет работать на них сразу нескольким пользователям, часто для выполнения специализированных задач);

-

Сетевые компьютеры (net computers, network computers, thin clients, упрощенные микрокомпьютеры, имеющие минимальное программное обеспечение и предназначенные для работы в сети и доступа к сетевым ресурсам).

Основные производители микро-ЭВМ: IBM, DEC, Hewlett-Packard, DELL, DEC, Olivetti, Toshiba, Matsushita. Основные производители процессоров для микрокомпьютеров: Intel, AMD.

Особенности микрокомпьютеров (ПК):

-

Низкая стоимость;

-

Автономность эксплуатации;

-

Гибкость архитектуры, обеспечивающая универсальность применения и адаптируемость к использованию в самых разных ситуациях (например, можно подключить к ПК швейную машину и вышивать узоры);

-

Дружественность системного и прикладного программного обеспечения;

-

Высокая надежность работы (наработка на отказ - свыше 5000 часов).

Мобильные ЭВМ

Иногда рассматривают как подкласс микро-ЭВМ. Предлагается все же выделить в отдельный класс.

Основные особенности всех портативных ЭВМ:

-

Портативность, то есть возможность легкого переноса и использования в походных условиях: на улице, дома, в офисе.

-

Автономность работы, в том числе энергетическая, то есть возможность работы на аккумуляторах.

-

Возможность подключения дополнительных устройств и интегрируемость с микро-ЭВМ.

В последние годы отмечается рост использования мобильных устройств. Это объясняется следующими факторами:

-

Снижение цены и выравнивание по ключевым параметром мобильных и персональных ПК;

-

Улучшение программного обеспечения для мобильных ЭВМ (по количеству и качеству);

-

Повышение уровня интеграции между микро- и мобильными ЭВМ.

-

Широкомасштабная кампания по продвижению мобильных устройств (со стороны самих разработчиков устройств, производителей ПО, IT-специалистов).

Виды мобильных ЭВМ:

-

Портативные рабочие станции - обычные микро-ЭВМ, но оформленные в удобном для переноса виде, предшественники наколенных компьютеров и ноутбуков.

-

Наколенные компьютеры (laptops) - весят 5-10 кг, по большинству параметров не уступают настольным персональным компьютерам, предназначены для работы вне офиса и проведения выездных презентаций. В настоящее время уступают свое место ноутбукам.

-

Ноутбуки (notebook, omnibook) - конструктивно оформляются в виде миниатюрного чемоданчика. По основным параметрам не уступают настольным ПК, имя значительно меньшие размеры и вес. Современные ноутбуки имеют операционные системы, аналогичные ОС для ПК, поэтому в них может использоваться такое же программное обеспечение, что и в обычных ПК. Подключение дополнительных устройств может быть через стандартные интерфейсы для персональных ЭВМ, а также с использованием PC-карт. PC-карты (PCMCIA-карты, PCMCIA - Personal Computer Memory Card International Association) - это платы специальной конструкции, спецификация для которых в начале была разработаны как для плат памяти. В дальнейшем указанный стандарт лег в основу для создания модемных, сетевых плат, радио-тюнеров, контроллеров сотовой и пэйджинговой связи, систем спутникового позиционирования. Большинство PC-карт поддерживает технологию Plug-n-Play, поэтому не требуют дополнительной настройки подключаемых устройств для работы. Современные ноутбуки обязательно имеют различные аппаратные средства для коммуникации и интеграции с настольными ПК и информационно-вычислительными сетями (встроенный факс-модем, встроенная сетевая карта, инфракрасный порт, Bluetooth-адаптер, клиентский Wi-Fi-интерфейс). Большинство современных ноутбуков имеют цветной жидкокристаллический дисплей диагональю 14-15 дюймов. Выделяют также подкласс субноутбуков с диагональю дисплея 10-12 дюймов, а также уменьшенными габаритами и весом. Они пока получили меньшее распространение из-за неудобной системы ввода-вывода и более высокой цены. Современные средства ввода-вывода для ноутбуков: встроенная клавиатура (с возможностью подключения стандартной или нестандартной клавиатуры через USB-интерфейс), мышь (часто беспроводная), трекбол, трекпойнт, трекпэд (тачпэд).

-

Карманные компьютеры (КПК, PDA - Personal Digital Assistant, Palmtop). Имеют массу от 100 до 300 грамм, размеры 150×80×20 мм. Первый КПК был создан в 1992 году фирмой U.S. Robotics. Особенности КПК: большая автономность работы; специальные операционные системы и прикладное ПО; наличие программных средства для интеграции и синхронизации данных; наличие средств распознавания рукописного текста (как дополнительный инструмент ввода информации); возможность подключения периферийных устройств: портативного принтера, адаптеров беспроводной связи, контроллеров сотовой и пэйджинговой связи, систем спутниковой навигации; возможность записи и воспроизведения звука, съемки и просмотра фотографий и видеоклипов; средства работы с текстами, эл. таблицами; средства работы с электронной почтой и Интернет. Средства ввода информации в КПК: управляющие клавиши, клавиатура или специальное перо (стилус) + сенсорный экран. В современных ПК используются следующие семейства операционных систем: Windows Mobile (ранее: Windows CE), Palm OS, Symbian (до 1998 - EPOC). Среди современных КПК выделяют подклассы: коммуникаторов и смартфонов. Специалисты считают, что в будущем все КПК будут обладать коммуникационными возможностями.

-

Планшетные ПК (Tablet PC). Специальный класс мобильных ЭВМ, имеющих большой экран и позволяющие вводить информацию с помощью электронного пера, либо с помощью клавиатуры. Современные планшетные ПК имеют жидкокристаллические дисплеи с диагональю 10-13 дюймов и предлагают развитые инструменты для распознавания рукописной информации. На рынке существуют как мощные планшетные ПК, которые не уступают по своим параметрам ноутбукам, так и упрощенные устройства («райтеры», writers), которые предназначены только для работы с текстом и обмена информации с настольной ЭВМ или информационно-вычислительной сетью. В такие устройства ввод информации, как правило, осуществляется только при помощи клавиатуры.

-

Электронные записные книжки (органайзеры). Наиболее простые представители класса мобильных ЭВМ. Ограничивают работу пользователя перечнем заранее предустановленных программ, к которым относятся: текстовый редактор, записная книжка, телефонная и адресная книги, будильник, таймер и т.п. Предусматривается защита информации от несанкционированного доступа. В настоящее время этот класс устройств теряет свои позиции на рынке.

Суперкомпьютеры

К суперкомпьютерам относятся мощные многопроцессорные вычислительные машины с быстродействием в десятки миллиардов операций в секунду. Особенности архитектуры суперкомпьютеров будут рассмотрены после знакомства с многомашинными и многопроцессорными вычислительными системами.

В последнее время от выше рассмотренной классификации все чаще переходят к группированию ЭВМ по сфере применения, иначе говоря, по месту и роли компьютера в сети:

-

Сетевые компьютеры;

-

Рабочие станции;

-

Серверы;

-

Суперсерверы.

Информация, кодирование, обработка в ЭВМ

В ЭВМ применяется двоичная система счисления, т.е. все числа в компьютере представляются с помощью нулей и единиц, поэтому компьютер может обрабатывать только информацию, представленную в цифровой форме.

Для преобразования числовой, текстовой, графической, звуковой информации в цифровую необходимо применить кодирование.

Кодирование - это преобразование данных одного типа через данные другого типа. В ЭВМ применяется система двоичного кодирования, основанная на представлении данных последовательностью двух знаков: 1 и 0, которые называются двоичными цифрами (binary digit - сокращенно bit).

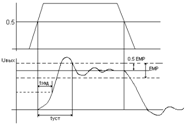

Целые числа кодируются двоичным кодом довольно просто (путем деления числа на два). Для кодирования нечисловой информации используется следующий алгоритм: все возможные значения кодируемой информации нумеруются и эти номера кодируются с помощью двоичного кода.

Кодирование чисел

Есть два основных формата представления чисел в памяти компьютера. Один из них используется для кодирования целых чисел, второй (так называемое представление числа в формате с плавающей точкой) используется для задания некоторого подмножества действительных чисел.

Кодирование целых чисел производиться через их представление в двоичной системе счисления: именно в этом виде они и помещаются в ячейке. Один бит отводиться при этом для представления знака числа (нулем кодируется знак "плюс", единицей - "минус").

Для кодирования действительных чисел существует специальный формат чисел с плавающей запятой. Число при этом представляется в виде: , где M - мантисса, p - порядок числа N, q - основание системы счисления. Если при этом мантисса M удовлетворяет условию , то число N называют нормализованным.

Кодирование координат

Закодировать можно не только числа, но и другую информацию, например, о том, где находится некоторый объект. Величины, определяющие положение объекта в пространстве, называются координатами. В любой системе координат есть начало отсчёта, единица измерения, масштаб, направление отсчёта, или оси координат. Примеры систем координат - декартовы координаты, полярная система координат, шахматы, географические координаты.

Кодирование текста

Для представления текстовой информации используется таблица нумерации символов или таблица кодировки символов, в которой каждому символу соответствует целое число (порядковый номер). Восемь двоичных разрядов могут закодировать 256 различных символов.

Существующий стандарт ASCII (сокращение от American Standard Code for Information Intercange - американский стандартный код для обмена информацией; 8 - разрядная система кодирования) содержит две таблицы кодирования - базовую и расширенную. Первая таблица содержит 128 основных символов, в ней размещены коды символов английского алфавита, а во второй таблице кодирования содержатся 128 расширенных символов.

Так как в этот стандарт не входят символы национальных алфавитов других стран, то в каждой стране 128 кодов расширенных символов заменяются символами национального алфавита. В настоящее время существует множество таблиц кодировки символов, в которых 128 кодов расширенных символов заменены символами национального алфавита.

Так, например, кодировка символов русского языка Widows - 1251 используется для компьютеров, работающих под ОС Windows. Другая кодировка для русского языка - это КОИ - 8, которая также широко используется в компьютерных сетях и российском секторе Интернет.

В настоящее время существует универсальная система UNICODE, основанная на 16 - разрядном кодировании символов. Эта 16 - разрядная система обеспечивает универсальные коды для 65536 различных символов, т.е. в этой таблице могут разместиться символы языков большинства стран мира.

Кодирование графической информации

В видеопамяти находится двоичная информация об изображении, выводимом на экран. Почти все создаваемые, обрабатываемые или просматриваемые с помощью компьютера изображения можно разделить на две большие группы - растровую и векторнуюграфику.

Растровые изображения представляют собой однослойную сетку точек, называемых пикселями (pixel, от англ. picture element). Код пикселя содержит информации о его цвете.

Для описания черно-белых изображений используются оттенки серого цвета, то есть при кодировании учитывается только яркость. Она описывается одним числом, поэтому для кодирования одного пикселя требуется от 1 до 8 бит: чёрный цвет - 0, белый цвет - N = 2k-l, где k - число разрядов, которые отводятся для кодирования цвета. Например, при длине ячейки в 8 бит это 256-1 = 255. Человеческий глаз в состоянии различить от 100 до 200 оттенков серого цвета, поэтому восьми разрядов для этого вполне хватает.

Цветные изображения воспринимаются нами как сумма трёх основных цветов - красного, зелёного и синего. Например, сиреневый = красный + синий; жёлтый = красный + зелёный; оранжевый = красный + зелёный, но в другой пропорции. Поэтому достаточно закодировать цвет тремя числами - яркостью его красной, зелёной и синей составляющих. Этот способ кодирования называется RGB (Red - Green - Blue). Его используют в устройствах, способных излучать свет (мониторы). При рисовании на бумаге действуют другие правила, так как краски сами по себе не испускают свет, а только поглощают некоторые цвета спектра. Если смешать красную и зелёную краски, то получится коричневый, а не жёлтый цвет. Поэтому при печати цветных изображений используют метод CMY (Cyan - Magenta - Yellow) - голубой, сиреневый, жёлтый цвета. При таком кодировании красный = сиреневый + жёлтый; зелёный = голубой + жёлтый.

В противоположность растровой графике векторное изображение многослойно. Каждый элемент такого изображения - линия, прямоугольник, окружность или фрагмент текста - располагается в своем собственном слое, пиксели которого устанавливаются независимо от других слоев. Каждый элемент векторного изображения является объектом, который описывается с помощью специального языка (математических уравнения линий, дуг, окружностей и т.д.) Сложные объекты (ломаные линии, различные геометрические фигуры) представляются в виде совокупности элементарных графических объектов.

Объекты векторного изображения, в отличие от растровой графики, могут изменять свои размеры без потери качества (при увеличении растрового изображения увеличивается зернистость).

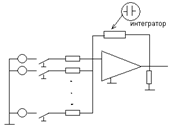

Кодирование звука

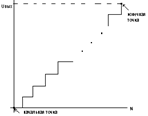

Как всякий звук, музыка является не чем иным, как звуковыми колебаниями, зарегистрировав которые достаточно точно, можно этот звук безошибочно воспроизвести. Нужно только непрерывный сигнал, которым является звук, преобразовать в последовательность нулей и единиц. С помощью микрофона звук можно превратить в электрические колебания и измерить их амплитуду через равные промежутки времени (несколько десятков тысяч раз в секунду). Каждое измерение записывается в двоичном коде. Этот процесс называется дискретизацией. Устройство для выполнения дискретизации называется аналогово-цифровым преобразователем (АЦП). Воспроизведение такого звука ведётся при помощи цифро-аналогового преобразователя (ЦАП). Полученный ступенчатый сигнал сглаживается и преобразуется в звук при помощи усилителя и динамика. На качество воспроизведения влияют частота дискретизации и разрешение (размер ячейки, отведённой под запись значения амплитуды). Например, при записи музыки на компакт-диски используются 16-разрядные значения и частота дискретизации 44 032 Гц.

Описанный способ кодирования звуковой информации достаточно универсален, он позволяет представить любой звук и преобразовывать его самыми разными способами. Но бывают случаи, когда выгодней действовать по-иному.

Издавна используется достаточно компактный способ представления музыки - нотная запись. В ней с помощью специальных символов указывается высота и длительность, общий темп исполнения и как сыграть. Фактически, такую запись можно считать алгоритмом для музыканта, записанным на особом формальном языке. В 1983 г. ведущие производители компьютеров и музыкальных синтезаторов разработали стандарт, определивший такую систему кодов. Он получил название MIDI (Musical Instrument Digital Interface). При таком кодировании запись компактна, легко меняется инструмент исполнителя, тональность звучания, одна и та же запись воспроизводится как на синтезаторе, так и на компьютере.

Конечно, такая система кодирования позволяет записать далеко не всякий звук, она годится только для инструментальной музыки. Но есть у нее и преимущества: чрезвычайно компактная запись, естественность для музыканта (практически любой MIDI-редактор позволяет работать с музыкой в виде обычных нот), легкость замены инструментов, изменения темпа и тональности мелодии.

Есть и другие форматы записи музыки. Среди них - формат MP3, позволяющий с очень большим качеством и степенью сжатия кодировать музыку, при этом вместо 18 - 20 музыкальных композиций на стандартном компакт-диске (CDROM) помещается около 200. Одна песня занимает примерно 3,5 Mb, что позволяет пользователям сети Интернет легко обмениваться музыкальными композициями.

Алгебраическое представление двоичных чисел

Знак числа обычно кодируется двоичной цифрой: знак "+" кодируется 0, знак "-" кодируется 1. Если двоичные числа -45 и 31 в форме с запятой, фиксированной после нулевого разряда, сложить, то получим неверный результат 1100.1100 или в десятичной системе счисления -45+31 =-76 (10101101+00011111=11001100). Чтобы арифметические операции над знаковыми числами в ЭВМ можно было бы производить точно также, как и с беззнаковыми переменными, отрицательные числа представляются в дополнительном коде.

Следует упомянуть, что aльтepнaтивными являютcя представления в прямом и обратном коде.

Прямой код числа N -  = -(abs(N). Такой код и был использован в рассмотренном выше примере. Недостатки такого представления:

= -(abs(N). Такой код и был использован в рассмотренном выше примере. Недостатки такого представления:

- операцию вычитания нельзя заменить операцией сложения;

- представление числа 0 неоднозначно.

Обратный код числа получается инверсией двоичных разрядов. Через аобозначим двоичный разряд числа, а через а* - инверсию двоичного разряда (если а=1, то а*=0 и если а=0, то а*=1). Правило получения обратного кода:

если N>0, то  = 0aaaaaaa;

= 0aaaaaaa;

если N<0, то  =1 а* а* а* а* а* а* а* а*,

=1 а* а* а* а* а* а* а* а*,

если N=0, то имеет место неоднозначность ![]() или

или  .

.

Например, число 11 в обратном коде представляется как 0.1011, а число с=-7 будет представлено как 1.1000. Сложим эти числа:

0.1011+1.1000= 0.0011+ единица переноса из старшего разряда.

Если единицу пересоса из старшего разряда игнорировать, то результат сложения неверный: 11-7=3. Чтобы получить верный результат, необходимо единицу переноса добавить к младшему разряду результата: 0.1011+1.1000=0.0011+0.0001=0.0100 (11-7=4).

Следовательно,

- представление 0 в обратном коде неоднозначно;

- операцию вычитания можно заменить операцией сложения, однако, если в результате выполнения операции будет получен перенос из старшего (знакового) разряда, эту 1 необходимо добавить к младшему разряду результата, чтобы получилось правильное значение.

В дополнительном коде положительное число представляется также, как в прямом и обратном кодах, т.е. при N>0,  = 0aaaaaaa.

= 0aaaaaaa.

Чтобы получить дополнительный код отрицательного числа:

1) надо взять его положительную форму (взять прямой код положительного числа);

2) обратить каждый бит (иначе говоря, заменить в представлении числа 0 на 1 и 1 на 0);

3) добавить к полученному числу 1 младшего разряда. Например, представим в дополнительном коде число-32:

1) положительная форма числа -0.00100000;

2) обратим биты -1.11011111;

3) добавим 1 -1.11011111 +0.00000001

получим 1.11100000 - дополнительный код числа.

Достоинства такого кода заключается в том, что нуль однозначно представляется кодом 0,0000....0 и, кроме того, операцию вычитания можно заменить операцией сложения.

Недостаток такого представления - при использовании дополнительного кода отрицательное число становится трудно расшифровать. Однако дело облегчается тем, что положительную форму отрицательного числа в дополнительном коде можно получить аналогично вышеописанной методике, выполнив пункты 2 и 3. Проверим на рассмотренном выше примере:

2) обращаем биты 000011111;

3) добавляем 1 + 0.00000001 получим 0.00100000.

2.Выполнение арифметических операций в компьютере

Правила выполнения арифметических операций для позиционных систем счисления задаются таблицами сложения, вычитания и умножения одноразрядных чисел.

Логические основы ЭВМ, элементы и узлы

Алгебра логики (булева алгебра) - это раздел математики, возникший в XIX веке благодаря усилиям английского математика Дж. Буля. Поначалу булева алгебра не имела никакого практического значения. Однако уже XX веке ее положения нашли применение в описании функционирования и разработке различных электронных схем. Законы и аппарат алгебры логики стал использоваться при проектировании различных частей компьютеров (память, процессор). Хотя это не единственная сфера применения данной науки.

Что же собой представляет алгебра логики? Во-первых, она изучает методы установления истинности или ложности сложных логических высказываний с помощью алгебраических методов. Во-вторых, булева алгебра делает это таким образом, что сложное логическое высказывание описывается функцией, результатом вычисления которой может быть либо истина, либо ложь (1, либо 0). При этом аргументы функции (простые высказывания) также могут иметь только два значения: 0, либо 1.

Что такое простое логическое высказывание? Это фразы типа «два больше одного», «5.8 является целым числом». В первом случае мы имеем истину, а во втором ложь. Алгебра логики не касается сути этих высказываний. Если кто-то решит, что высказывание «Земля квадратная» истинно, то алгебра логики это примет как факт. Дело в том, что булева алгебра занимается вычислениями результата сложных логических высказываний на основе заранее известных значений простых высказываний.

Логические операции. Дизъюнкция, конъюнкция и отрицание

Так как же связываются между собой простые логические высказывания, образуя сложные? В естественном языке мы используем различные союзы и другие части речи. Например, «и», «или», «либо», «не», «если», «то», «тогда». Пример сложных высказываний: «у него есть знания и навыки», «она приедет во вторник, либо в среду», «я буду играть тогда, когда сделаю уроки», «5 неравно 6». Как мы решаем, что нам сказали правду или нет? Как-то логически, даже где-то неосознанно, исходя из предыдущего жизненного опыта, мы понимает, что правда при союзе «и» наступает в случае правдивости обоих простых высказываний. Стоит одному стать ложью и все сложное высказывание будет лживо. А вот, при связке «либо» должно быть правдой только одно простое высказывание, и тогда все выражение станет истинным.

Булева алгебра переложила этот жизненный опыт на аппарат математики, формализовала его, ввела жесткие правила получения однозначного результата. Союзы стали называться здесь логическими операторами.

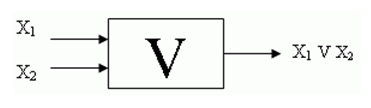

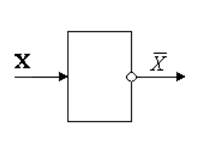

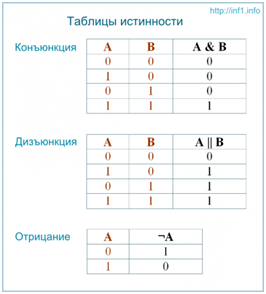

Алгебра логики предусматривает множество логических операций. Однако три из них заслуживают особого внимания, т.к. с их помощью можно описать все остальные, и, следовательно, использовать меньше разнообразных устройств при конструировании схем. Такими операциями являются конъюнкция (И), дизъюнкция (ИЛИ) и отрицание (НЕ). Часто конъюнкцию обозначают &, ᴧ, дизъюнкцию - ||, V а отрицание - чертой над переменной, обозначающей высказывание.

Функция конъюнкции истин(логического умножения) на тогда, когда истинны одновременно оба высказывания.

Дизъюнкция. Читается X1 ИЛИ X2: часто это высказывание называют логическим сложением. Функция дизъюнкции истинна тогда, когда хотя бы одно из высказываний истинно.

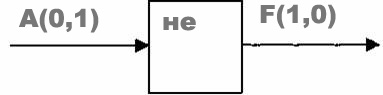

Логическое отрицание - инверсия. Инверсия - это высказывание, которое истинно, если исходное высказывание ложно; и, наоборот, ложно, если исходное высказывание истинно.

Таблицы истинности

Логические операции удобно описывать так называемыми таблицами истинности, в которых отражают результаты вычислений сложных высказываний при различных значениях исходных простых высказываний. Простые высказывания обозначаются переменными (например, A и B).

Логические основы компьютера

В ЭВМ используются различные устройства, работу которых прекрасно описывает алгебра логики. К таким устройствам относятся группы переключателей, триггеры, сумматоры.

Кроме того, связь между булевой алгеброй и компьютерами лежит и в используемой в ЭВМ системе счисления. Как известно она двоичная. Поэтому в устройствах компьютера можно хранить и преобразовывать как числа, так и значения логических переменных.

Переключательные схемы

В ЭВМ применяются электрические схемы, состоящие из множества переключателей. Переключатель может находиться только в двух состояниях: замкнутом и разомкнутом. В первом случае - ток проходит, во втором - нет. Описывать работу таких схем очень удобно с помощью алгебры логики. В зависимости от положения переключателей можно получить или не получить сигналы на выходах.

Вентили

В основе построения компьютеров, а точнее аппаратного обеспечения, лежат так называемые вентили. Они представляют собой достаточно простые элементы, которые можно комбинировать между собой, создавая тем самым различные схемы. Одни схемы подходят для осуществления арифметических операций, а на основе других строят различную память ЭВМ.

Простейший вентиль представляет собой транзисторный инвертор, который преобразует низкое напряжение в высокое или наоборот (высокое в низкое). Это можно представить как преобразование логического нуля в логическую единицу или наоборот. т.е. получаем вентиль НЕ.

Соединив пару транзисторов различным способом, получают вентили ИЛИ-НЕ и И-НЕ. Эти вентили принимают уже не один, а два и более входных сигнала. Выходной сигнал всегда один и зависит (выдает высокое или низкое напряжение) от входных сигналов. В случае вентиля ИЛИ-НЕ получить высокое напряжение (логическую единицу) можно только при условии низкого напряжении на всех входах. В случае вентиля И-НЕ все наоборот: логическая единица получается, если все входные сигналы будут нулевыми. Как видно, это обратно таким привычным логическим операциям как И и ИЛИ. Однако обычно используются вентили И-НЕ и ИЛИ-НЕ, т.к. их реализация проще: И-НЕ и ИЛИ-НЕ реализуются двумя транзисторами, тогда как логические И и ИЛИ тремя.

Выходной сигнал вентиля можно выражать как функцию от входных.

Транзистору требуется очень мало времени для переключения из одного состояния в другое (время переключения оценивается в наносекундах). И в этом одно из существенных преимуществ схем, построенных на их основе.

Сумматор и полусумматор

Арифметико-логическое устройство процессора (АЛУ) обязательно содержит в своем составе такие элементы как сумматоры. Эти схемы позволяют складывать двоичные числа.

Как происходит сложение? Допустим, требуется сложить двоичные числа 1001 и 0011. Сначала складываем младшие разряды (последние цифры): 1+1=10. Т.е. в младшем разряде будет 0, а единица - это перенос в старший разряд. Далее: 0 + 1 + 1(от переноса) = 10, т.е. в данном разряде снова запишется 0, а единица уйдет в старший разряд. На третьем шаге: 0 + 0 + 1(от переноса) = 1. В итоге сумма равна 1100.

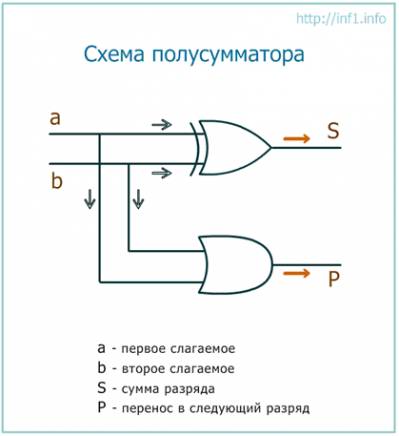

Полусумматор

Теперь не будем обращать внимание на перенос из предыдущего разряда и рассмотрим только, как формируется сумма текущего разряда. Если были даны две единицы или два нуля, то сумма текущего разряда равна 0. Если одно из двух слагаемых равно единице, то сумма равна единицы. Получить такие результаты можно при использовании вентиля ИСКЛЮЧАЮЩЕГО ИЛИ.

Перенос единицы в следующий разряд происходит, если два слагаемых равны единице. И это реализуемо вентилем И.

Тогда сложение в пределах одного разряда (без учета возможной пришедшей единицы из младшего разряда) можно реализовать изображенной ниже схемой, которая называется полусумматором. У полусумматора два входа (для слагаемых) и два выхода (для суммы и переноса). На схеме изображен полусумматор, состоящий из вентилей ИСКЛЮЧАЮЩЕЕ ИЛИ и И.

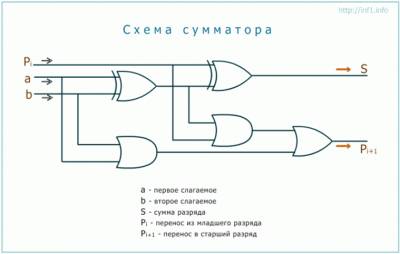

Сумматор

В отличие от полусумматора сумматор учитывает перенос из предыдущего разряда, поэтому имеет не два, а три входа.

Чтобы учесть перенос приходится схему усложнять. По-сути она получается, состоящей из двух полусумматоров.

Рассмотрим один из случаев. Требуется сложить 0 и 1, а также 1 из переноса. Сначала определяем сумму текущего разряда. Судя по левой схеме ИСКЛЮЧАЮЩЕЕ ИЛИ, куда входят a и b, на выходе получаем единицу. В следующее ИСКЛЮЧАЮЩЕЕ ИЛИ уже входят две единицы. Следовательно, сумма будет равна 0.

Теперь смотрим, что происходит с переносом. В один вентиль И входят 0 и 1 (a и b). Получаем 0. Во второй вентиль (правее) заходят две единицы, что дает 1. Проход через вентиль ИЛИ нуля от первого И и единицы от второго И дает нам 1.

Проверим работу схемы простым сложением 0 + 1 + 1 = 10. Т.е. 0 остается в текущем разряде, и единица переходит в старший. Следовательно, логическая схема работает верно.

Работу данной схемы при всех возможных входных значениях можно описать следующей таблицей истинности.

Триггер как элемент памяти. Схема RS-триггера

Память (устройство, предназначенное для хранения данных и команд) является важной частью компьютера. Можно сказать, что она его и определяет: если вычислительное устройство не имеет памяти, то оно уже не компьютер.

Элементарной единицей компьютерной памяти является бит. Поэтому требуется устройство, способное находиться в двух состояниях, т.е. хранить единицу или ноль. Также это устройство должно уметь быстро переключаться из одного состояния в другое под внешним воздействием, что дает возможность изменять информацию. Ну и наконец, устройство должно позволять определять его состояние, т.е. предоставлять во вне информацию о своем состоянии.

Устройством, способным запоминать, хранить и позволяющим считывать информацию, является триггер. Он был изобретен в начале XX века Бонч-Бруевичем.

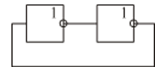

К триггерным принято относить все устройства, имеющих два устойчивых состояния. В основе любого триггера находится кольцо из двух инверторов, показанное на рис.12.1. Общепринято это кольцо изображать в виде так называемой защелки, которая показана на рис.

Рис. Кольцо из двух инверторов

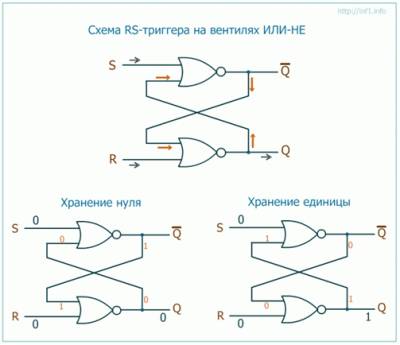

Разнообразие триггеров весьма велико. Наиболее простой из них так называемый RS-триггер, который собирается из двух вентилей. Обычно используют вентили ИЛИ-НЕ или И-НЕ.

RS-триггер на вентилях ИЛИ-НЕ

RS-триггер «запоминает», на какой его вход подавался сигнал, соответствующий единице, в последний раз. Если сигнал был подан на S-вход, то триггер на выходе постоянно «сообщает», что хранит единицу. Если сигнал, соответствующий единице, подан на R-вход, то триггер на выходе имеет 0. Не смотря на то, что триггер имеет два выхода, имеется в виду выход Q. (Q с чертой всегда имеет противоположное Q значение.)

Другими словами, вход S (set) отвечает за установку триггера в 1, а вход R (reset) - за установку триггера в 0. Установка производится сигналом, с высоким напряжением (соответствует единице). Просто все зависит от того, на какой вход он подается.

Большую часть времени на входы подается сигнал равный 0 (низкое напряжение). При этом триггер сохраняет свое прежнее состояние.

Возможны следующие ситуации:

-

Q = 1, сигнал подан на S, следовательно, Q не меняется.

-

Q = 0, сигнал подан на S, следовательно, Q = 1.

-

Q = 1, сигнал подан на R, следовательно, Q = 0.

-

Q = 0, сигнал подан на R, следовательно, Q не меняется.

Ситуация, при которой на оба входа подаются единичные сигналы, недопустима.

Как триггер сохраняет состояние? Допустим, триггер выдает на выходе Q логический 0. Тогда судя по схеме, этот 0 возвращается также и в верхний вентиль, где инвертируется (получается 1) и уже в этом виде передается нижнему вентилю. Тот в свою очередь снова инвертирует сигнал (получается 0), который и имеется на выходе Q. Состояние триггера сохраняется, он хранит 0.

Теперь, допустим, был подан единичный сигнал на вход S. Теперь в верхний вентиль входят два сигнала: 1 от S и 0 от Q. Поскольку вентиль вида ИЛИ-НЕ, то на выходе из него получается 0. Ноль идет на нижний вентиль, там инвертируется (получается 1). Сигнал на выходе Q становится соответствующим 1.

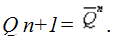

Т триггер

Триггер типа Т называется триггером со счётным входом. Он изменяет своё состояние на противоположное каждый раз, когда на его вход приходит очередной сигнал. Обозначение триггера произошло от первой буквы английского слова toggle - защёлка.

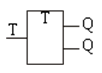

Условное графическое обозначение Т-триггера показано на рис. Т триггер имеет один вход Т и два выхода Q и Õ. T - счётный вход триггера.

Рис. Условное графическое обозначение T триггера

Принцип работы триггера иллюстрирует его таблица истинности

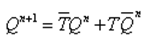

Состояние его выхода меняется на противоположное при поступлении на вход счётного сигнала Т=1 и сохраняется неизменным при Т=0. В соответствии с табл.12.5 характеристическое уравнение Т триггера имеет вид:

Согласно этому уравнению Т триггер сохраняет неизменное состояние при Т=0, когда Q n+1=Q n и при Т=1, когда Q n+1=

Т триггер может быть реализован введением в RS и D триггеры обратных связей (рис.)

Рис. Схемы T триггера

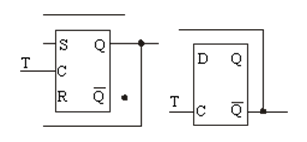

JK триггер

JK триггер наиболее широко используемый универсальный триггер, обладающий характеристиками всех других типов триггеров. JK триггер в отличии от RS триггера не имеет запрещенных комбинаций входных сигналов, которые следует исключать при работе цифровых систем.

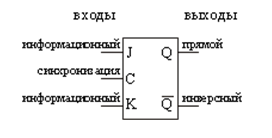

На рис. показано условное графическое обозначение JK триггера.

Рис. Условное графическое обозначение JK триггера

Рассмотрим табл., иллюстрирующую принципы работы JK триггера.

Таблица истинности для JK триггера

Из табл. видно, что когда на оба входа J и K подается уровень логического 0, триггер блокируется, и состояния его выходов не изменяются. В этом случае триггер находится в режиме хранения.

Строки 2 и 3 табл. описывают режимы, соответствующие установке триггера в состояние 0 и 1. Строка 4 соответствует переключательному режиму работы JK триггера. Если на обоих входах J и K установлен уровень логической 1, то следующие друг за другом тактовые импульсы будут вызывать перебросы уровней сигналов на выходах триггера от 1 к 0, от 0 к 1 и т.д. Такая работа триггера напоминает последовательно производимые переключения тумблера, откуда и происходит название режима.

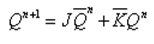

Характеристическое уравнение JK триггера имеет вид:

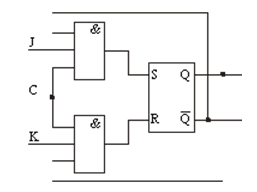

JK триггер может быть реализован с использованием двух элементов И и RS триггера

Рис. Реализация JK триггера

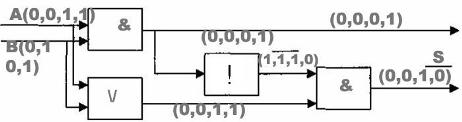

Логические операции и базовые элементы компьютеров

Базовые логические элементы реализуют рассмотренные выше три основные логические операции:

-

логический элемент «И» - логическое умножение;

-

логический элемент «ИЛИ» - логическое сложение;

-

логический элемент «НЕ» - инверсию.

Поскольку любая логическая операция может быть представлена в виде комбинации трех основных, любые устройства компьютера, производящие обработку или хранение информации, могут быть собраны из базовых логических элементов, как из «кирпичиков».

Логические элементы компьютера оперируют с сигналами, представляющими собой электрические импульсы. Есть импульс - логический смысл сигнала - 1, нет импульса - 0. На входы логического элемента поступают сигналы-значения аргументов, на выходе появляется сигнал-значение функции.Преобразование сигнала логическим элементом задается таблицей состояния, которая фактически является таблицей истинности, соответствующей логической функции.

Логический элемент «И». На входы А и В логического элемента (рис. 3.1) подаются два сигнала (00, 01, 10 или 11). На выходе получается сигнал 0 или 1 в соответствии с таблицей истинности операции логического умножения.

Pис. 3.1 Логический элемент • «И»

Логический элемент «ИЛИ». На входы А и В логического элемента (рис. 3.2) подаются два сигнала (00, 01, 10 или 11). На выходе получается сигнал 0 или 1 в соответствии с таблицей истинности операции логического сложения.

Рис. 3.2 Логический элемент • "ИЛИ"

Логический элемент «НЕ». На вход А логического элемента (рис. 3.3) подается сигнал 0 или 1. На выходе получается сигнал 0 или 1 в соответствии с таблицей истинности инверсии

Рис. 3.3 Логический элемент • "НЕ"

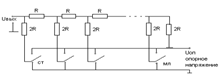

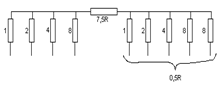

Сумматор двоичных чисел

В целях максимального упрощения работы компьютера все многообразие математических операций в процессоре сводится к сложению двоичных чисел. Поэтому главной частью процессора являются сумматоры, которые как раз и обеспечивают такое сложение. Полусумматор. Вспомним, что при сложении двоичных чисел в каждом разряде образуется сумма и при этом возможен перенос в старший разряд. Введем обозначения слагаемых (А, В), переноса (Р) и суммы (S). Таблица сложения одноразрядных двоичных чисел с учетом переноса в старший разряд выглядит следующим образом:

Слагаемые

Перенос

Сумма

А

В

Р

S

0

0

0

0

0

1

0

1

1

0

0

1

1

1

1

0

Из этой таблицы сразу видно, что перенос можно реализовать с помощью операции логического умножения:

Р =А&В.

Получим теперь формулу для вычисления суммы. Значения суммы близки к результату операции логического сложения (кроме случая, когда на входы подаются две единицы, а на выходе должен получиться нуль).

Нужный результат достигается, если результат логического сложения умножить на инвертированный перенос. Таким образом, для определения суммы можно применить следующее логическое выражение:

S = (А v B) & (А & В).

Построим таблицу истинности для данного логического выражения и убедимся в правильности нашего предположения (табл. 3.11).

Таблица 3.11. Таблица истинности логической функции F= (АvВ)&(А&В)

А

В

AvВ

А&В

А&В

(AvB)&(А&B)

0

0

0

0

1

0

1

0

1

0

1

1

1

0

1

0

1

1

1

1

1

1

0

0

Теперь на основе полученных логических выражений можно построить из базовых логических элементов схему сложения одноразрядных двоичных чисел.

По логической формуле переноса легко определить, что для получения переноса необходимо использовать логический элемент «И».

Анализ логической формулы для суммы показывает, что на выходе должен стоять элемент логического умножения «И», который имеет два входа. На один из входов надо подать результат логического сложения исходных величин А и В, то есть на него должен подаваться сигнал с элемента логического сложения «ИЛИ».

На второй вход требуется подать результат инвертированного логического умножения исходных сигналов (А & В), то есть на второй вход должен подаваться сигнал с элемента «НЕ», на вход которого должен поступать сигнал с элемента логического умножения «И» (рис. 3.4).

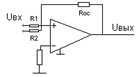

Рис. 3.4. Полусумматор двоичных чисел

Данная схема называется полусумматором, так как реализует суммирование одноразрядных двоичных чисел без учета переноса из младшего разряда.

Полный одноразрядный сумматор. Полный одноразрядный сумматор должен иметь три входа: А, В - слагаемые и Р0 - перенос из младшего разряда и два выхода: сумму S и перенос Р. Таблица сложения в этом случае будет иметь следующий вид:

Слагаемые

Перенос из младшего разряда

Перенос

Сумма

А

В

Р0

Р

S

0

0

0

0

0

0

1

0

0

1

1

0

0

0

1

1

1

0

1

0

0

0

1

0

1

0

1

1

1

0

1

0

1

1

0

1

1

1

1

1

Идея построения полного сумматора точно такая же, как и полусумматора. Из таблицы сложения видно, что перенос (логическая переменная Р) принимает значение 1 тогда, когда хотя бы две входные логические переменные одновременно принимают значение 1. Таким образом, перенос реализуется путем логического сложения результатов попарного логического умножения входных переменных (А, В, ро). Формула переноса получает следующий вид:

Р = (А & В) v (А & Р0) v (В & Р0).

Для получения значения суммы (логическая переменная 5) необходимо результат логического сложения входных переменных (А, В,P0) умножить на инвертированный перенос Р:

S = (А v В v Р0) & !Р.

Данное логическое выражение дает правильные значения суммы во всех случаях, кроме одного, когда на все входные логические переменные принимают значение 1. Действительно:

Р = (1 & 1) v (1 & 1) v (1 & 1) = 1;

S = (1v1v1)&!Р = 1 & 0 = 0.

Для получения правильного значения суммы (для данного случая переменная S должна принимать значение 1) необходимо сложить полученное выше выражение для суммы с результатом логического умножения входных переменных (А, В, P0). В результате логическое выражение для вычисления суммы в полном сумматоре принимает следующий вид:

S = (А v В v Р0) & !Р0 v (А & В & Р0). Многоразрядный сумматор. Многоразрядный сумматор процессора состоит из полных одноразрядных сумматоров. На каждый разряд ставится одноразрядный сумматор, причем выход (перенос) сумматора младшего разряда подключается ко входу сумматора старшего разряда.

Триггер

Важнейшей структурной единицей оперативной памяти компьютера, а также внутренних регистров процессора является триггер. Это устройство позволяет запоминать, хранить и считывать информацию (каждый триггер может хранить 1 бит информации).

Триггер можно построить из двух логических элементов «ИЛИ» и двух элементов «НЕ» (рис. 3.5).

Триггер

В обычном состоянии на входы триггера подан сигнал О, и триггер хранит 0. Для записи 1 на вход 5 (установочный) подается сигнал 1. Последовательно рассмотрев прохождение сигнала по схеме, видим, что триггер переходит в это состояние и будет устойчиво находиться в нем и после того, как сигнал на входе 5 исчезнет. Триггер запомнил 1, то есть с выхода триггера Q можно считать 1.Для того чтобы сбросить информацию и подготовиться к приему новой, подается сигнал 1 на вход К (сброс), после чего триггер возвратится к исходному «нулевому» состоянию.

Преобразование логических формул

-

Закон двойного отрицания (двойное отрицание исключает отрицание):

А =  .

.

-

Переместительный (коммутативный) закон:

-

для логического сложения: А B = B A;

-

для логического умножения: A & B = B & A.

-

Результат операции над высказываниями не зависит от того, в каком порядке берутся эти высказывания.

-

Сочетательный (ассоциативный) закон:

-

для логического сложения: (А B) C = A (B C);

-

для логического умножения: (A & B) & C = A & (B & C).

-

При одинаковых знаках скобки можно ставить произвольно или вообще опускать.

-

Распределительный (дистрибутивный) закон:

-

для логического сложения: (А B) & C = (A & C) (B & C);

-

для логического умножения: (A & B) C = (A C) & (B C).

-

Закон определяет правило выноса общего высказывания за скобку.

-

Закон общей инверсии (законы де Моргана):

-

для логического сложения:

=

=  &

& ;

; -

для логического умножения:

=

=

-

-

Закон идемпотентности (от латинских слов idem - тот же самый и potens - сильный; дословно - равносильный):

-

для логического сложения: А A = A;

-

для логического умножения: A & A = A .

-

Закон означает отсутствие показателей степени.

-

Законы исключения констант:

-

для логического сложения: А 1 = 1, А 0 = A;

-

для логического умножения: A & 1 = A, A & 0 = 0.

-

-

Закон противоречия:

-

A &

= 0.

= 0.

-

Невозможно, чтобы противоречащие высказывания были одновременно истинными.

-

Закон исключения третьего:

-

A

= 1.

= 1.

-

Из двух противоречащих высказываний об одном и том же предмете одно всегда истинно, а второе - ложно, третьего не дано.

-

Закон поглощения:

-

для логического сложения: А (A & B) = A;

-

для логического умножения: A & (A B) = A.

-

Знание законов логики позволяет проверять правильность рассуждений и доказательств. Основываясь на законах, можно выполнять упрощение сложных логических выражений. Такой процесс замены сложной логической функции более простой, но равносильной ей, называется минимизацией функции.

Некоторые преобразования логических формул похожи на преобразования формул в обычной алгебре (вынесение общего множителя за скобки, использование переместительного и сочетательного законов и т.п.), другие - основаны на свойствах, которыми не обладают операции обычной алгебры (использование распределительного закона для конъюнкции, законов поглощения, склеивания, де Моргана и др.).

Нарушения законов логики приводят к логическим ошибкам и вытекающим из них противоречиям.

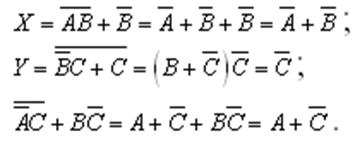

Упрощение формул.

Пример 1. Упростить формулу (А В) & (А С).

Решение:

-

Раскроем скобки: (А В) & (А С) = A & A A & C B & A B & C;

-

По закону идемпотентности A & A =A, следовательно,

A & A A & C B & A B & C = A A & C B & A B & C; -

В высказываниях А и А & C вынесем за скобки А и используя свойство А + 1= 1, получим

A A & C B & A B & C = A & (1 C) B & A B & C = A B & A B & C; -

Аналогично предыдущему пункту вынесем за скобки высказывание А.

A B & A B & C = A & (1 B) B & C = A B & C.

Таким образом, мы доказали закон дистрибутивности.

Всякую формулу можно преобразовать так, что в ней не будет отрицаний сложных высказываний - все отрицания будут применяться только к простым высказываниям.

Пример 2. Упростить выражения ![]() так, чтобы в полученных формулах не содержалось отрицания сложных высказываний.

так, чтобы в полученных формулах не содержалось отрицания сложных высказываний.

Решение:

Базовые представления об архитектуре ЭВМ

Структура компьютера - Это совокупность его функциональных элементов и связей между ними. Элементами могут быть самые различные устройства - от основных логических узлов компьютера до простейших схем. Структура компьютера графически представляется в виде структурных схем, с помощью которых можно дать описание компьютера на любом уровне детализации.

Архитектурой компьютера считается его представление на некотором общем уровне, включающее описание пользовательских возможностей программирования, системы команд, системы адресации, организации памяти и т.д. Архитектура определяет принципы действия, информационные связи и взаимное соединение основных логических узлов компьютера: процессора, оперативного запоминающего устройства (ОЗУ, ОП), внешних ЗУ и периферийных устройств. Общность архитектуры разных компьютеров обеспечивает их совместимость с точки зрения пользователя.

Функциональные блоки (агрегаты, устройства).

В то время как логические элементы и узлы во многом универсальны и могут использоваться в самых различных сочетаниях для решения разнообразных задач, блоки (агрегаты) ЭВМ представляют собой комплексы элементов (узлов), ориентированные на узкий круг задач (операций). Такие агрегаты, как АЛУ, процессор, блок памяти, внешние устройства, обязательно включают в свой состав (кроме механического, оптического, электромагнитного и иного оборудования) логические элементы и узлы, используемые для хранения информации, ее обработки и управления этими процессами.

Центральное устройство (ЦУ) представляет основную компоненту ЭВМ и, в свою очередь, включает ЦП - центральный процессор и ОП - оперативную (главную) память или оперативное запоминающее устройство (ОЗУ).

Процессор непосредственно реализует операции обработки информации и управления вычислительным процессом, осуществляя выборку машинных команд и данных из оперативной памяти, их выполнение и запись результатов в ОП, включение и отключение ВУ. Основными блоками процессора являются:

устройство управления (УУ) с интерфейсом процессора (системой сопряжения и связи процессора с другими узлами машины);

-

арифметико-логическое устройство (АЛУ);

-

процессорная память (внутренний кэш).

Оперативная память предназначена для временного хранения данных и программ в процессе выполнения вычислительных и логических операций.

Арифметико-логическое устройство (АЛУ) - часть процессора, выполняющая арифметические и логические операции над данными.

АЛУ реализует набор простых операций. Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление). Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ). АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и блока управления выполняемым процессом. Устройство работает в соответствии с сообщаемым ему кодами операций, которые должны быть выполнены над переменными, помещаемыми в регистры.

Внешние устройства (ВУ). ВУ обеспечивают эффективное взаимодействие компьютера с окружающей средой - пользователями, объектами управления, другими машинами.

В специализированных управляющих ЭВМ (технологические процессы, связь, ракеты и пр.) внешними устройствами ввода являются датчики (температуры, давления, расстояния и пр.), устройствами вывода - манипуляторы (гидро-, пневмо-, сервоприводы рулей, вентили и др.).

К универсальным ЭВМ (человеко-машинная обработка информации) в качестве ВУ выступают терминалы, принтеры и др. устройства.

Интерфейсы (каналы связи) служат для сопряжения центральных узлов машины с ее внешними устройствами.

Однотипные ЦУ и устройства хранения данных могут использоваться в различных типах машин. Известны примеры того, как фирмы, начавшие свою деятельность с производства управляющих машин, совершенствуя свою деятельность с производства управляющих машин, совершенствуя свою продукцию, перешли к выпуску систем, которые в зависимости от конфигурации ВУ могут исполнять роль как универсальных, так и управляющих машин (машины Hewlett-Packard - HP и Digital Equipment Corporation - DEC).

Архитектура ЭВМ.

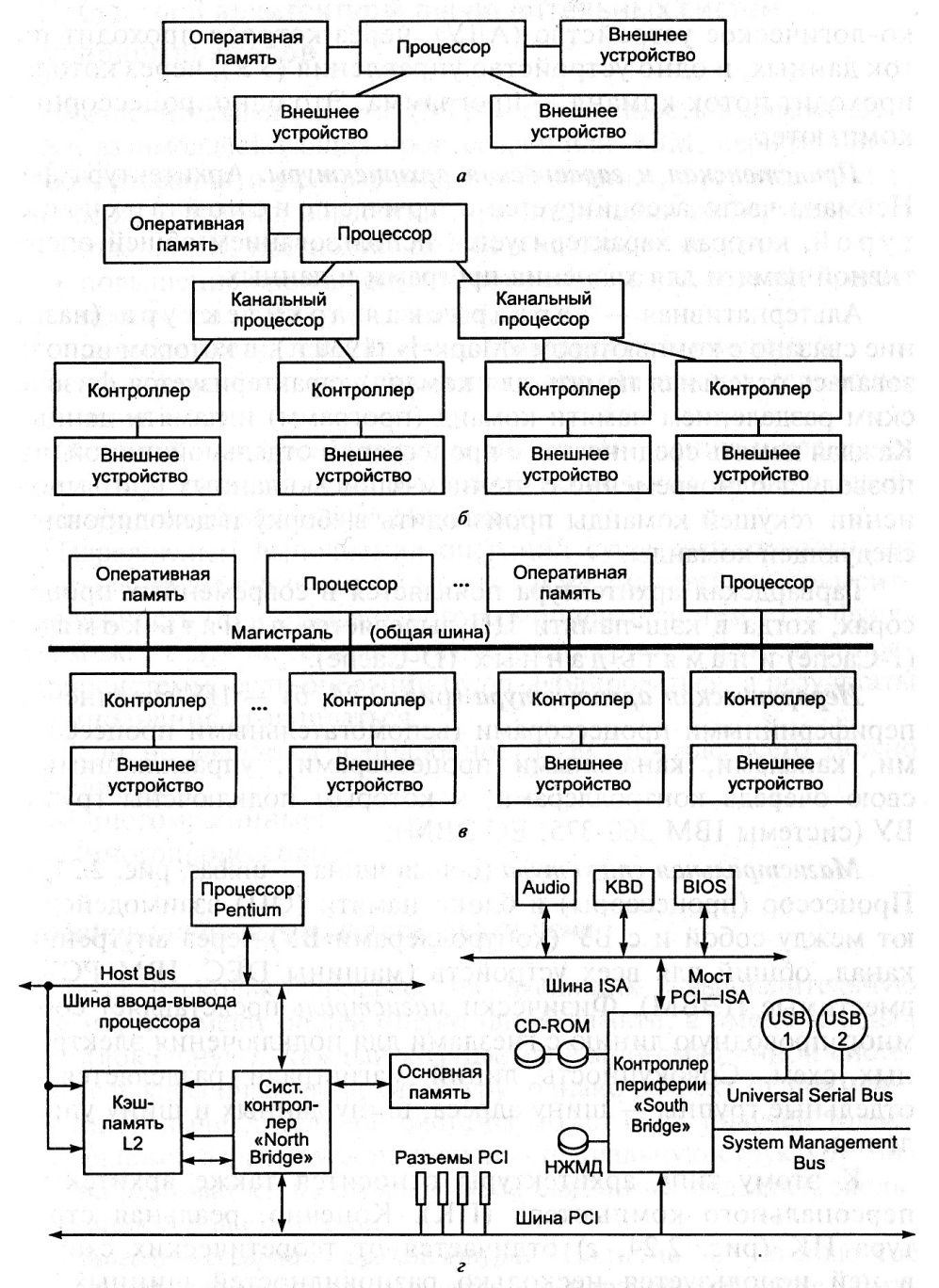

Архитектура "звезда". Здесь процессор (ЦУ) (рис.1.3.2, а) соединен непосредственно в ВУ и управляет их работой (ранние модели машин). Этот тип также именуется классическая архитектура - одно арифметико-логическое устройство (АЛУ), через которое проходит поток данных, и одно устройство управления (УУ), через которое проходит поток команд - программа. Это однопроцессорный компьютер.

Рис. 1.3.2. Основные классы архитектур ЭВМ: а - централизованная; б - иерархическая; в - магистральная; г - общая структура персонального компьютера (архитектураTriton 430 TX - Northbridge/ Southbridge)

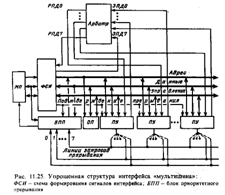

Иерархическая архитектура (рис. 1.3.2, б) - ЦУ соединено с периферийными процессорами (вспомогательными процессорами, каналами, канальными процессорами), управляющими в свою очередь контроллерами, к которым подключены группы ВУ (система IBM 360-375, ЕС ЭВМ).

Магистральная структура (рис. 1.3.2, в). Процессор (процессоры) и блоки памяти (ОП) взаимодействуют между собой и с ВУ (контроллерами ВУ) через внутренний канал, общий для всех устройств (машины DEC, IBM PC-совместимые ПЭВМ). Физически магистраль представляет собой многопроходную линию с гнездами для подключения электронных схем. Совокупность линий магистрали разделяется на отдельные группы - шину адреса, шину данных и шину управления.

К этому типу архитектуры относится также архитектура персонального компьютера (ПК). Конечно реальная структура ПК (рис.1.3.2, г) отличается от теоретических схем - в ней используется несколько разновидностей шинных интерфейсов, которые соединяются между собой мостами - контроллерами памяти и периферийных устройств.

Классы и архитектуры вычислительных систем и суперкомпьютеров.

Вычислительная система (ВС)- совокупность взаимосвязанных и взаимодействующих процессоров или ЭВМ, периферийного оборудования и программного обеспечения, предназначенная для сбора хранения, обработки и распределения информации.

-

Создание ВС преследует следующие основные цели:

-

повышение производительности системы за счет ускорения процессов обработки данных;

-

повышение надежности и достоверности вычислений;

-

предоставление пользователям дополнительных сервисных услуг и.т.д.

Отличительной особенностью ВС по отношению к классическим ЭВМ является наличие в ней нескольких вычислителей, реализующих параллельную обработку.

-

ВС можно разделить на:

-

многомашинные;

-

многопроцессорные.

Многомашинная вычислительная система.

Здесь несколько процессоров, входящих в вычислительную систему, не имеют общей оперативной памяти, а имеют каждый свою (локальную). Каждый компьютер в многомашинной системе имеет классическую архитектуру, однако эффект от применения такой вычислительной системы может быть получен только при решении задач, имеющих очень специальную структуру: она должна разбиваться на столько слабо связанных подзадач, сколько компьютеров в системе.

Многопроцессорная архитектура.

Наличие в компьютере нескольких процессоров означает, что параллельно может быть организовано много потоков данных и много потоков команд. Таким образом, параллельно могут выполняться несколько фрагментов одной задачи. Преимущество в быстродействии многопроцессорных и многомашинных вычислительных систем перед однопроцессорными очевидно.

Архитектура с параллельными процессорами.

Здесь несколько АЛУ работают под управлением одного УУ. Это означает, что множество данных может обрабатываться по одной программе, т.е. по одному потоку команд. Высокое быстродействие такой архитектуры можно получить только на задачах, в которых одинаковые вычислительные операции выполняются одновременно на различных однотипных наборах данных.

Принципы (архитектура) фон Неймана

В 1946 году Д. фон Нейман, Г. Голдстайн и А. Беркс в своей совместной статье изложили новые принципы построения и функционирования ЭВМ. В последствие на основе этих принципов производились первые два поколения компьютеров. В более поздних поколениях происходили некоторые изменения, хотя принципы Неймана актуальны и сегодня.

По сути, Нейману удалось обобщить научные разработки и открытия многих других ученых и сформулировать на их основе принципиально новое.

Принципы фон Неймана

-

Использование двоичной системы счисления в вычислительных машинах. Преимущество перед десятичной системой счисления заключается в том, что устройства можно делать достаточно простыми, арифметические и логические операции в двоичной системе счисления также выполняются достаточно просто.

-

Программное управление ЭВМ. Работа ЭВМ контролируется программой, состоящей из набора команд. Команды выполняются последовательно друг за другом. Созданием машины с хранимой в памяти программой было положено начало тому, что мы сегодня называем программированием.

-

Память компьютера используется не только для хранения данных, но и программ. При этом и команды программы и данные кодируются в двоичной системе счисления, т.е. их способ записи одинаков. Поэтому в определенных ситуациях над командами можно выполнять те же действия, что и над данными.

-

Ячейки памяти ЭВМ имеют адреса, которые последовательно пронумерованы. В любой момент можно обратиться к любой ячейке памяти по ее адресу. Этот принцип открыл возможность использовать переменные в программировании.

-

Возможность условного перехода в процессе выполнения программы. Не смотря на то, что команды выполняются последовательно, в программах можно реализовать возможность перехода к любому участку кода.

Самым главным следствием этих принципов можно назвать то, что теперь программа уже не была постоянной частью машины (как например, у калькулятора). Программу стало возможно легко изменить. А вот аппаратура, конечно же, остается неизменной, и очень простой.

Для сравнения, программа компьютера ENIAC (где не было хранимой в памяти программы) определялась специальными перемычками на панели. Чтобы перепрограммировать машину (установить перемычки по-другому) мог потребоваться далеко не один день. И хотя программы для современных компьютеров могут писаться годы, однако они работают на миллионах компьютеров после несколько минутной установки на жесткий диск.

Как работает машина фон Неймана

Машина фон Неймана состоит из запоминающего устройства (памяти) - ЗУ, арифметико-логического устройства - АЛУ, устройства управления - УУ, а также устройств ввода и вывода.

Программы и данные вводятся в память из устройства ввода через арифметико-логическое устройство. Все команды программы записываются в соседние ячейки памяти, а данные для обработки могут содержаться в произвольных ячейках. У любой программы последняя команда должна быть командой завершения работы.

Команда состоит из указания, какую операцию следует выполнить (из возможных операций на данном «железе») и адресов ячеек памяти, где хранятся данные, над которыми следует выполнить указанную операцию, а также адреса ячейки, куда следует записать результат (если его требуется сохранить в ЗУ).

Арифметико-логическое устройство выполняет указанные командами операции над указанными данными.

Из арифметико-логического устройства результаты выводятся в память или устройство вывода. Принципиальное различие между ЗУ и устройством вывода заключается в том, что в ЗУ данные хранятся в виде, удобном для обработки компьютером, а на устройства вывода (принтер, монитор и др.) поступают так, как удобно человеку.

УУ управляет всеми частями компьютера. От управляющего устройства на другие устройства поступают сигналы «что делать», а от других устройств УУ получает информацию об их состоянии.

Управляющее устройство содержит специальный регистр (ячейку), который называется «счетчик команд». После загрузки программы и данных в память в счетчик команд записывается адрес первой команды программы. УУ считывает из памяти содержимое ячейки памяти, адрес которой находится в счетчике команд, и помещает его в специальное устройство - «Регистр команд». УУ определяет операцию команды, «отмечает» в памяти данные, адреса которых указаны в команде, и контролирует выполнение команды. Операцию выполняет АЛУ или аппаратные средства компьютера.

В результате выполнения любой команды счетчик команд изменяется на единицу и, следовательно, указывает на следующую команду программы. Когда требуется выполнить команду, не следующую по порядку за текущей, а отстоящую от данной на какое-то количество адресов, то специальная команда перехода содержит адрес ячейки, куда требуется передать управление.

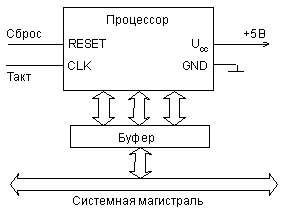

Процессор, структура и функционирование

Процессоробычно представляет собой отдельную микросхему или же часть микросхемы (в случае микроконтроллера).

Микросхема процессора обязательно имеет следующие выводы:

- шины адреса,

- шины данных

- шины управления.

- вывод внешнего тактового сигнала или кварцевого резонатора (CLK), так как процессор всегда представляет собой тактируемое устройство.

- вывод сигнал начального сброса RESET. При включении питания, при аварийной ситуации или зависании процессора подача этого сигнала приводит к инициализации процессора, заставляет его приступить к выполнению программы начального запуска.

- шина питания - обычно имеет одно напряжение питания (+5 В или +3,3 В) и общий провод ("землю").

Иногда некоторые сигналы и шины мультиплексируются, чтобы уменьшить количество выводов микросхемы процессора.

Важнейшие характеристики процессора:

- разрядность шины данных, определяет скорость работы системы;

- разрядность его шины адреса, определяет допустимую сложность системы;

- количество управляющих сигналов в шине управления; определяет разнообразие режимов обмена и эффективность обмена процессора с другими устройствами системы.

Чем больше тактовая частота процессора, тем он быстрее работает, то есть тем быстрее выполняет команды. Впрочем, быстродействие процессора определяется не только тактовой частотой, но и особенностями его структуры. Современные процессоры выполняют большинство команд за один такт и имеют средства для параллельного выполнения нескольких команд. Тактовая частота процессора имеет нижний и верхний пределы. При превышении верхнего предела частоты возможно перегревание процессора, а также сбои, причем, что самое неприятное, возникающие не всегда и нерегулярно. Так что с изменением этой частоты надо быть очень осторожным.

Рисунок 2.4 - Схема включения процессора

После включения питания процессор переходит в первый адрес программы начального пуска и выполняет эту программу. Данная программа предварительно записана в постоянную (энергонезависимую) память. После завершения программы начального пуска процессор начинает выполнять основную программу, находящуюся в постоянной или оперативной памяти, для чего выбирает по очереди все команды. От этой программы процессор могут отвлекать внешние прерывания или запросы на ПДП. Команды из памяти процессор выбирает с помощью циклов чтения по магистрали. При необходимости процессор записывает данные в память или в устройства ввода/вывода с помощью циклов записи или же читает данные из памяти или из устройств ввода/вывода с помощью циклов чтения.

Таким образом, основные функции любого процессора следующие:

- выборка (чтение) выполняемых команд;

- ввод (чтение) данных из памяти или устройства ввода/вывода;

- вывод (запись) данных в память или в устройства ввода/вывода;

- обработка данных (операндов), в том числе арифметические операции над ними;

- адресация памяти, то есть задание адреса памяти, с которым будет производиться обмен;

- обработка прерываний и режима прямого доступа.

Упрощенно структуру микропроцессора можно представить в следующем виде (рис. 2.5).

Рисунок 2.5 - Внутренняя структура микропроцессора.

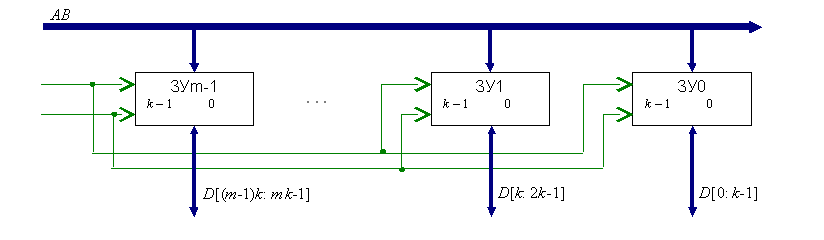

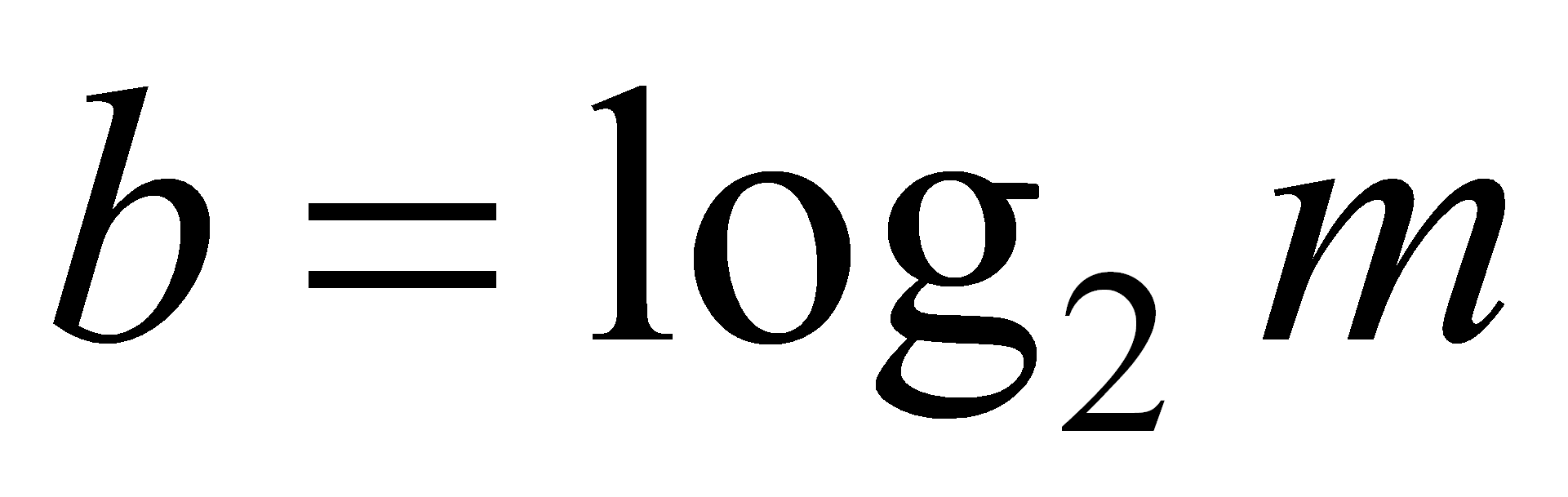

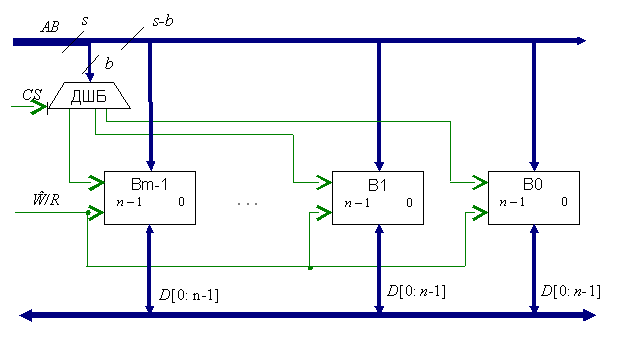

Основные функции узлов процессора приведены ниже.