- Преподавателю

- Другое

- Методические указания к выполнению ЛПЗ по Основам электроники и цифровой схемотехники

Методические указания к выполнению ЛПЗ по Основам электроники и цифровой схемотехники

| Раздел | Другое |

| Класс | - |

| Тип | Другие методич. материалы |

| Автор | Плаксо В.А. |

| Дата | 02.10.2014 |

| Формат | doc |

| Изображения | Есть |

ОТДЕЛЕНИЕ Ресурсный центр Транспорта. Москва, ул. Басовская, 12 ПЦК (КМК) по укрупненной группе СПО/НПО 230000 Информатике и вычислительная техника

УТВЕРЖДАЮ

Зам. директора по УМР

_________________________Бозрова И.Г.

МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПО ПРОВЕДЕНИЮ

ЛАБОРАТОРНЫХ И ПРАКТИЧЕСКИХ РАБОТ

Дисциплина (Профессиональный модуль)

ОП.03 Основы электроники и цифровой схемотехники

для профессии 230103.04 Наладчик аппаратного и программного обеспечения

Разработчик(и): Плаксо Виктор Александрович, преподаватель

Методические рекомендации рассмотрены и одобрены на заседании ПЦК (КМК) по укрупненной группе СПО/НПО 230000 Информатика и вычислительная техника

протокол №___ от «__»_______ 201_ г. Председатель ПЦК_____Сивцова Е.Г.

Содержание

1. Пояснительная записка

2. Правила проведения лабораторных и практических работ

3. Паспорт фонда оценочных средств

4. Состав КОС для текущего контроля знаний, умений обучающихся по учебной дисциплине/ разделам

5. Лабораторная работа №1 Ознакомление с передатчиками электрических сигналов

6. Практическая работа №1 «Определение значения логической функции и составление таблиц истинности и временных диаграмм»

7. Практическая работа №2 «Минимизация булевых функций. Метод непосредственных преобразований»

8. Практическая работа №3 «Решение задач по выполнению условий, с дальнейшим построением схем логических функций»

9. Практическая работа №4 «Исследование работы триггерных схем»

10. Практическая работа №5 «Исследование работы регистров хранения и сдвига»

11.Практическая работа №6 «Исследования работы двоичных и двоично - десятичных счетчиков»

12. Практическая работа №7 «Исследование работы дешифраторов и шифраторов. Реализация логических функций на дешифраторах»

13. Практическая работа №8 «Исследование работы мультиплексоров и демультиплексоров»

14. Практическая работа №9 «Исследование работы сумматоров»

15. Лабораторная работа №2 «Исследование работы цифро-аналогового преобразователя (ЦАП)»

16. Лабораторная работа №3 «Исследование работы оперативного запоминающего устройства»

17. Критерии оценки лабораторных и практических работ

18. Информационное обеспечение обучения

19. Список литературы

1. Пояснительная записка

Дисциплина «Основы электроники и цифровой схемотехники» входит в цикл общепрофессиональных дисциплин для профессии 230103.04 Наладчик аппаратного и программного обеспечения. Данные методические рекомендации предназначены для учащихся, изучающие данную дисциплину, и включает в себя три лабораторных работы и девять практических работ.

Данные методические рекомендации входят в состав контрольно-оценочных средств по дисциплине и предполагают формирование у учащихся знаний и умений в области электроники и схемотехники.

2. Правила проведения практических занятий

1.Обучающийся должен подготовить ответы на теоретические вопросы к ЛР или ПЗ;

2.Перед началом каждого занятия проверяется готовность обучающегося к ЛР или ПЗ;

3.После завершения ЛР или ПЗ обучающийся должен сдать преподавателю отчет о проделанной работе, выполненной в тетради;

4.Обучающийся, пропустивший ЛР или ПЗ по уважительной или неуважительной причинам, обязан выполнить задания ЛР или ПЗ в дополнительно назначенное время.

5.Оценка за выполненные задания обучающемуся выставляется с учетом предварительной подготовки к занятию, доли самостоятельности при выполнении расчетов, точности и грамотности оформления отчета.

-

ПАСПОРТ

ФОНДА ОЦЕНОЧНЫХ СРЕДСТВ

по учебной дисциплине

Основы электроники и цифровой схемотехники

наименование учебной дисциплины

230103.04 Наладчик аппаратного и программного обеспечения

код, наименование профессии/специальности

Результаты обучения

(освоенные умения,

усвоенные знания)

Наименование темы

Уровень освоения

темы

Текущий контроль

Промежуточная аттестация

Наименование

контрольно-оценочного средства

Уровень трудности

Наименование

контрольно-оценочного средства

Уровень трудности

1

2

3

4

5

6

7

1-2

Тема 1.1. Электровакуумные и полупроводниковые приборы

2

Вопросы для устной проверки знаний Лабораторн..раб. №1

2

3-5

Тема 1.2. Волоконно-оптические линии связи

2

Вопросы для устной проверки знаний

2

7

Тема 2.1. Элементная база схемотехники. Логические основы цифровой схемотехники.

2

Тестовые задания

Практич.раб. №1

Практич.раб. №2

Практич.раб. №3

2

8-9

Тема 2.2 Комбинационные и последовательные устройства

2

Вопросы для устной проверки знаний

Практич.раб. №4

Практич.раб. №5

Практич.раб. №6

Практич.раб. №7

Практич.раб. №8

Практич.раб. №9

2

6, 10

Тема 2.3 Запоминающие устройства. Цифро-аналоговые преобразователи (ЦАП) и аналого-цифровые преобразователи (АЦП).

2

Вопросы для устной проверки знаний

Лабораторн..раб. №2

Лабораторн..раб. №3

2

Зачет

Тест

Формируемые знания и умения:

Уметь:

1. идентифицировать полупроводниковые приборы и элементы схемотехники и определять их параметры

Знать:

2. основные сведения об электровакуумных и полупроводниковых приборах, выпрямителях, колебательных системах, антеннах; усилителях, генераторах электрических сигналов;

3. общие сведения о распространении радиоволн;

4. принцип распространения сигналов в линиях связи;

5. сведения о волоконно-оптических линиях;

6. цифровые способы передачи информации;

7. общие сведения об элементной базе схемотехники (резисторы, конденсаторы, диоды, транзисторы, микросхемы, элементы оптоэлектроники);

8. логические элементы и логическое проектирование в базисах микросхем;

9.функциональные узлы (дешифраторы, шифраторы, мультиплексоры, демультиплексоры, цифровые компараторы, сумматоры, триггеры, регистры, счетчики);

10. цифро-аналоговые и аналогово-цифровые преобразователи.

-

Состав КОС

для текущего контроля знаний, умений обучающихся

по учебной дисциплине/ разделам и темам

№

п/п

Наименование КОС

Материалы для преставления

в ФОС

Раздел 1 Тема1 «Электровакуумные и полупроводниковые приборы»

1

Вопросы для устного опроса по теме.

Перечень вопросов

по теме (Приложение 1)

2

Лабораторная работа №1 «Ознакомление с передатчиками электрических сигналов»

Методическая разработка лабораторной работы (Приложение 2)

Раздел 1 Тема2 «Волоконно-оптические линии связи»

1

Вопросы для устного опроса по теме.

Перечень вопросов

по теме (Приложение 3)

Раздел 2 Тема1 «Элементная база схемотехники. Логические основы цифровой схемотехники»

1

Тест по теме

Тест по теме (Приложение 4)

2

Практическая работа №1 «Определение значения логической функции и составление таблиц истинности и временных диаграмм»

Методическая разработка практического занятия (Приложение 5)

3

Практическая работа №2 «Минимизация булевых функций. Метод непосредственных преобразований»

Методическая разработка практического занятия (Приложение 6)

4

Практическая работа №3 «Решение задач по выполнению условий, с дальнейшим построением схем логических функций»

Методическая разработка практического занятия (Приложение 7)

Раздел 2 Тема2 «Комбинационные и последовательные устройства»

1

Вопросы для письменного опроса по теме

Перечень вопросов

по теме (Приложение 8)

2

Практическая работа №4 «Исследование работы триггерных схем»

Методическая разработка практического занятия (Приложение 9)

3

Практическая работа №5 «Исследование работы регистров хранения и сдвига»

Методическая разработка практического занятия (Приложение 10)

4

Практическая работа №6 «Исследования работы двоичных и двоично - десятичных счетчиков»

Методическая разработка практического занятия (Приложение 11)

5

Практическая работа №7 «Исследование работы дешифраторов и шифраторов. Реализация логических функций на дешифраторах»

Методическая разработка практического занятия (Приложение 12)

6

Практическая работа №8 «Исследование работы мультиплексоров и демультиплексоров»

Методическая разработка практического занятия (Приложение 13)

7

Практическая работа №9 «Исследование работы сумматоров»

Методическая разработка практического занятия (Приложение 14)

Раздел 2 Тема3 «Запоминающие устройства. Цифро-аналоговые преобразователи (ЦАП) и аналого- цифровые преобразователи (АЦП)»

1

Вопросы для письменного опроса по теме

Перечень вопросов

по теме (Приложение 15)

2

Лабораторная работа №2 «Исследование работы цифро- аналогового преобразователя (ЦАП)»

Методическая разработка лабораторной работы (Приложение 16)

3

Лабораторная работа №3 «Исследование работы оперативного запоминающего устройства и флэш- памяти»

Методическая разработка лабораторной работы (Приложение 17)

Лабораторная работа №1

Ознакомление с передатчиками электрических сигналов

Цель работы: ознакомить учащихся с передатчиками электрических сигналов.

Пояснения к работе

Для передачи электрических сигналов между двумя точками необходимо организовать замкнутую электрическую цепь, соединяющую передатчик и приемник. Очевидно, что для связи двух точек необходимо иметь по крайней мере два проводника. Сигналы оп проводам могут передаваться как в потенциальном представлении, так и в токовом.

При потенциальном представлении информативным является уровень напряжения сигнала, переданный передатчиком и полученный приемником. Передача с потенциальным представлением может быть как асимметричной, так и симметричной. При асимметричной передаче один из проводов, соединяющих узлы называют общим - его потенциал относительно земли остается более или менее постоянным. Информативным (полезным сигналом) является потенциал на сигнальном проводе относительно общего провода. Например, классическая реализация Ethernet на коаксиальном кабеле. При симметричной, или дифференциальной, или балансной, передаче оба провода являются равноправными, а информативна разность потенциалов между ними. Симметрия подразумевает совпадение характеристик цепей для обоих проводников. Примером симметричной передачи является Ethernet на витой паре.

Передаваемые по проводам сигналы могут иметь и токовое представление - здесь информативно наличие или отсутствие тока в цепи. Токовое представление при небольшой пропускной способности (до 10кбит/с) обеспечивает большую дальность связи - до нескольких километров. Примером может являться городская телефонная сеть.

Для передачи сигналов используются две основные разновидности кабеля - коаксиальный кабель и витые пары проводников. Коаксиальный кабель используется для асимметричной передачи, витая пара - для симметричной (балансной).

Кабель имеет набор параметров, распределенных по всей его длине: емкость и сопротивление изоляции проводниками, индуктивность и сопротивление проводников. Эти параметры определяют частотные свойства кабеля, а также скорость распространения электрического сигнала вдоль линии.

Важным параметром кабеля является его волновое сопротивление, называемое его характеристическим импедансом, которое является комплексной величиной и измеряется в омах. Волновое сопротивление, или импеданс, непосредственно не связано ни с активным сопротивлением проводников, которое легко измеряется омметром, ни с сопротивлением изоляции, которое измеряется мегомметром. Импеданс в основном зависит от геометрии проводников кабеля и диэлектрической проницаемости материала изоляции.

рис. 1.

Рассмотрим процесс распространения сигнала в отрезке однородной линии (рис. 1). Пусть на конце A расположен источник сигнала, а на конце B - приемник. Одиночный импульс, посланный передатчиком, начнет распространяться вдоль линии с характерной для данного кабеля скоростью. Скорость распространения сигнала обычно лежит в пределах 60-80% от скорости света в вакууме. По мере распространения сигнала в линии происходит его затухание - часть энергии рассеивается в виде потерь. Затухание Att принято измерять в децибелах(дБ).

Att = -10*lg(PВ/PА) = -20*lg(UВ/UA),

Где PВ - мощность переданного сигнала, PA - мощность принятого сигнала, а UВ и UA - напряжения в точках A и B. Значение затухания, определенного поданной формуле всегда положительное, поскольку PВ < PА . Затухание 6дБ соответствует падению амплитуды сигнала вдове, 20дБ - в 10 раз. Кабели могут характеризоваться и погонным затуханием дБ/м. Чем меньше затухание - тем лучше кабель. С повышением частоты затухание увеличивается. К аномалиям импеданса приводят нарушения геометрии проводников (резкие изгибы, передавливания) и изоляции, применение отрезков кабеля с разными значениями импеданса. На концах отрезка источниками отражения сигнала могут и разъемы, если их импеданс не соответствует импедансу кабеля. Соединяемые кабелем устройства должны иметь соответствующий импеданс - при этом вся энергия передатчика будет уходить в линию, а приемник получит всю энергию, дошедшую до него по линии.

Мерой степени согласованности импеданса является ослабление отраженного сигнала, или возвратные потери RL. Как и затухание этот параметр измеряется в децибелах.

RL = -20*lg(URA/UA),

Где UA - амплитуда переданного сигнала, URA - амплитуда отраженного сигнала на конце А. Большое значение RL означает лучшее согласование кабеля с оконечными элементами линии.

Рассмотрим ситуацию, когда рядом проходят две линии связи. Причем одна используется при передачи в направлении от A к B, а другая - в обратном.

рис. 2.

При передаче сигнала от A к B по паре 1 за сет паразитных емкостных и индуктивных связей между парами, в паре 2 наводится сигнал перекрестной помехи. Этот сигнал можно наблюдать на обоих концах кабеля. Мерой этой помехи, называемой перекрестной, является ослабление перекрестной помехи на ближнем конце - NEXT.

NEXT = -20*lg(UXA/UA),

Где UA - амплитуда переданного сигнала, UXA - амплитуда помехи на конце А. Чем большое значение NEXT - тем лучше кабель, меньше перекрестных помех.

Для кабеля, имеющего более двух пар, параметр NEXT измеряют между всеми комбинациями пар и приводят наихудшее значение. Кроме того, параметр NEXT может быть и асимметричным - различаться при измерении с различных концов. Это относится не к отдельно взятому отрезку кабеля, а к кабельной линии, которая может состоять из нескольких отрезков и пассивных средств их соединения. Поэтому, при проверке кабельного соединения NEXT измеряется с двух концов и берется наихудшее значение.

Стандартное определение NEXT исходит из того, что в кабеле в одном направлении в одно время передача данных идет по одной паре. В случае применения многопарного кабеля, перекрестная помеха будет наводиться от нескольких источников. Для нормальной работы в таком случае должен быть запас по параметру NEXT, определяемый как

NEXT = 6 + 10*lg(n+1),

где n - число кабельных единиц, примыкающих к той кабельной единице, для которой определяют NEXT.

Критерием возможности использования кабельного соединения для двустороннего трафика является параметр ACR - отношение затухания сигнала к ослаблению перекрестной помехи.

ACR = NEXT - Att

Параметр ACR можно трактовать как отношение сигнал/шум. Положительное значение ACR означает превышение уровня полезного сигнала над уровнем помехи. Отрицательное значение ACR означает, что полезный сигнал меньше помехи, при этом его распознавание становится проблематичным. ACR зависит от частоты и с ее повышением понижается. Частота, на которой ACR переходит через ноль в отрицательное значение, считается предельно допустимой частотой при использовании данного кабеля. Для относительно надежной работы ACR на максимальной рабочей частоте должен быть не менее +2…+4 дБ.

Задание

Рассчитать по формуле затухания Att степень затухания при известных напряжениях в точках А и В.

Необходимые принадлежности

-

Компьютер

Программа EWB (Electronics Workbench)

Работа в лаборатории

-

Изучить теоретический материал по данной теме;

-

Изучить формулу нахождения затухания Att;

-

Изучить формулу нахождения возвратных потерь RL;

-

Изучить формулу нахождения ослабления перекрестной помехи на ближнем конце - NEXT;

-

Изучить формулу нахождения ACR - отношения затухания сигнала к ослаблению перекрестной помехи;

-

На основе проведенных вычислений занести результаты в таблицу.

-

Параметр

Att

RL

NEXT

ACR

Значение

Практическая работа №1 «Определение значения логической функции и составление таблиц истинности и временных диаграмм»

Цель: Исследовать работу логических элементов и их комбинаций.

Теоретическая часть.

Структурной основой любого цифрового вычислительного устройства являются логические элементы и их комбинации. Информация, обрабатываемая цифровыми устройствами, описывается логическими переменными. Их обозначают буквами А, В и т.д., которые могут принимать значения цифр 0 и 1 двоичной системы счисления. От переменных образуются простые логические функции: инверсия (А=В) - НЕ, дизъюнкция (А+В=С) - ИЛИ, конъюнкция (С=А*В) - И, а также сложные функции ИЛИ - НЕ , И - НЕ. Наиболее удобным является способ задания функции в виде таблиц истинности логических функций. Используя два сигнала высокого и низкого уровня, например, напряжения, можно строить простые логические элементы на полупроводниковой базе.

Порядок выполнения работы.

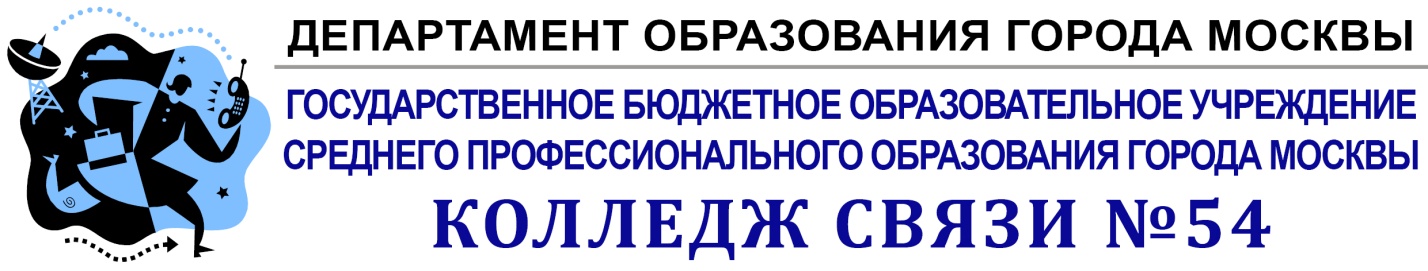

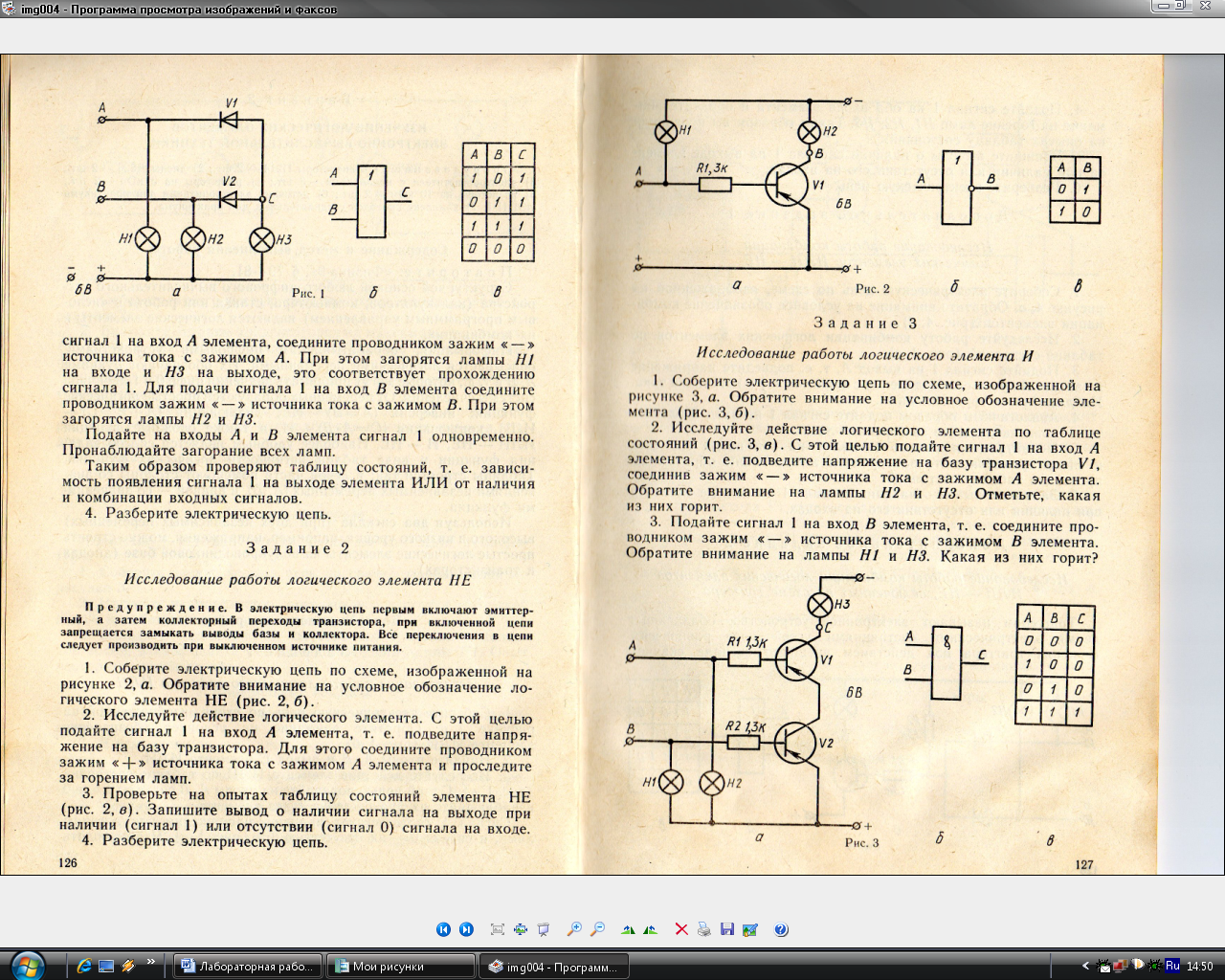

Задание 1. Исследование работы логического элемента ИЛИ.

-

Соберите электрическую цепь по схеме, изображенной на рисунке 1,а. Обратите внимание на условное обозначение элемента ИЛИ (рис. 1,б). (Н1, Н2, Н3 - 10Вт, 6В; R1, R2 - 1кОм).

-

Исследуйте действие элемента ИЛИ по таблице состояний (рис. 1,в). С этой целью подавайте на входы А, В сигналы 1 или 0 и наблюдайте их прохождение через элемент. Сигнал 1 соответствует наличию напряжения или горению ламп, а сигнал 0 - их отсутствию. Чтобы подать сигнал 1 на вход А элемента, соедините проводником зажим «-» источника тока с зажимом А. При этом загорятся лампы Н1 на входе и Н3 на выходе, это соответствует прохождению сигнала 1. Для подачи сигнала 1 на вход В элемента соедините проводником зажим «- » источника тока с зажимом В. При этом загорятся лампы Н2 и Н3. Подайте на входы А и В элемента сигнал 1 одновременно. Пронаблюдайте загорание всех ламп. Таким образом проверяют таблицу состояний, т.е. зависимость появления сигнала 1 на выходе элемента ИЛИ от наличия и комбинации входных сигналов.

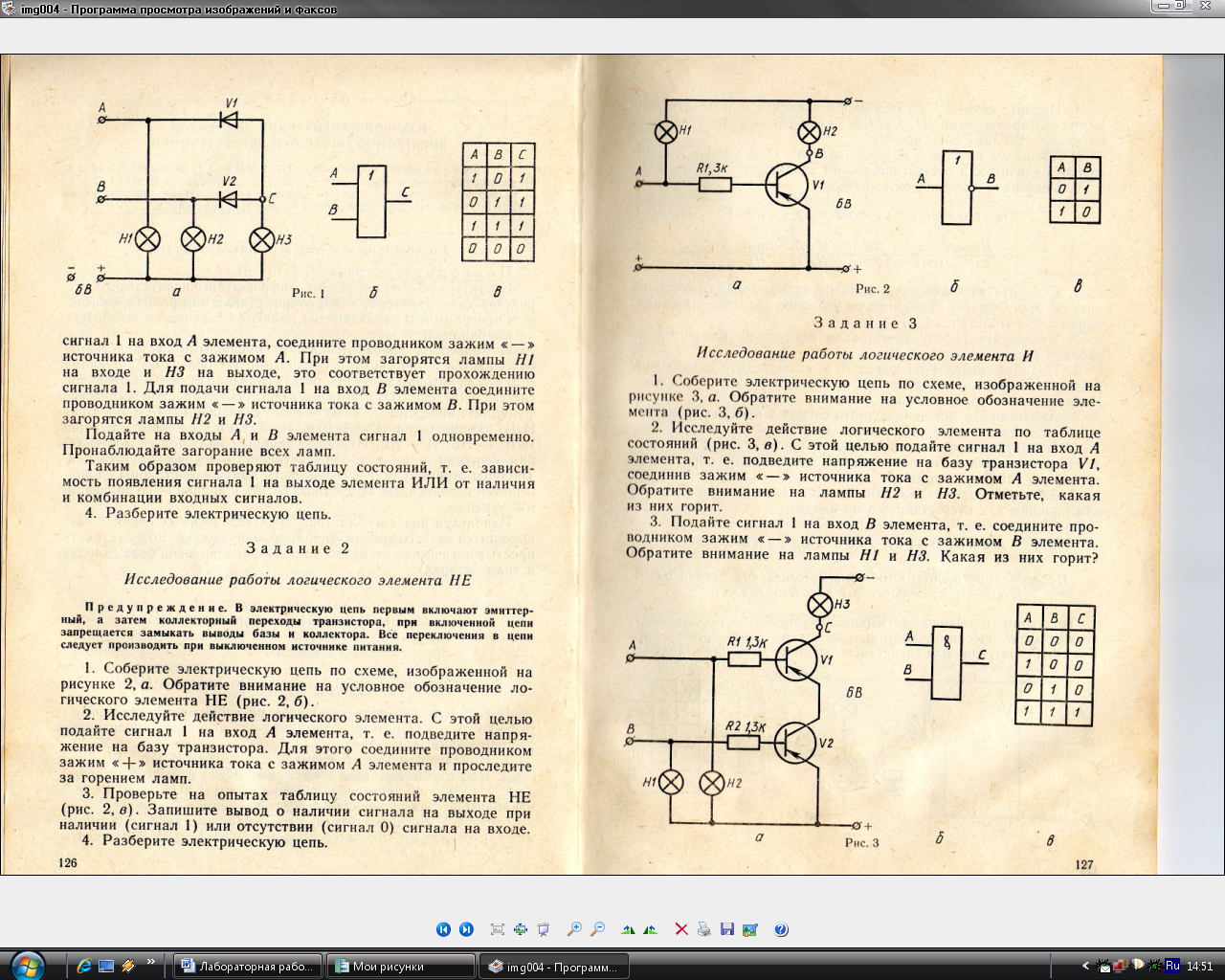

Задание 2. Исследование работы логического элемента НЕ.

-

Соберите электрическую цепь по схеме, изображенной на рисунке 2,а. Обратите внимание на условное обозначение логического элемента НЕ. (Н1 - 10Вт, 6В; Н2 - 2Вт, 3В; R1, R2 - 1кОм).

-

Исследуйте действие логического элемента. С этой целью подайте сигнал 1 на вход А элемента, т.е. подведите напряжение на базу транзистора. Для этого соедините проводником зажим «+» источника с зажимом А элемента и проследите за горением ламп.

-

Проверьте на опытах таблицу состояний элемента НЕ (рис. 2,в). Запишите вывод о наличии сигнала на выходе при наличии (сигнал 1) или отсутствии (сигнал 0) сигнала на входе.

Задание 3. Исследование работы логического элемента И.

-

Соберите электрическую цепь по схеме, изображенной на рисунке 3,а. Обратите внимание на условное обозначение элемента (рис. 3,б). (Н1 и Н2 - 1Вт, 6В; Н3 - 2Вт, 3В; R1, R2 - 1кОм).

-

Исследуйте действие логического элемента по таблице состояний (рис. 3,в). С этой целью подайте сигнал 1 на вход А элемента, т.е. подведите напряжение на базу транзистора V1, соединив зажим «-» источника тока с зажимом А элемента. Обратите внимание на лампы Н2 и Н3. Отметьте, какая из них горит.

-

Подайте сигнал 1 на вход В элемента, т.е. соедините проводником зажим «-» источника тока с зажимом В элемента. Обратите внимание на лампы Н1 и Н3. Какая из них горит?

-

Подайте сигнал 1 на оба входа элемента и обратите внимание на горение ламп Н1, Н2, Н3. Таким образом, вы проверили на опытах таблицу состояний.

-

Запишите выводы о наличии сигнала 1 на выходе элемента при наличии или отсутствии его на входах.

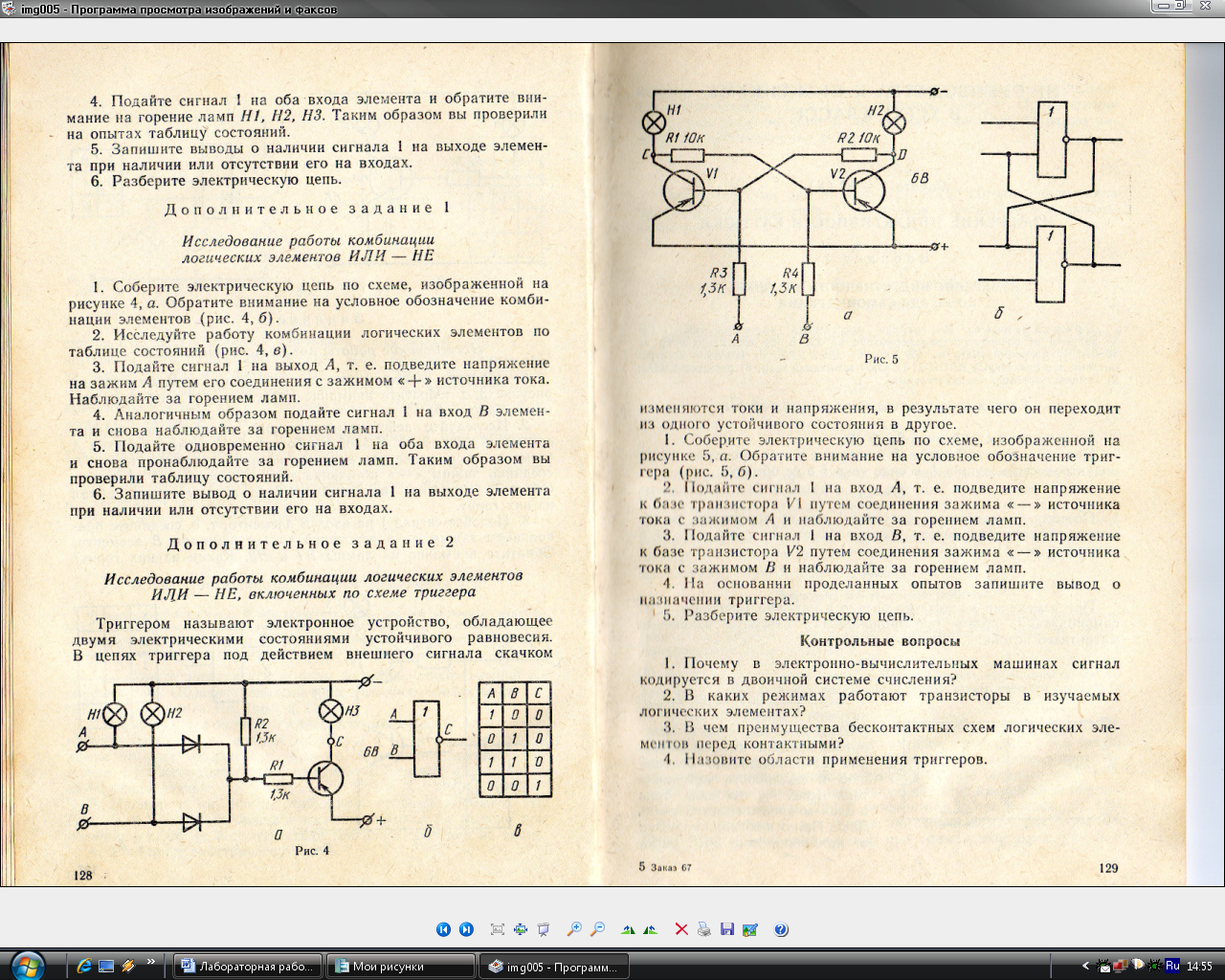

Задание 4. Исследование работы комбинации логических элементов ИЛИ - НЕ.

-

Соберите электрическую цепь по схеме, изображенной на рисунке 4,а. Обратите внимание на условное обозначение комбинации элементов (рис. 4,б). (Н1, Н2 - 10Вт, 12В; Н3 - 2Вт, 3В; R1 - 2 кОм, R2 - 1кОм).

-

Исследуйте работу комбинации логических элементов по таблице состояний (рис. 4,в).

-

Подайте сигнал 1 на вход А, т.е. подведите напряжение на зажим А путем его соединения с зажимом «+» источника тока. Наблюдайте за горением ламп.

-

Аналогичным образом подайте сигнал 1 на вход В элемента и снова наблюдайте за горением ламп.

-

Подайте одновременно сигнал 1 на оба входа элемента и снова пронаблюдайте за горением ламп. Таким образом вы проверили таблицу состояний.

-

Запишите вывод о наличии сигнала 1 на выходе элемента при наличии или отсутствии его на входах.

Задание 5. Исследование работы комбинаций логических элементов.

-

Соберите схеме:

-

Составьте таблицу истинности для данной схемы.

-

Повторите для других комбинаций логических элементов.

Практическая работа №2 «Минимизация булевых функций. Метод непосредственных преобразований»

Задание 1.

Определить МДНФ логической функции устройства.

Составить таблицу соответствия (истинности) функции.

Перевести логическую функцию от табличной к аналитической форме в виде ДСНФ

Найти МДНФ различными методами.

прямым (алгебраическим) преобразованием;

методом Квайна;

усовершенствованным методом Квайна (Квайна-Маккласки);

методом карт Карно;

методом неопределенных коэффициентов;

Задание 2.

Составить алгоритм метода минимизации

2.1 Составить содержательный (словесный) алгоритм минимизации функции, разработать граф-схему алгоритма, разработать логическую схему алгоритма в нотации Ляпунова для метода Квайна.

2.2 Составить содержательный (словесный) алгоритм минимизации функции, разработать граф-схему алгоритма, разработать логическую схему алгоритма в нотации Ляпунова для метода минимального покрытия Петрика.

2.3 Разработать рабочие программы по алгоритмам.

Задание 3.

Синтез схемы логического устройства.

3.1 Выполнить синтез схемы по ДСНФ и МДНФ в базисе Буля с использованием двухвходовых логических элементов и интегральных микросхем серии 155.

3.2 Функцию МДНФ в базисе Буля полученную в первом задании представить в базисах Шеффера и Пирса.

Обосновать выбор базиса по формулам МДНФ.

3.4 Реализовать в выбранном базисе логическую схему.

Задание 4.

4.1 Составить таблицу соответствия (истинности) функции.

Составим таблицу истинности для заданной функции F(X1,X2,X3,X4).

№

X1

X2

X3

X4

F(X1, X2, X3, X4)

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

1

1

0

1

1

1

0

0

1

1

0

0

0

1

Матрицу ДСНФ получают путем удаления тех строк, где функция равна нулю. Для нашего случая получим:

№

X1

X2

X3

X4

0

2

3

5

6

7

10

11

15

0

0

0

0

0

0

1

1

1

0

0

0

1

1

1

0

0

1

0

1

1

0

1

1

1

1

1

0

0

1

1

0

1

0

1

1

4.2Перевести логическую функцию от табличной к аналитической форме в виде ДСНФ.

Переведем логическую функцию от табличной к аналитической форме в виде ДСНФ.

F(X1X2X3X4) = X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4

V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4.

4.3 Метод эквивалентных преобразований.

В основе метода минимизации булевых функций эквивалентными преобразованиями лежит последовательное использование законов булевой алгебры. Метод эквивалентных преобразований целесообразно использовать лишь для простых функций и для количества логических переменных не более 4-х. При большем числе переменных и сложной функции вероятность ошибок при преобразовании возрастает.

Проведем прямое алгебраическое преобразование, используя закон неполного склеивания.

F(X1X2X3X4) = X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V

V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 =

= (X1X2X3X4 V X1X2X3X4) V (X1X2X3X4 V X1X2X3X4)V(X1X2X3X4 V X1X2X3X4) V

V (X1X2X3X4 V X1X2X3X4) V (X1X2X3X4 V X1X2X3X4)V(X1X2X3X4 V X1X2X3X4) V

V (X1X2X3X4 V X1X2X3X4) V (X1X2X3X4 V X1X2X3X4)V(X1X2X3X4 V X1X2X3X4) V

V (X1X2X3X4 V X1X2X3X4) V (X1X2X3X4 V X1X2X3X4) =

= X1X2X4 V X1X2X3 V X1X3X4 V X2X3X4 V X1X3X4 V X2X3X4 V X1X2X4 V

V X1X2X3V X2X3X4 V X1X2X3 V X1X3X4 =

= (X1X2X3 V X1X2X3 V X1X3X4 V X1X3X4) V X1X2X4 V

V (X1X2X3 V X1X2X3 V X2X3X4 V X2X3X4) V X1X2X4 V

V (X1X3X4 V X1X3X4 V X2X3X4 V X2X3X4) =

= X1X3 V X2X3 V X3X4 V X1X2X4 V X1X2X4.

Дальнейшее преобразование невозможно. Полученную функцию можно немного упростить с помощью вынесения за скобки общих переменных.

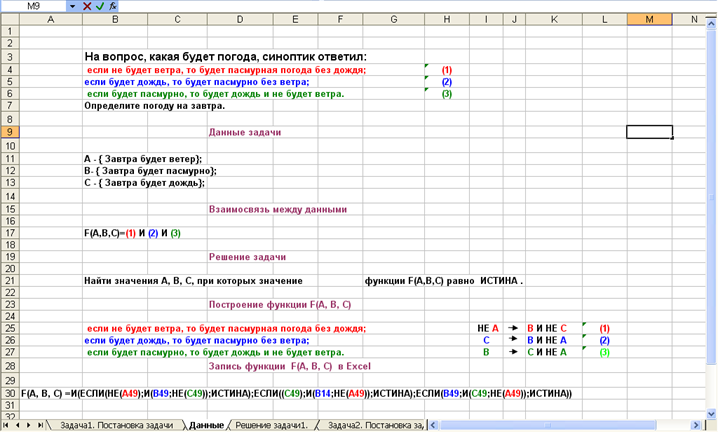

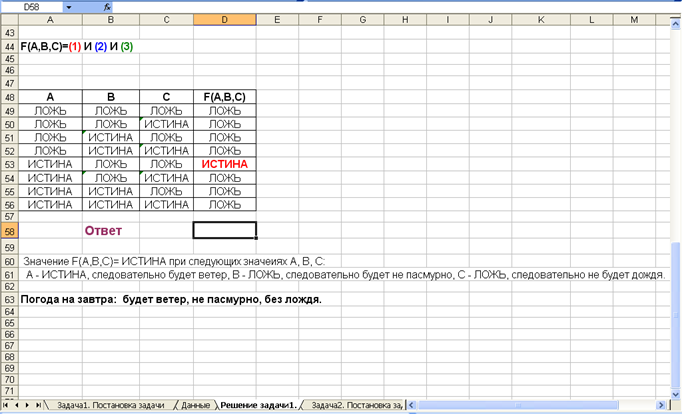

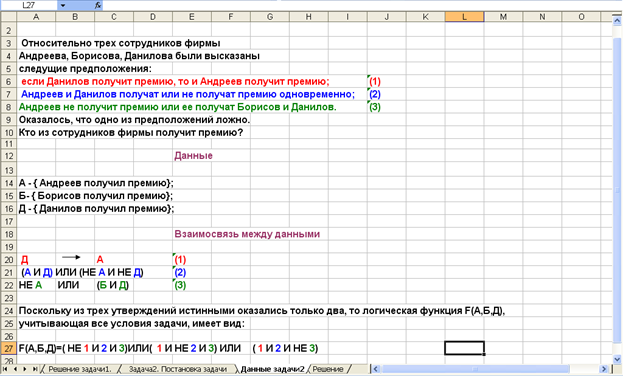

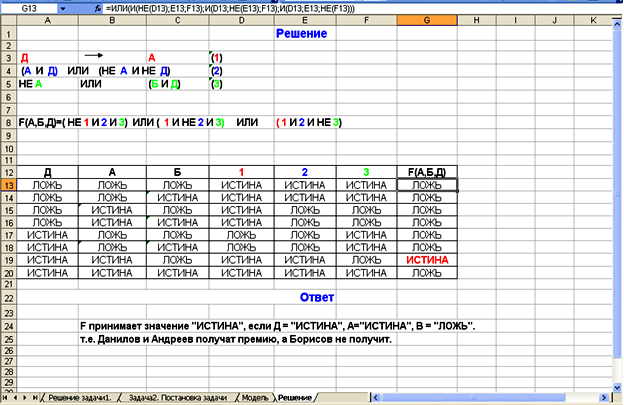

Практическая работа №3 «Решение задач по выполнению условий, с дальнейшим построением схем логических функций»

План решения

-

Обозначить простые высказывания, входящие в условие задачи, буквами (А, В, С,…).

-

Используя логические связи между простыми высказываниями, составить сложные высказывания (условия задачи).

-

Перемножить сложные высказывания, приравняв произведение к 1.

-

Построить таблицу истинности.

-

Записать ответ (выбрать из таблицы истинности при каких значениях простых высказываний логическая функция принимает значение истина).

Задача 1

Задача 2

Практическая работа №4 «Исследование работы триггерных схем»

Цель работы:

Закрепление теоретического материала путем макетирования и экспериментального исследования элементов ЭВМ, а также развитие навыков по сборке и проверке функционирования цифровых схем с помощью современной измерительной аппаратуры.

Теоретическая часть.

Триггеры имеют два устойчивых состояния. Эти состояния определяются по логическим уровням на выходах триггера. Триггер снабжается двумя выходами: прямым Q и инверсным  . Состояние триггера определяет логический уровень на выходе Q. Говорят, что триггер находится в состоянии логической единицы, если на выходе Q уровень напряжения, соответствующий логической единице.

. Состояние триггера определяет логический уровень на выходе Q. Говорят, что триггер находится в состоянии логической единицы, если на выходе Q уровень напряжения, соответствующий логической единице.

Триггеры могут иметь входы различного типа:

R (от англ. RESET) - раздельный вход установки в состояние 0;

S (от англ. SET) - раздельный вход установки в состояние 1;

К - вход установки универсального триггера в состояние 0;

J - вход установки универсального триггера в состояние 1;

V - вход разрешения;

С - синхронизирующий вход;

D - информационный вход;

Т - счетный вход

и некоторые другие.

Обычно название триггера дают по имеющимся у него входам: RS-триггер, JK-триггер, D-триггер и др.

По способу записи информации триггеры подразделяются на асинхронные и синхронные. В асинхронных триггерах состояние на выходе изменяется сразу же после изменения сигнала на информационных входах. В синхронных триггерах для передачи сигнала с информационных входов на выходы требуется специальный синхронизирующий импульс. Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигнала с информационных входов на выходы осуществляется по фронту или по спаду синхронизирующего импульса.

Триггеры относятся к цифровым автоматам. В отличие от комбинационных схем состояние на выходе триггера в данный момент времени определяется не только состояниями на входах триггера в этот же момент времени, но и предыдущим состоянием триггера. Цифровые автоматы, к которым относятся триггеры, иногда называют последовательными схемами.

Триггеры строились по самым разнообразным электрическим схемам. В последнее время триггеры обычно конструируют, используя логические элементы.

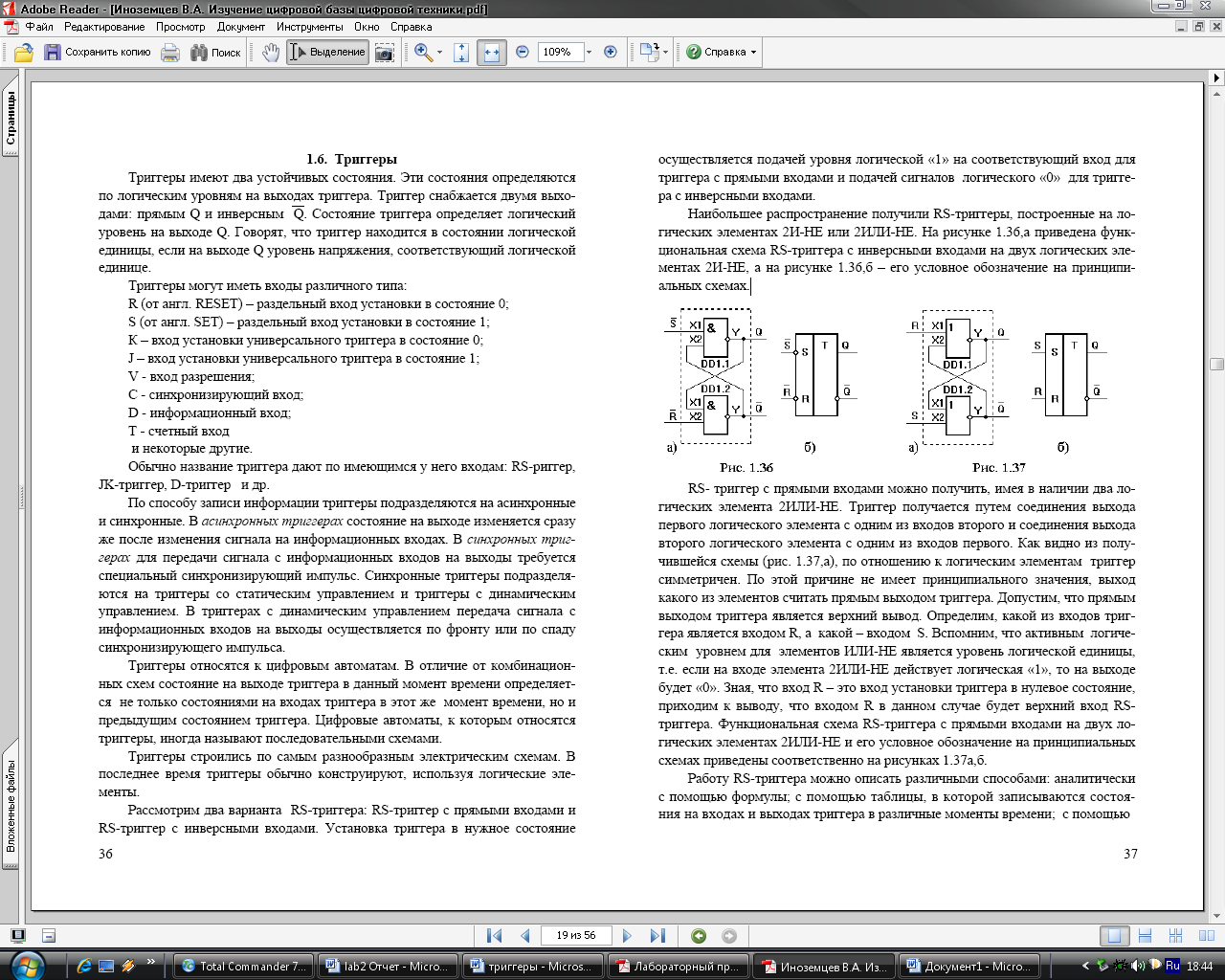

Рассмотрим два варианта RS-триггера: RS-триггер с прямыми входами и RS-триггер с инверсными входами. Установка триггера в нужное состояние осуществляется подачей уровня логической «1» на соответствующий вход для триггера с прямыми входами и подачей сигналов логического «0» для триггера с инверсными входами. Наибольшее распространение получили RS-триггеры, построенные на логических элементах 2И-НЕ или 2ИЛИ-НЕ. На рисунке 1.36,а приведена функциональная схема RS-триггера с инверсными входами на двух логических элементах 2И-НЕ, а на рисунке 1.36,б - его условное обозначение на принципиальных схемах.

RS- триггер с прямыми входами можно получить, имея в наличии два логических элемента 2ИЛИ-НЕ. Триггер получается путем соединения выхода первого логического элемента с одним из входов второго и соединения выхода второго логического элемента с одним из входов первого. Как видно из получившейся схемы (рис. 1.37,а), по отношению к логическим элементам триггер симметричен. По этой причине не имеет принципиального значения, выход какого из элементов считать прямым выходом триггера. Допустим, что прямым выходом триггера является верхний вывод. Определим, какой из входов триггера является входом R, а какой - входом S. Вспомним, что активным логическим уровнем для элементов ИЛИ-НЕ является уровень логической единицы, т.е. если на входе элемента 2ИЛИ-НЕ действует логическая «1», то на выходе будет «0». Зная, что вход R - это вход установки триггера в нулевое состояние, приходим к выводу, что входом R в данном случае будет верхний вход RS-триггера. Функциональная схема RS-триггера с прямыми входами на двух логических элементах 2ИЛИ-НЕ и его условное обозначение на принципиальных схемах приведены соответственно на рисунках 1.37а,б.

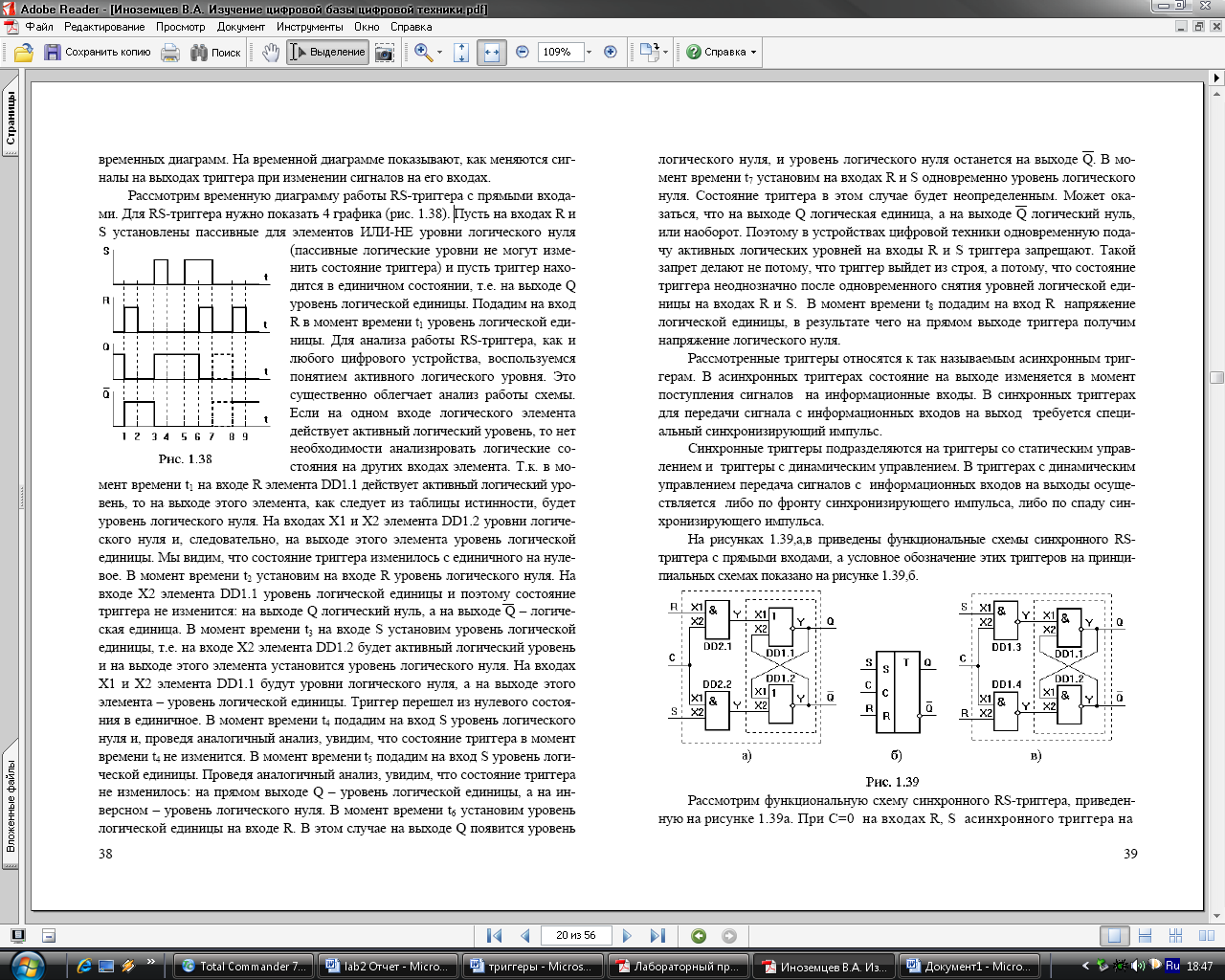

Работу RS-триггера можно описать различными способами: аналитически с помощью формулы; с помощью таблицы, в которой записываются состояния на входах и выходах триггера в различные моменты времени; с помощью временных диаграмм. На временной диаграмме показывают, как меняются сигналы на выходах триггера при изменении сигналов на его входах. Рассмотрим временную диаграмму работы RS-триггера с прямыми входами. Для RS-триггера нужно показать 4 графика (рис. 1.38).

Пусть на входах R и S установлены пассивные для элементов ИЛИ-НЕ уровни логического нуля (пассивные логические уровни не могут изменить состояние триггера) и пусть триггер находится в единичном состоянии, т.е. на выходе Q уровень логической единицы. Подадим на вход R в момент времени t1 уровень логической единицы. Для анализа работы RS-триггера, как и любого цифрового устройства, воспользуемся понятием активного логического уровня. Это существенно облегчает анализ работы схемы. Если на одном входе логического элемента действует активный логический уровень, то нет необходимости анализировать логические состояния на других входах элемента. Т.к. в момент времени t1 на ходе R элемента DD1.1 действует активный логический уровень, то на выходе этого элемента, как следует из таблицы истинности, будет уровень логического нуля. На входах Х1 и Х2 элемента DD1.2 уровни логического нуля и, следовательно, на выходе этого элемента уровень логической единицы. Мы видим, что состояние триггера изменилось с единичного на нуле-вое. В момент времени t в 2 установим на входе R уровень логического нуля. На входе Х2 элемента DD1.1 уровень логической единицы и поэтому состояние триггера не изменится: на выходе Q логический нуль, а на выходе Q - логическая единица. В момент времени t3 на входе S установим уровень логической единицы, т.е. на входе Х2 элемента DD1.2 будет активный логический уровень и на выходе этого элемента установится уровень логического нуля. На входах Х1 и Х2 элемента DD1.1 будут уровни логического нуля, а на выходе этого элемента - уровень логической единицы. Триггер перешел из нулевого состояния в единичное. В момент времени t4 подадим на вход S уровень логического нуля и, проведя аналогичный анализ, увидим, что состояние триггера в момент времени t4 не изменится. В момент времени t5 подадим на вход S уровень логической единицы. Проведя аналогичный анализ, увидим, что состояние триггера не изменилось: на прямом выходе Q - уровень логической единицы, а на инверсном - уровень логического нуля. В момент времени t6 установим уровень логической единицы на входе R. В этом случае на выходе Q появится уровень логического нуля, и уровень логического нуля останется на выходе Q. В момент времени t7 установим на входах R и S одновременно уровень логического нуля. Состояние триггера в этом случае будет неопределенным. Может оказаться, что на выходе Q логическая единица, а на выходе Q логический нуль, или наоборот. Поэтому в устройствах цифровой техники одновременную подачу активных логических уровней на входы R и S триггера запрещают. Такой запрет делают не потому, что триггер выйдет из строя, а потому, что состояние триггера неоднозначно после одновременного снятия уровней логической единицы на входах R и S. В момент времени t8 подадим на вход R напряжение логической единицы, в результате чего на прямом выходе триггера получим напряжение логического нуля.

Рассмотренные триггеры относятся к так называемым асинхронным триггерам. В асинхронных триггерах состояние на выходе изменяется в момент поступления сигналов на информационные входы. В синхронных триггерах для передачи сигнала с информационных входов на выход требуется специальный синхронизирующий импульс.

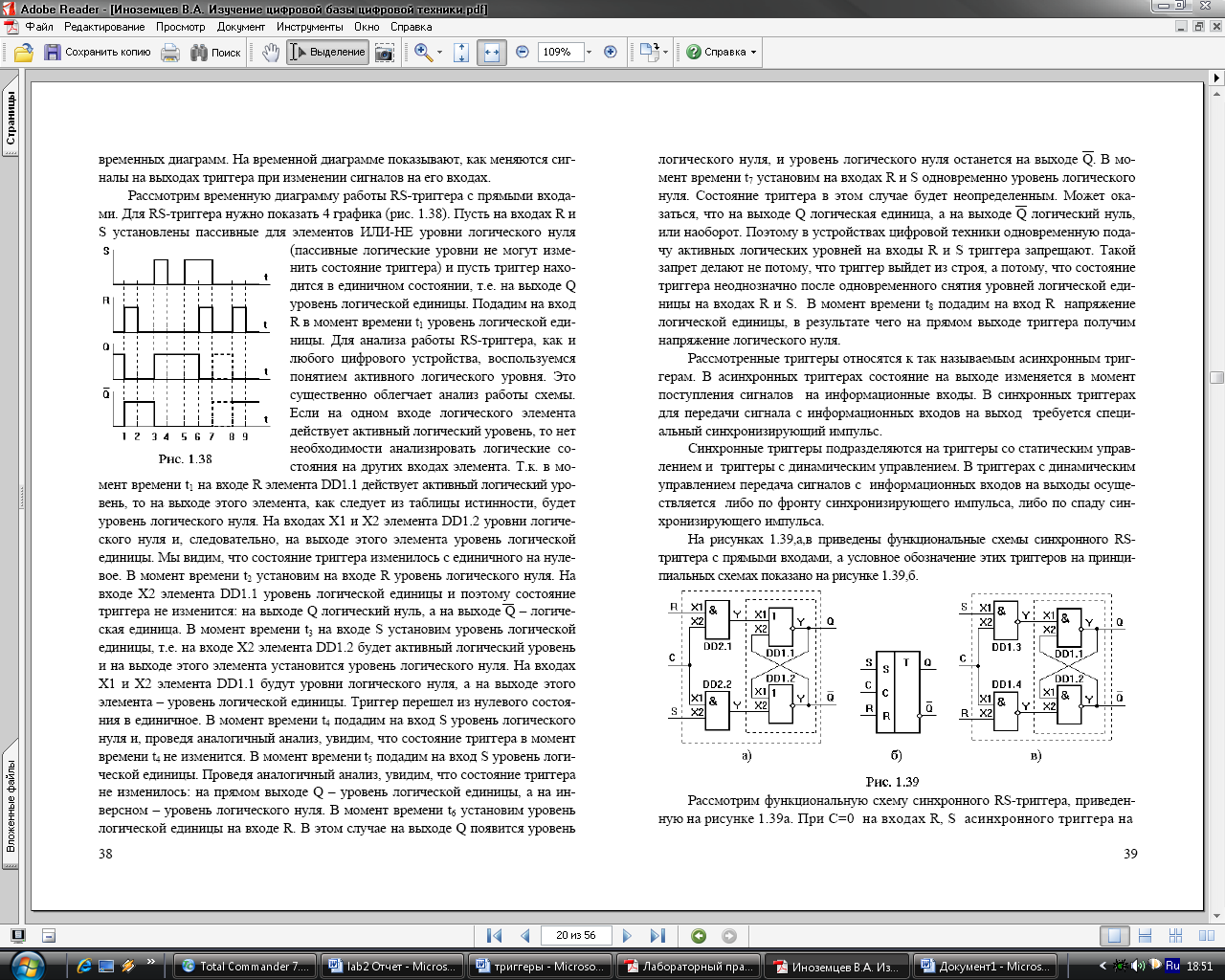

Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигналов с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса.

На рисунках 1.39,а,в приведены функциональные схемы синхронного RS-триггера с прямыми входами, а условное обозначение этих триггеров на принципиальных схемах показано на рисунке 1.39,б.

Рассмотрим функциональную схему синхронного RS-триггера, приведенную на рисунке 1.39а. При С=0 на входах R, S асинхронного триггера на элементах DD1.1 и DD1.2 действуют сигналы логического нуля (логический нуль является пассивным логическим уровнем для логических элементов 2ИЛИ-НЕ), поэтому при любых комбинациях сигналов на входах R, S синхронного RS-триггера состояние триггера не меняется. При С=1 рассмотренный синхронный RS-триггер работает точно так же, как рассмотренный чуть раньше асинхронный RS-триггер с прямыми входами. Рассмотренный только что синхронный RS-триггер относится к триггерам со статическим управлением.

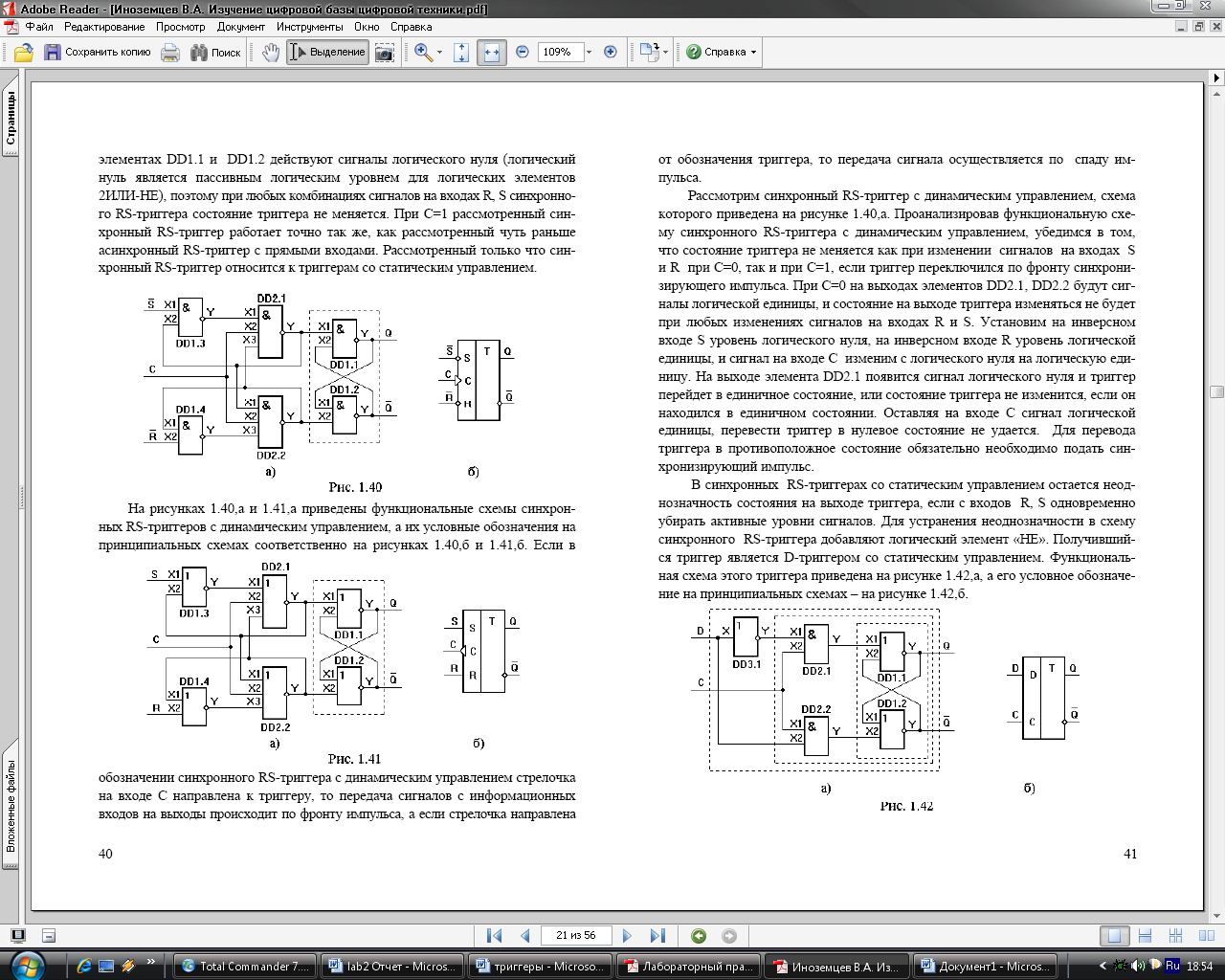

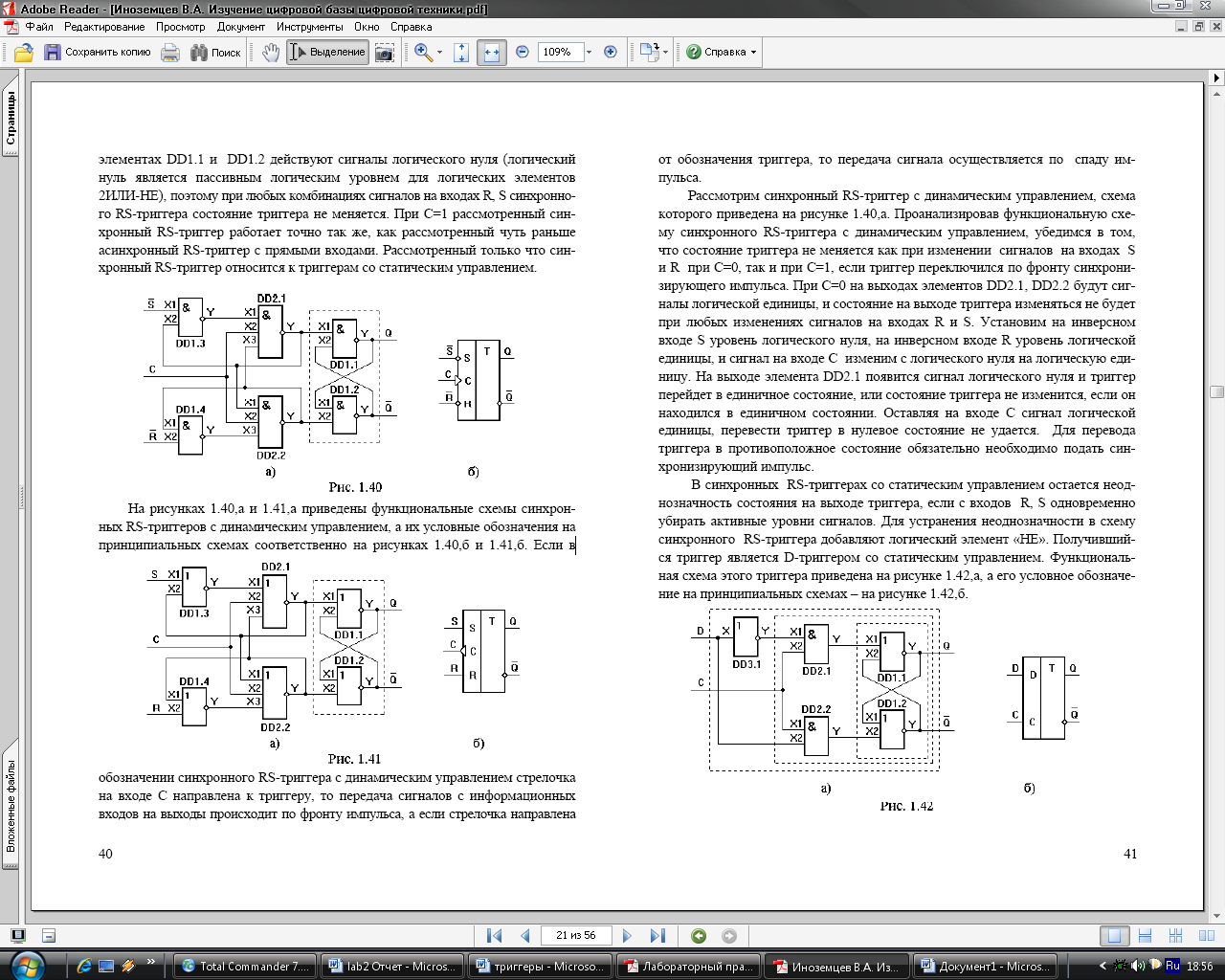

На рисунках 1.40,а и 1.41,а приведены функциональные схемы синхронных RS-триггеров с динамическим управлением, а их условные обозначения на принципиальных схемах соответственно на рисунках 1.40,б и 1.41,б. Если в

обозначении синхронного RS-триггера с динамическим управлением стрелочка на входе С направлена к триггеру, то передача сигналов с информационных входов на выходы происходит по фронту импульса, а если стрелочка направлена от обозначения триггера, то передача сигнала осуществляется по спаду импульса.

Рассмотрим синхронный RS-триггер с динамическим управлением, схема которого приведена на рисунке 1.40,а. Проанализировав функциональную схему синхронного RS-триггера с динамическим управлением, убедимся в том, что состояние триггера не меняется как при изменении сигналов на входах S и R при С=0, так и при С=1, если триггер переключился по фронту синхронизирующего импульса. При C=0 на выходах элементов DD2.1, DD2.2 будут сигналы логической единицы, и состояние на выходе триггера изменяться не будет при любых изменениях сигналов на входах R и S. Установим на инверсном входе S уровень логического нуля, на инверсном входе R уровень логической единицы, и сигнал на входе С изменим с логического нуля на логическую единицу. На выходе элемента DD2.1 появится сигнал логического нуля и триггер перейдет в единичное состояние, или состояние триггера не изменится, если он находился в единичном состоянии. Оставляя на входе С сигнал логической единицы, перевести триггер в нулевое состояние не удается. Для перевода триггера в противоположное состояние обязательно необходимо подать синхронизирующий импульс.

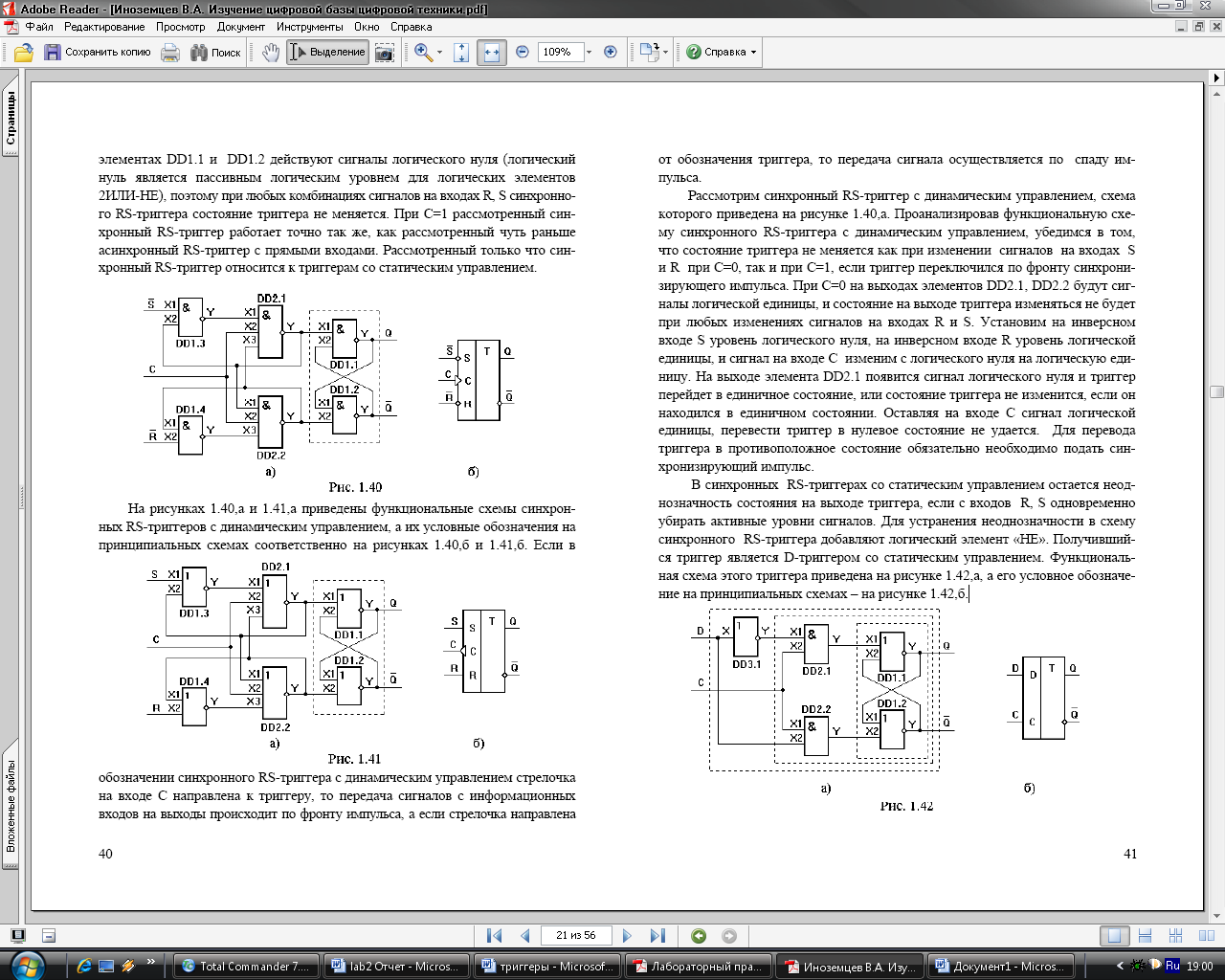

В синхронных RS-триггерах со статическим управлением остается неоднозначность состояния на выходе триггера, если с входов R, S одновременно убирать активные уровни сигналов. Для устранения неоднозначности в схему синхронного RS-триггера добавляют логический элемент «НЕ». Получившийся триггер является D-триггером со статическим управлением. Функциональная схема этого триггера приведена на рисунке 1.42,а, а его условное обозначение на принципиальных схемах - на рисунке 1.42,б.

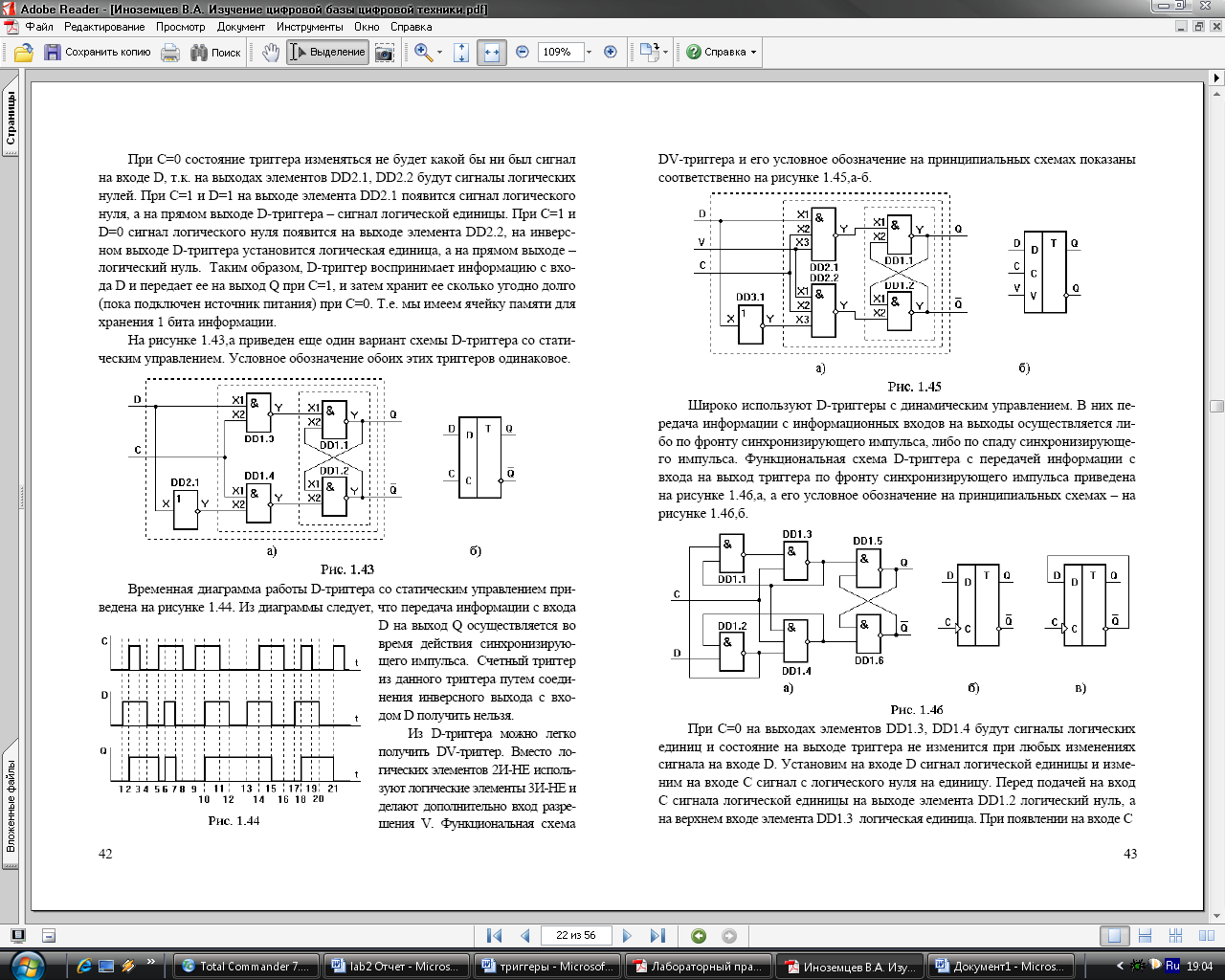

При С=0 состояние триггера изменяться не будет какой бы ни был сигнал на входе D, т.к. на выходах элементов DD2.1, DD2.2 будут сигналы логических нулей. При С=1 и D=1 на выходе элемента DD2.1 появится сигнал логического нуля, а на прямом выходе D-триггера - сигнал логической единицы. При С=1 и D=0 сигнал логического нуля появится на выходе элемента DD2.2, на инверсном выходе D-триггера установится логическая единица, а на прямом выходе -логический нуль. Таким образом, D-триггер воспринимает информацию с входа D и передает ее на выход Q при C=1, и затем хранит ее сколько угодно долго (пока подключен источник питания) при С=0. Т.е. мы имеем ячейку памяти для хранения 1 бита информации.

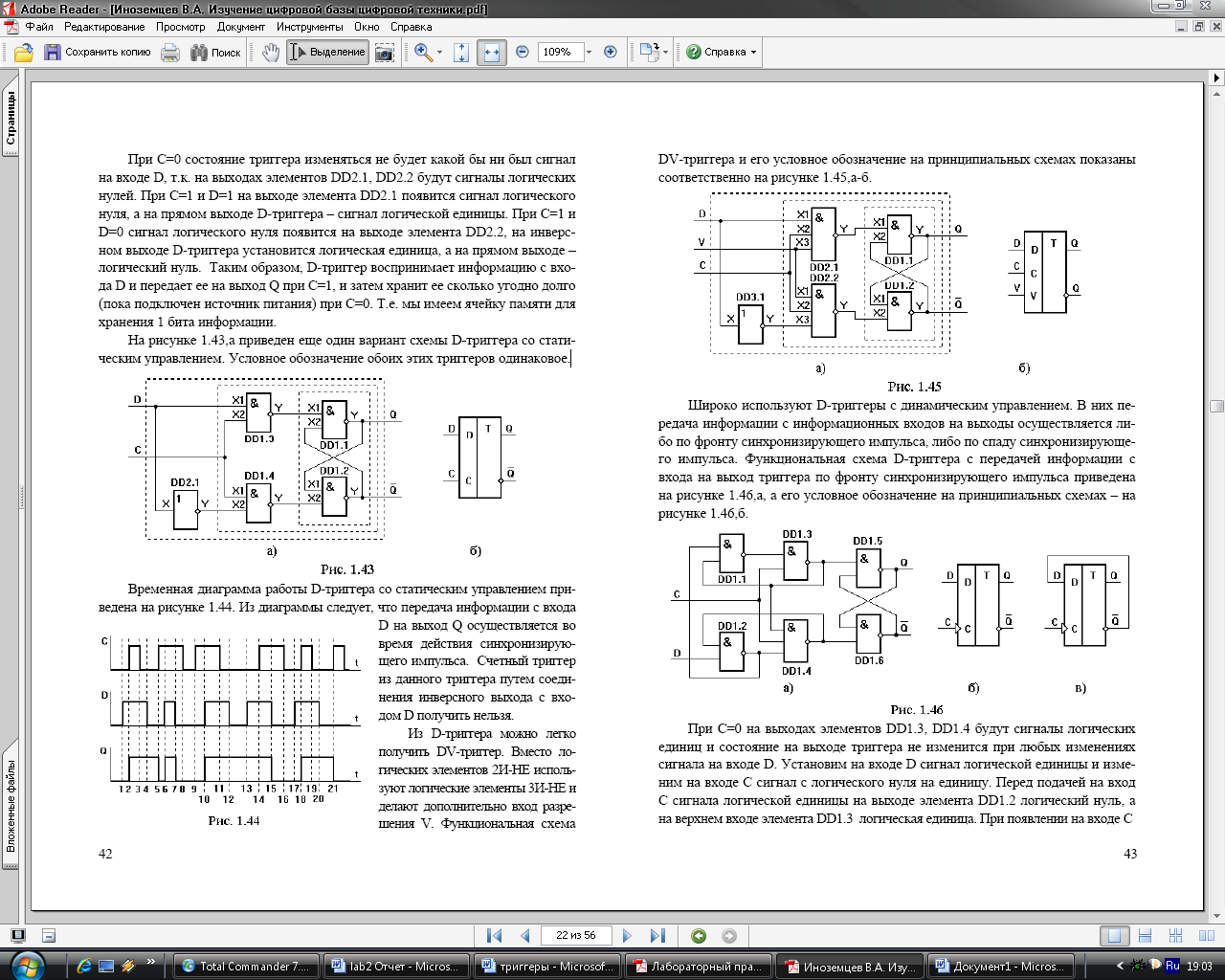

На рисунке 1.43,а приведен еще один вариант схемы D-триггера со статическим управлением. Условное обозначение обоих этих триггеров одинаковое.

Временная диаграмма работы D-триггера со статическим управлением приведена на рисунке 1.44.

Из диаграммы следует, что передача информации с входа D на выход Q осуществляется во время действия синхронизирующего импульса. Счетный триггер из данного триггера путем соединения инверсного выхода с входом D получить нельзя. Из D-триггера можно легко получить DV-триггер. Вместо логических элементов 2И-НЕ используют логические элементы 3И-НЕ и делают дополнительно вход разрешения V. Функциональная схема DV-триггера и его условное обозначение на принципиальных схемах показаны соответственно на рисунке 1.45,а-б.

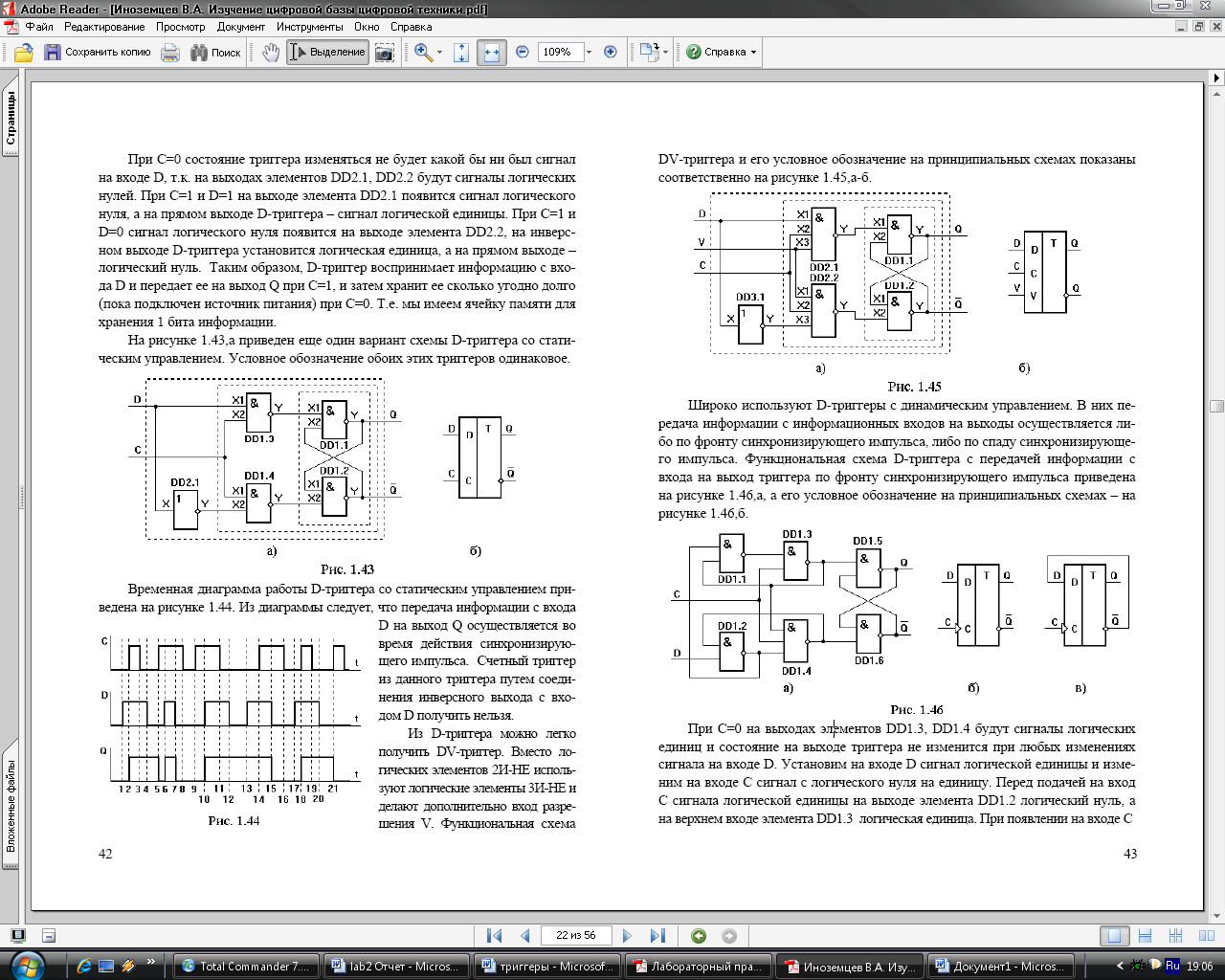

Широко используют D-триггеры с динамическим управлением. В них передача информации с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса. Функциональная схема D-триггера с передачей информации с входа на выход триггера по фронту синхронизирующего импульса приведена на рисунке 1.46,а, а его условное обозначение на принципиальных схемах - на рисунке 1.46,б.

При С=0 на выходах элементов DD1.3, DD1.4 будут сигналы логических единиц и состояние на выходе триггера не изменится при любых изменениях сигнала на входе D. Установим на входе D сигнал логической единицы и изменим на входе С сигнал с логического нуля на единицу. Перед подачей на вход С сигнала логической единицы на выходе элемента DD1.2 логический нуль, а на верхнем входе элемента DD1.3 логическая единица. При появлении на входе С логической единицы на выходе элемента DD1.3 установится логический нуль, а на прямом выходе триггера - логическая единица. Сигнал логического нуля подается с выхода элемента DD1.3 на нижний вход элемент DD1.1 и на верхний вход элемента DD1.4. Оставляя на входе С логическую единицу, изменим сигнал на входе D с логической единицы на нуль. На выходе элемента DD1.2 установится логическая единица, а сигналы на выходах элементов DD1.1, DD1.3 не изменятся, следовательно, не изменится состояние на выходе триггера.

При D=0 изменим сигнал на входе С с логической единицы на нуль. На выходах элементов DD1.3, DD1.4 будут логические единицы, а на прямом выходе триггера останется сигнал логической единицы. Затем изменим сигнал на входе С с логического нуля на логическую единицу. На выходе DD1.4 установится логический нуль, на инверсном выходе триггера логическая единица, а прямом выходе - логический нуль. Из анализа работы данного триггера следует, что в нем передача информации с входа D на выход Q осуществляется по фронту синхронизирующего импульса, подаваемого на вход С.

Триггеры являются составной частью счетчиков электрических импульсов. D-триггер с динамическим управлением легко превратить в счетный триггер. С этой целью необходимо инверсный выход триггера соединить с информационным входом D, а импульсы подавать на синхронизирующий вход. Схема такого соединения приведена на рисунке 1.46,в.

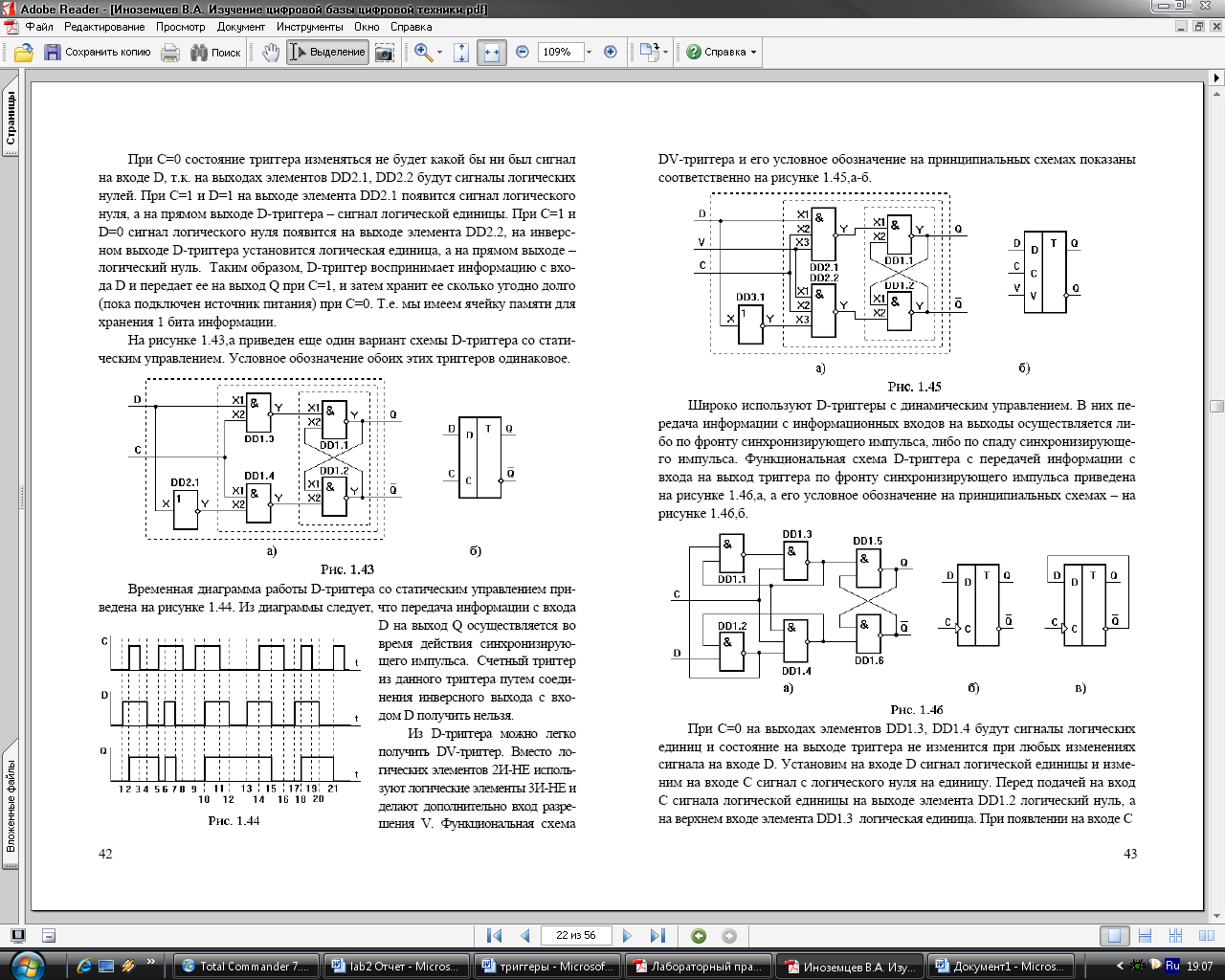

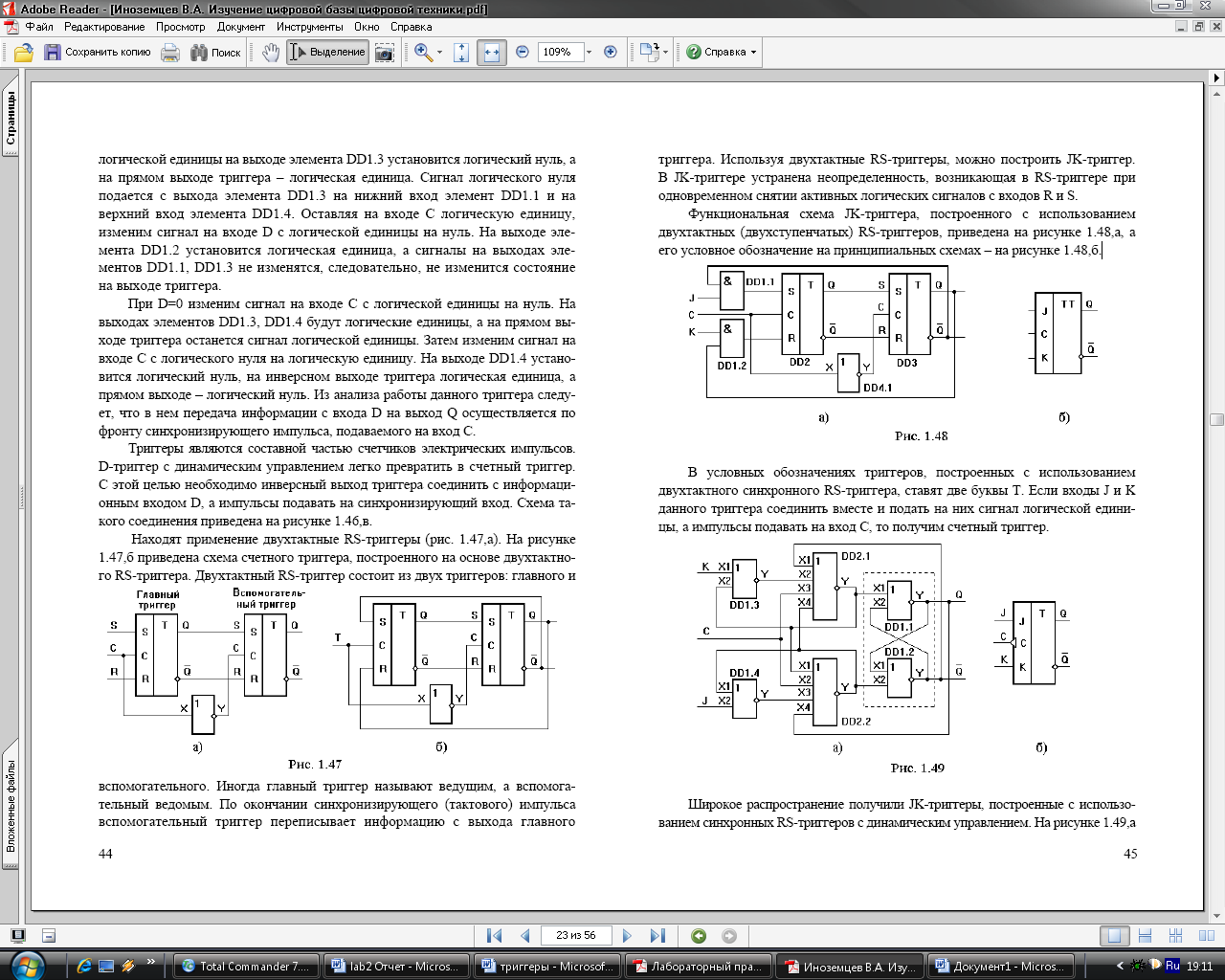

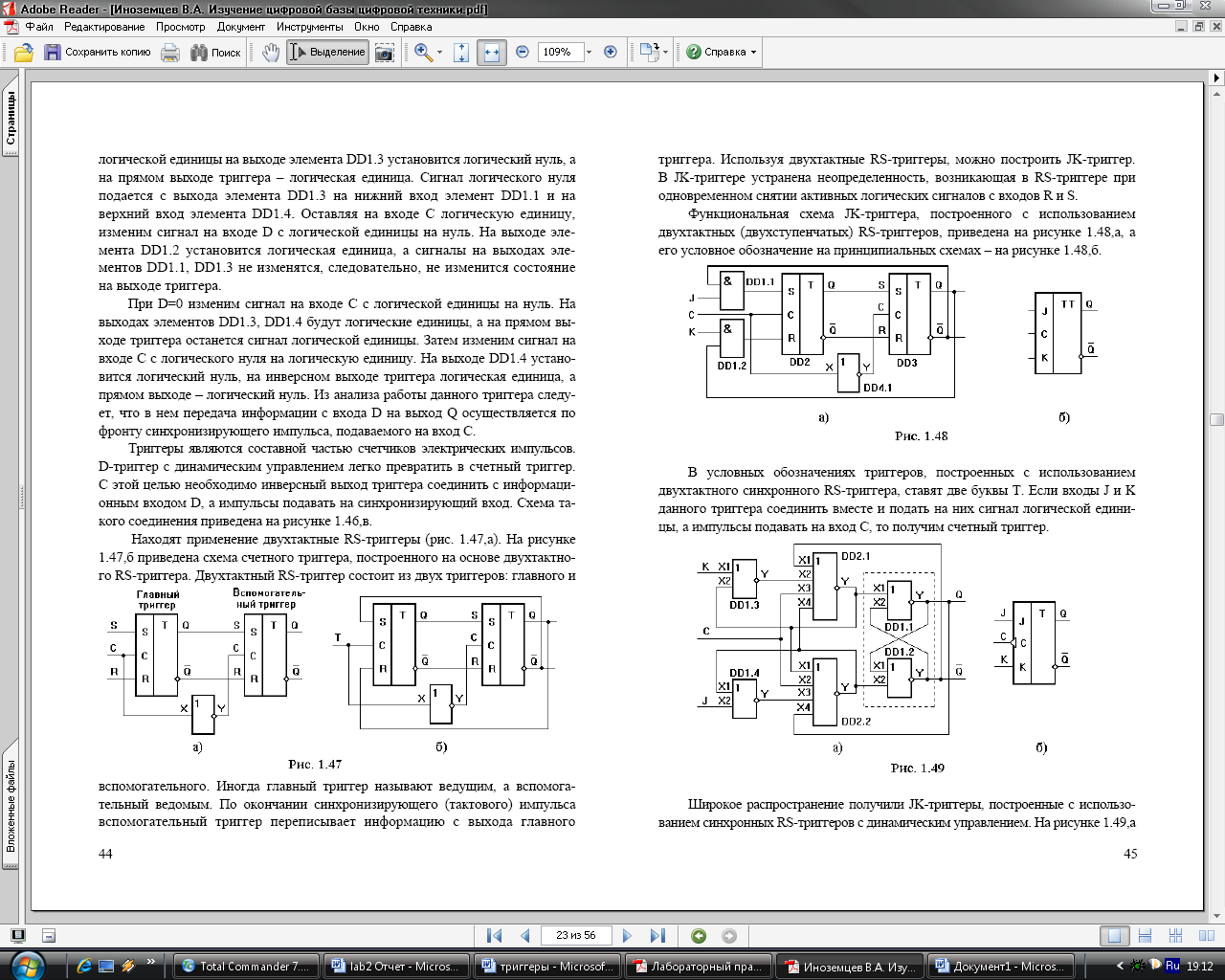

Находят применение двухтактные RS-триггеры (рис. 1.47,а). На рисунке 1.47,б приведена схема счетного триггера, построенного на основе двухтактного RS-триггера. Двухтактный RS-триггер состоит из двух триггеров: главного и

вспомогательного. Иногда главный триггер называют ведущим, а вспомогательный ведомым. По окончании синхронизирующего (тактового) импульса вспомогательный триггер переписывает информацию с выхода главного триггера. Используя двухтактные RS-триггеры, можно построить JK-триггер. В JK-триггере устранена неопределенность, возникающая в RS-триггере при одновременном снятии активных логических сигналов с входов R и S.

Функциональная схема JK-триггера, построенного с использованием двухтактных (двухступенчатых) RS-триггеров, приведена на рисунке 1.48,а, а его условное обозначение на принципиальных схемах - на рисунке 1.48,б.

В условных обозначениях триггеров, построенных с использованием двухтактного синхронного RS-триггера, ставят две буквы Т. Если входы J и K данного триггера соединить вместе и подать на них сигнал логической единицы, а импульсы подавать на вход С, то получим счетный триггер.

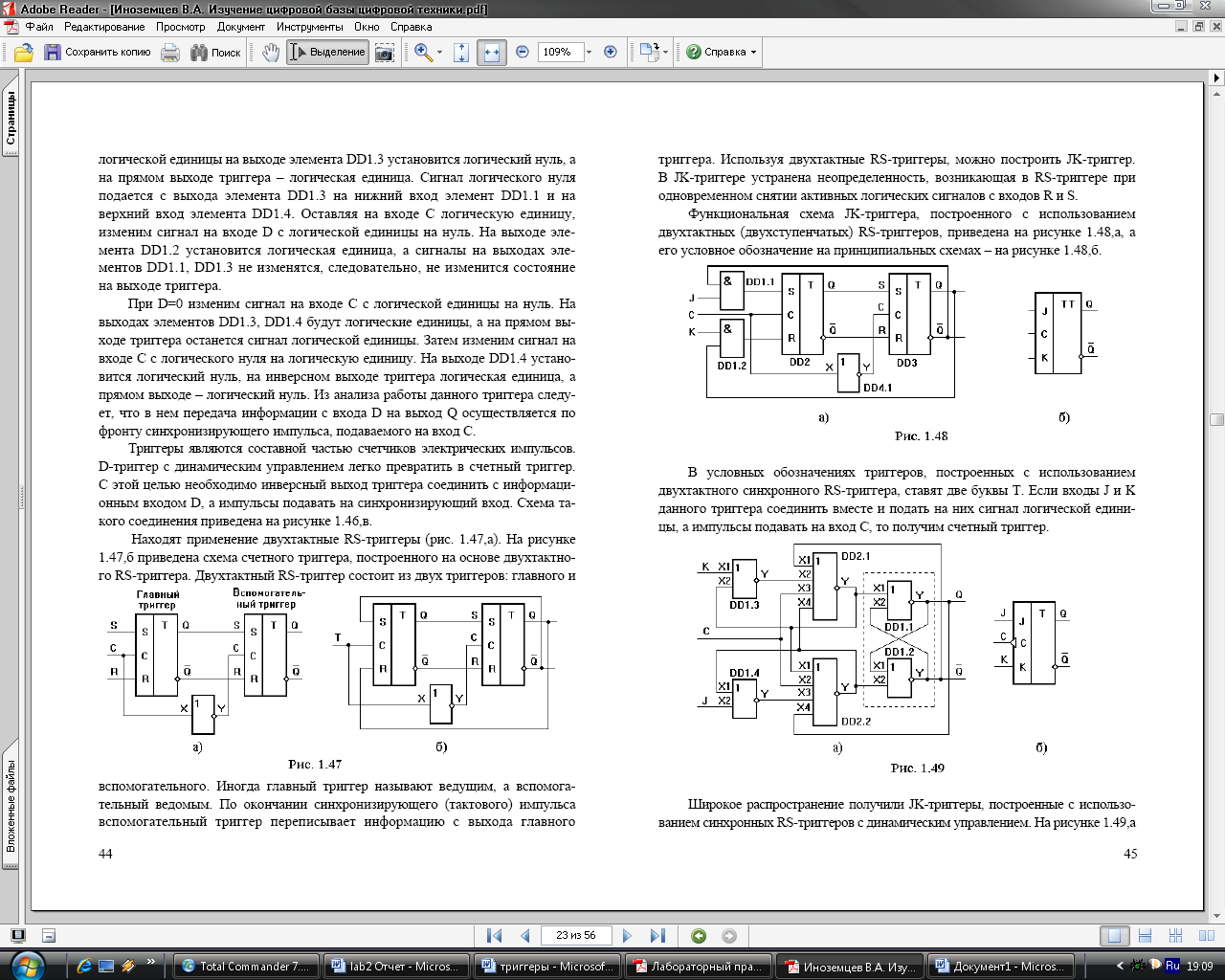

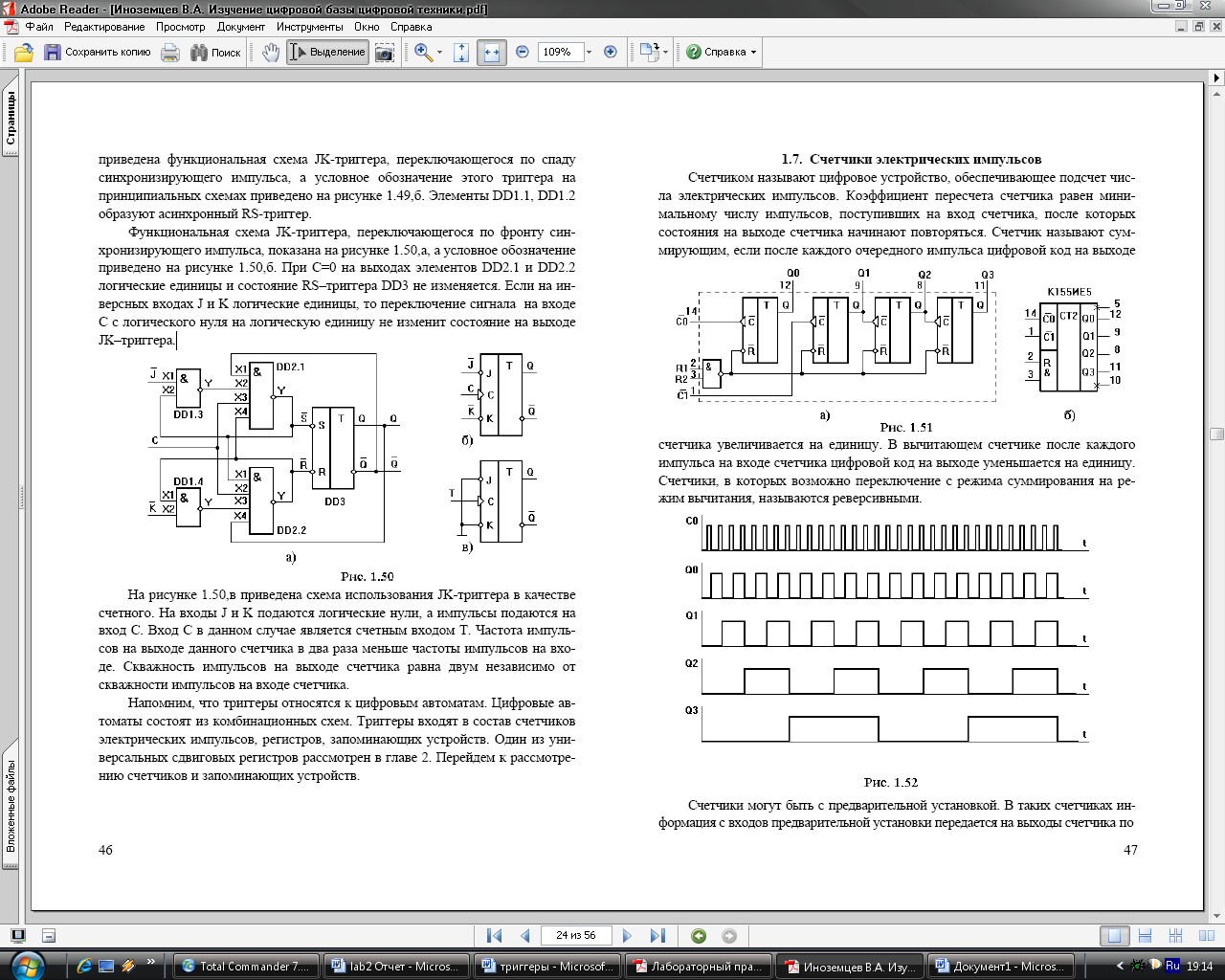

Широкое распространение получили JK-триггеры, построенные с использованием синхронных RS-триггеров с динамическим управлением. На рисунке 1.49,а приведена функциональная схема JK-триггера, переключающегося по спаду синхронизирующего импульса, а условное обозначение этого триггера на принципиальных схемах приведено на рисунке 1.49,б. Элементы DD1.1, DD1.2 образуют асинхронный RS-триггер.

Функциональная схема JK-триггера, переключающегося по фронту синхронизирующего импульса, показана на рисунке 1.50,а, а условное обозначение приведено на рисунке 1.50,б. При С=0 на выходах элементов DD2.1 и DD2.2 логические единицы и состояние RS-триггера DD3 не изменяется. Если на инверсных входах J и K логические единицы, то переключение сигнала на входе С с логического нуля на логическую единицу не изменит состояние на выходе JK-триггера.

На рисунке 1.50,в приведена схема использования JK-триггера в качестве счетного. На входы J и K подаются логические нули, а импульсы подаются на вход С. Вход С в данном случае является счетным входом Т. Частота импульсов на выходе данного счетчика в два раза меньше частоты импульсов на входе. Скважность импульсов на выходе счетчика равна двум независимо от скважности импульсов на входе счетчика.

Напомним, что триггеры относятся к цифровым автоматам. Цифровые автоматы состоят из комбинационных схем. Триггеры входят в состав счетчиков электрических импульсов, регистров, запоминающих устройств.

Порядок выполнения работы.

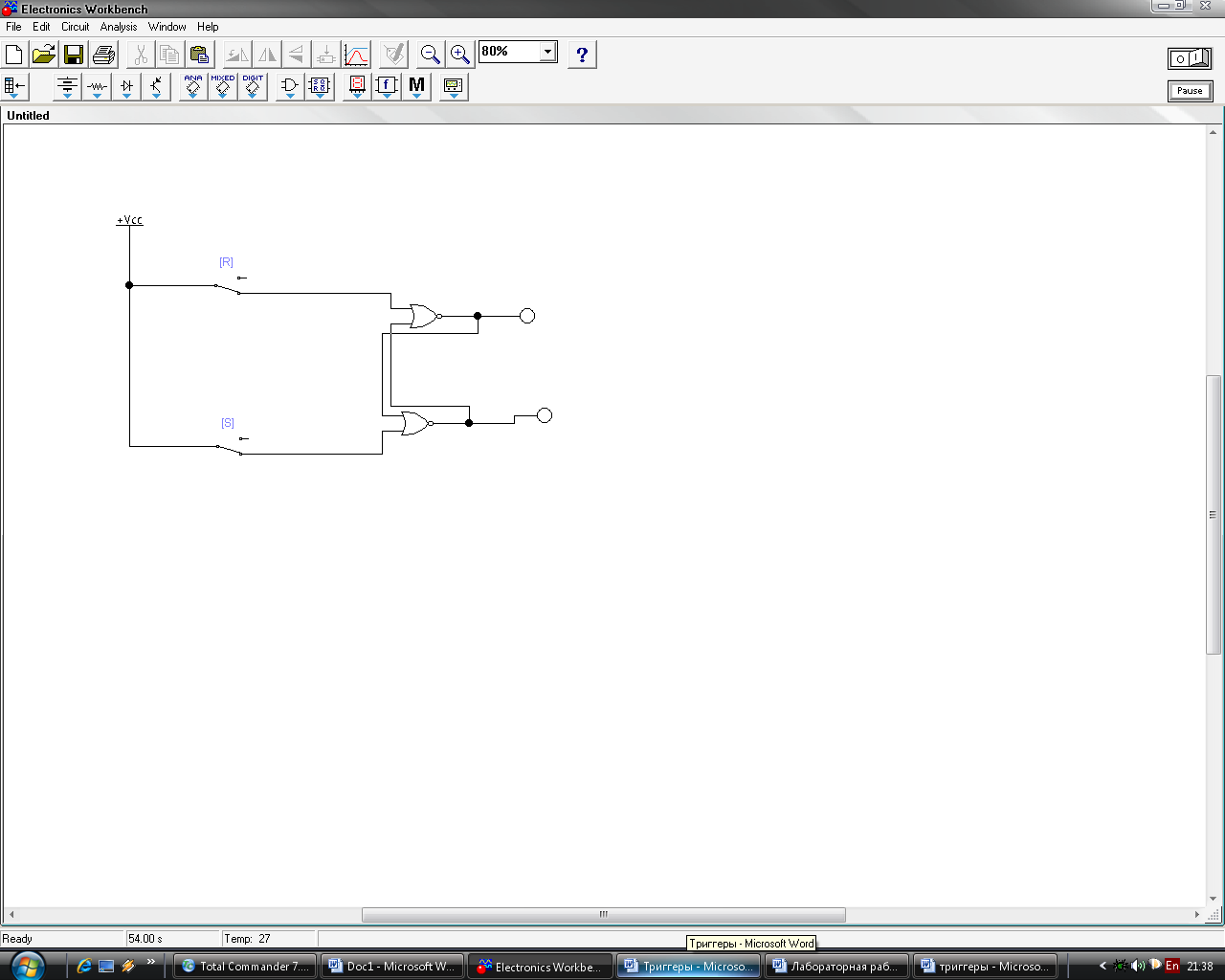

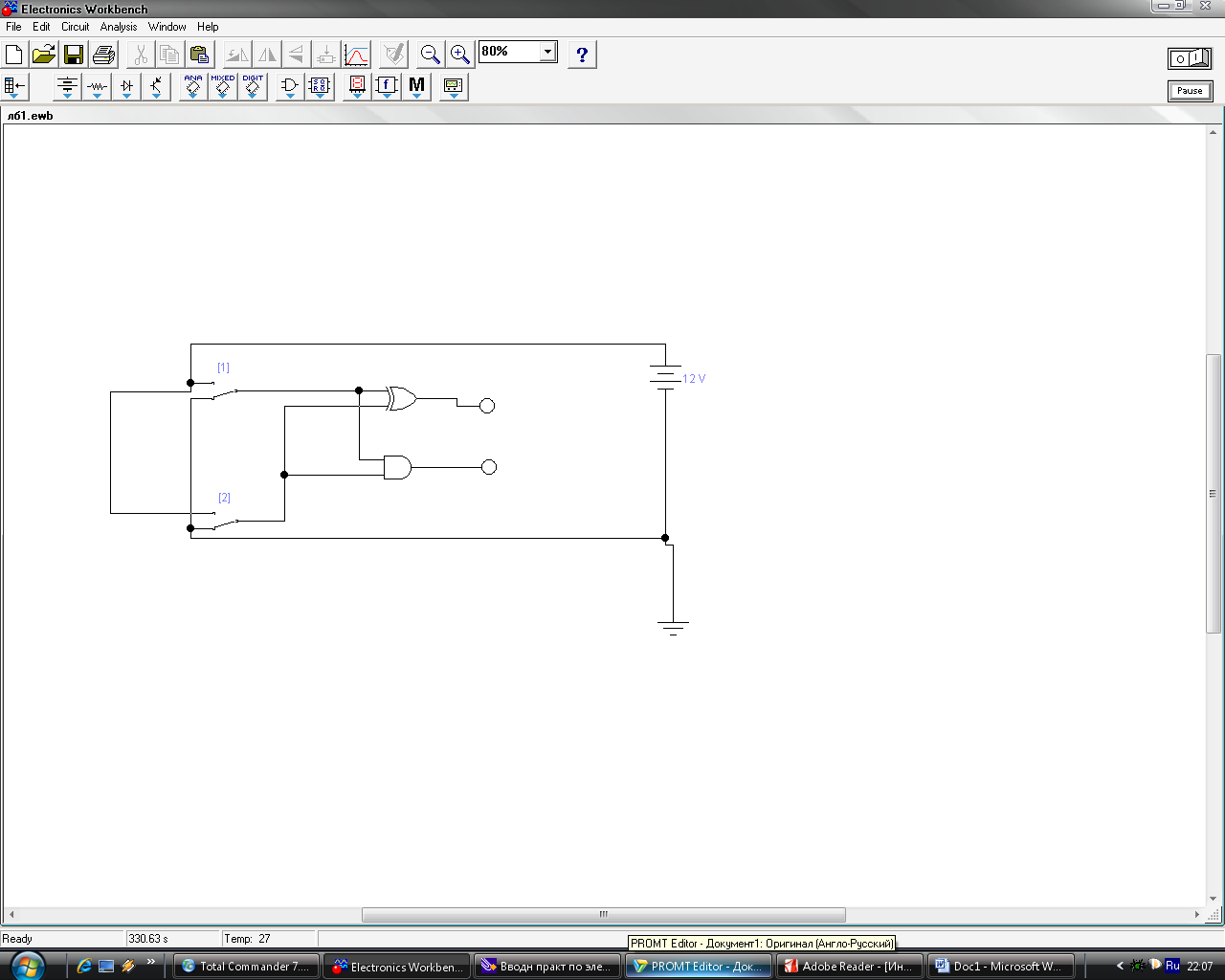

Задание 1. Исследование работы RS-триггера в статическом режиме.

1. Соберите схему асинхронного RS-триггера из элементов 2ИЛИ-НЕ.

2. Составьте таблицу состояний в зависимости от входных сигналов (таблица должна содержать все возможные комбинации входных сигналов):

![]()

![]()

![]()

![]()

![]()

- состояние выхода Q до подачи, а

- состояние выхода Q до подачи, а  - после подачи сигналов на входы триггера.

- после подачи сигналов на входы триггера.

3. Проверьте таблицу состояний с помощью характеристического уравнения:

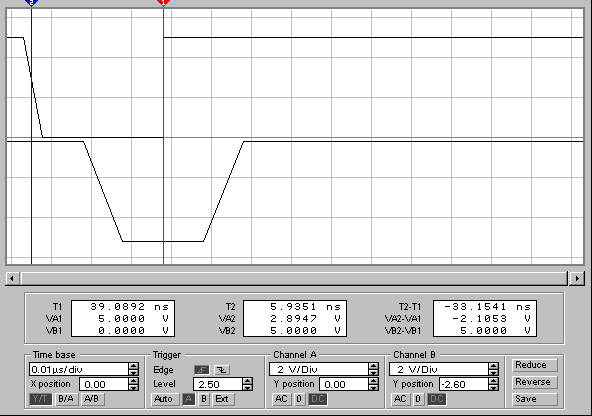

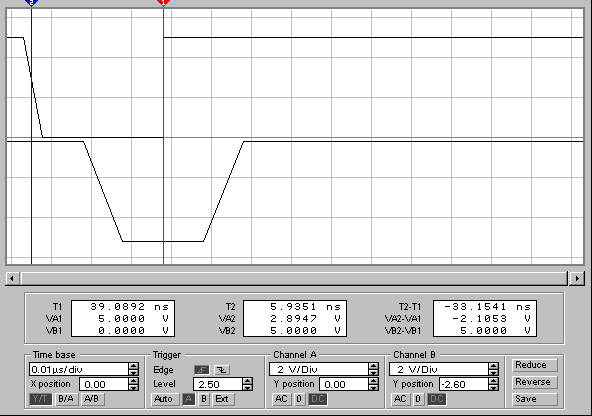

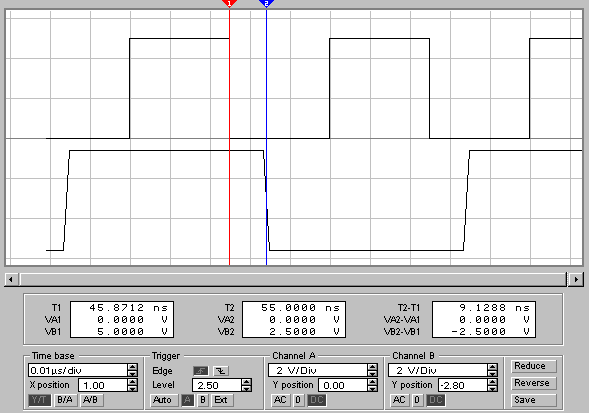

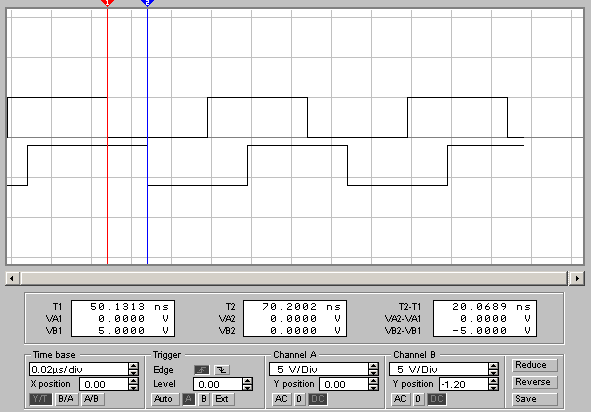

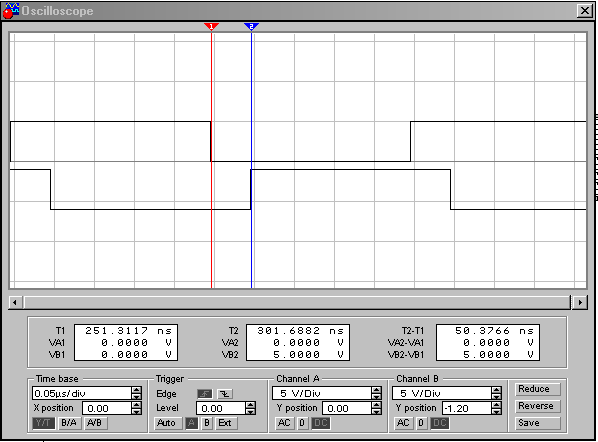

2. Исследование работы схемы RS-триггера в динамическом режиме.

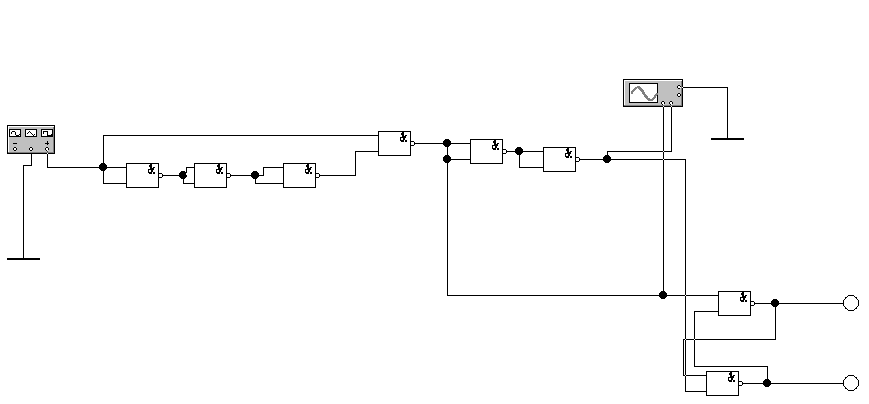

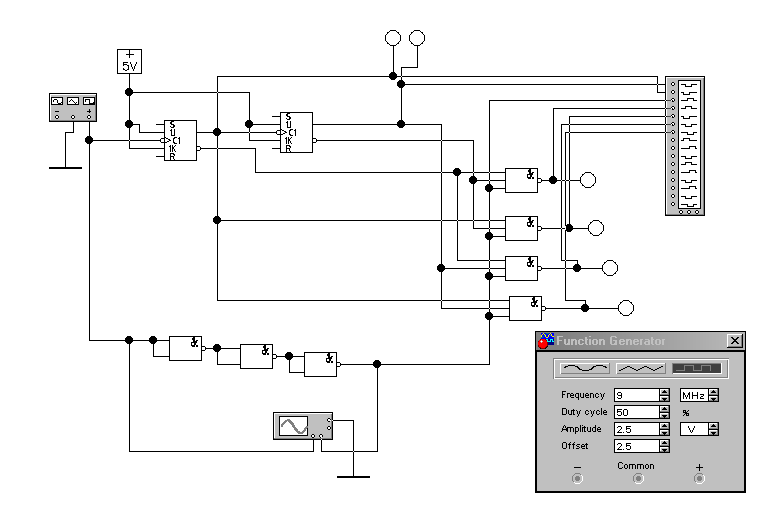

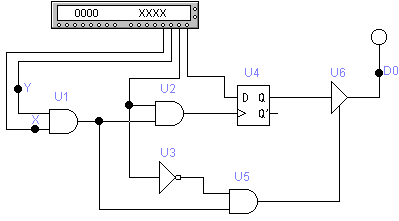

1. Соберите схему:

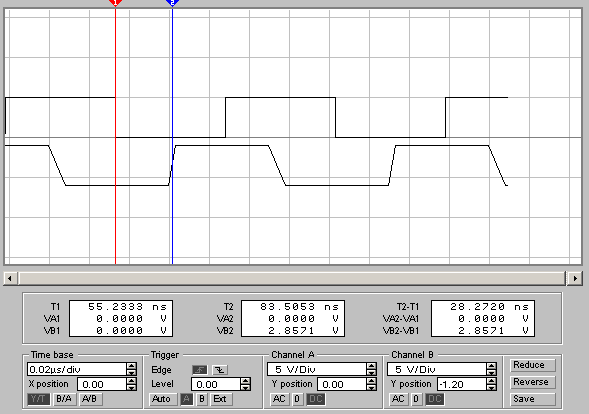

Данная схема состоит из схемы генератора импульсов малой длительности, состоящей из m=3 И-НЕ и схемы формирования задержки, состоящей из k=2 И-НЕ. Данные параметры являются критическими, то есть при меньшей длительности импульса не происходит переключение триггера и при меньшей задержке (вообще говоря данная задержка минимальна) триггер работает неправильно. При таких параметрах можно измерить динамические параметры RS-триггера.

2. Установите на осциллографе следующие параметры:

3. Определите минимальную длительность импульса.

4. Определите разрешающее время триггера.

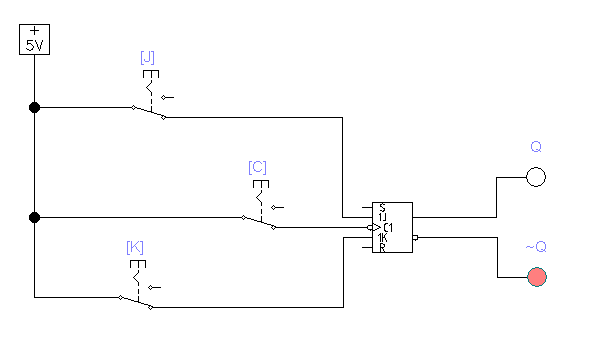

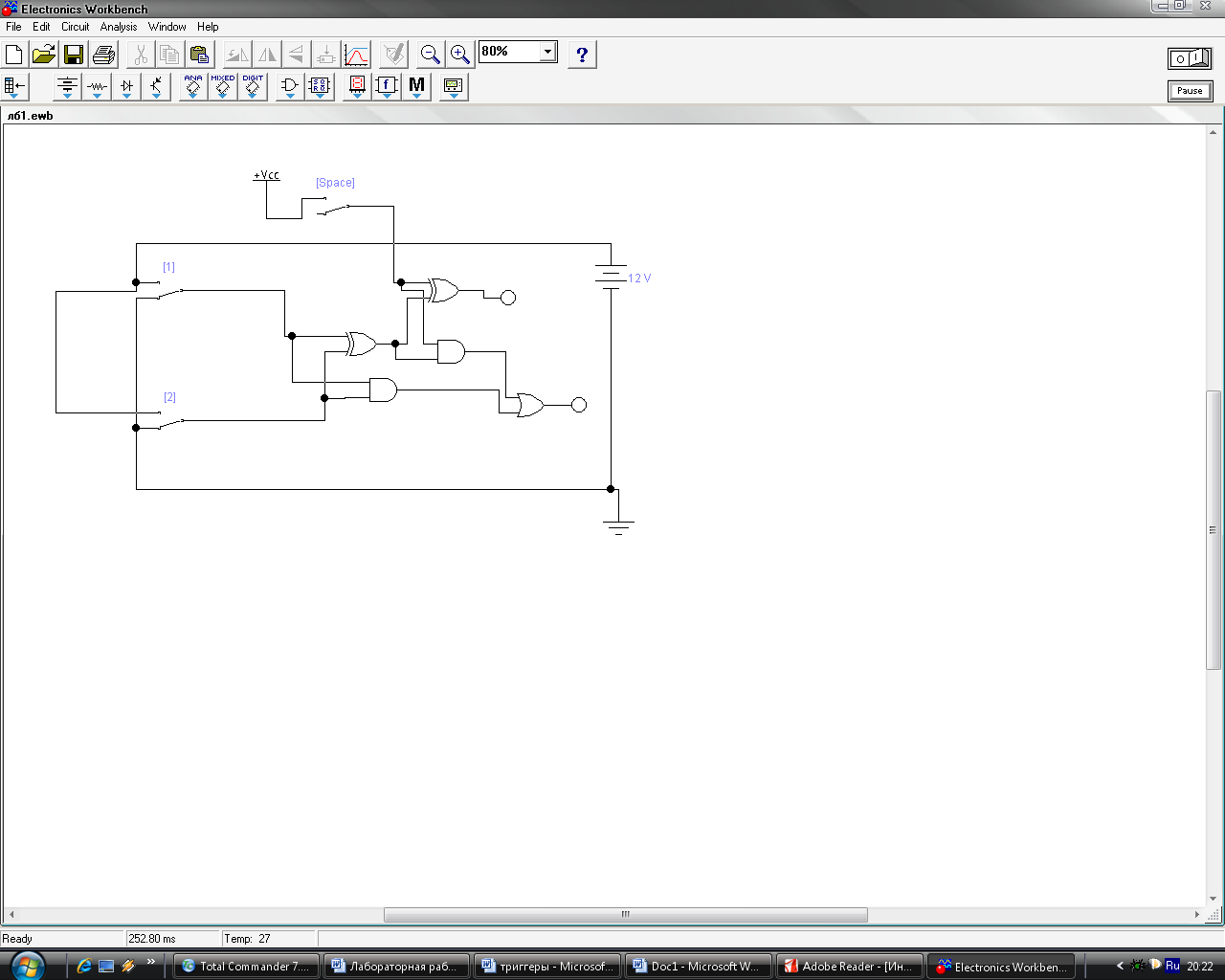

3. Исследование работы JK-триггера в статическом режиме.

1. Соберите схему с использованием библиотечного JK-триггера.

2. Составьте таблицу переходов для данного триггера. Сигнал C не показан в таблице, так как его сброс в 0 устанавливает выходное значение триггера. Если сигнал C не изменяется, то не изменяется и выходное состояние триггера.

J

K

JK-триггер, в отличие от RS-триггера, не имеет запрещенного состояния. При подаче на вход J=K=1, происходит переключение состояния триггера, то есть работа в режиме счетного T-триггера.

3. Проверьте таблицу состояний с помощью характеристического уравнения:

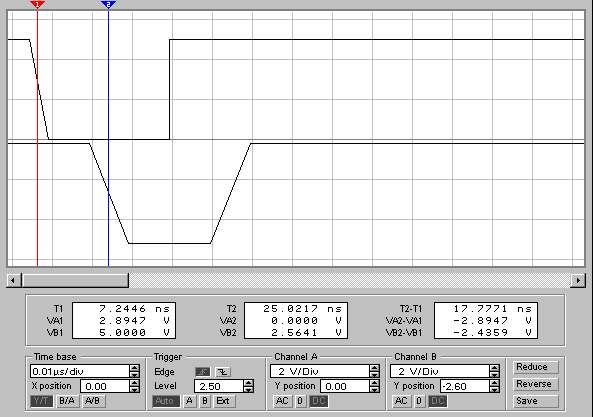

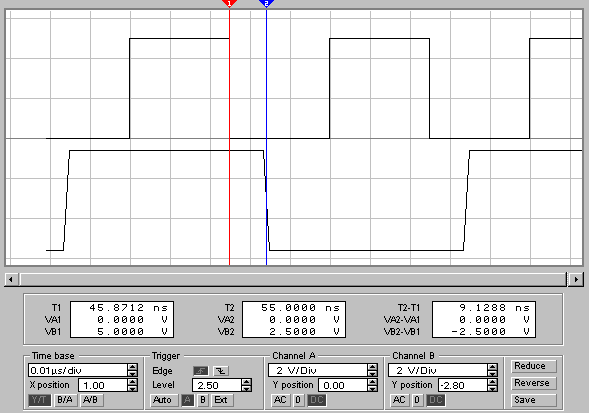

4. Исследование работы схемы JK-триггера в динамическом режиме.

1. Соберите схему:

На входы J и K подаются 1, что обеспечивает работу в режиме счетного триггера.

2. Установите следующие параметры:

Частоту - 10 МГц, амплитуду - 5 В.

3. Определите время переключения триггера.

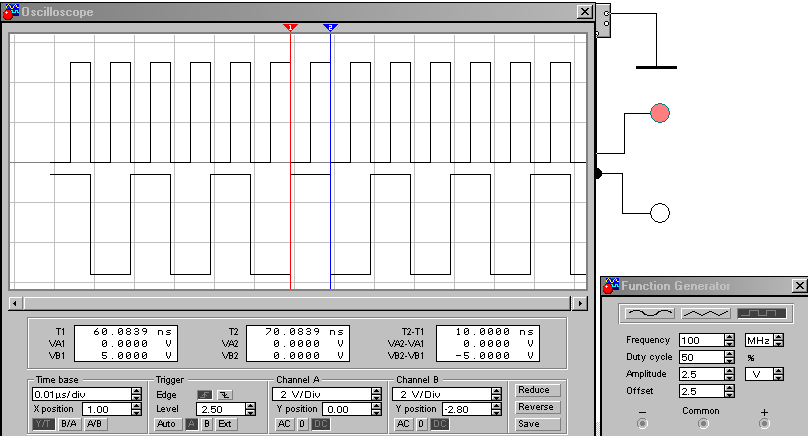

4. Увеличивайте частоту импульсов на входе до тех пор, пока триггер не начнет работать неправильно.

а) правильная работа

б) неправильная работа

5. Найдите разрешающую способность триггера для максимальной частоты правильной работы. Сравните его со временем переключения.

5. Исследование работы JK-триггера (ttl LC) в динамическом режиме.

1. Замените идеальный триггер моделью реального.

2. Определите разрешающее время данного триггера.

Практическая работа №5 «Исследование работы регистров хранения и сдвига»

Цель: изучение принципов построения регистров, макетирование регистров и их экспериментальное исследование.

Теоретическая часть.

Регистр - операционный элемент, состоящий из триггеров, основным назначением которого является прием и хранение чисел с двоичным представлением цифр разрядов.

Регистры можно получать, объединяя в группы некоторое число триггеров. Такие группы являются простейшими запоминающими устройствами, способными хранить дискретную информацию в виде двоичных чисел. Основными видами этих функциональных узлов являются параллельные и последовательные регистры.

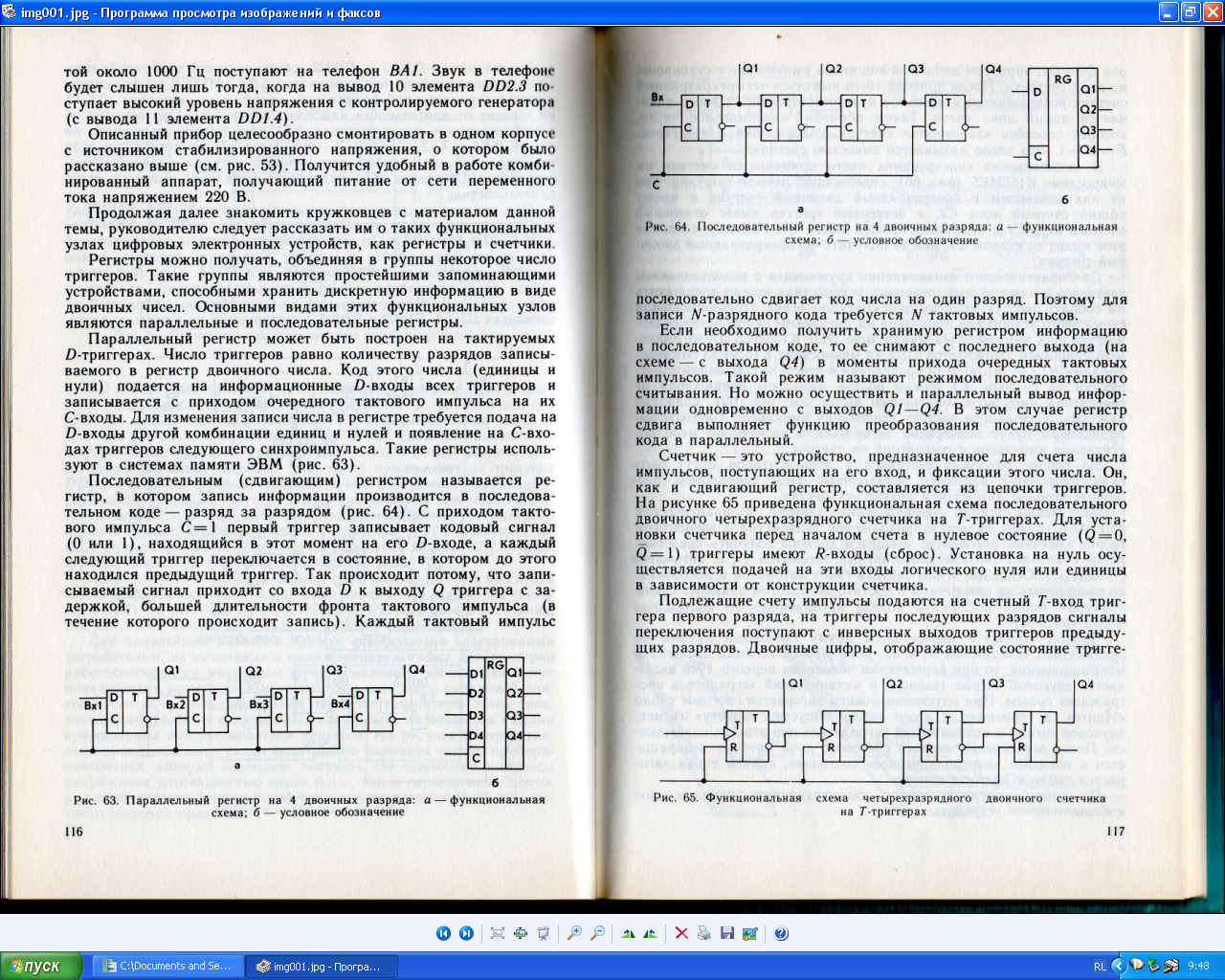

Параллельный регистр может быть построен на тактируемых D - триггерах. Число триггеров равно количеству разрядов записываемого в регистр двоичного числа. Код этого числа (единицы и нули) подается на информационные D - входы всех триггеров и записывается с приходом очередного тактового импульса на их C - входы. Для изменения записи числа в регистре требуется подача на D - входы другой комбинации единиц и нулей и появление на C - входах триггеров следующего синхроимпульса. Такие регистры используются в системах памяти ЭВМ. На рис. 1 приведены функциональная схема и условное обозначение параллельного регистра на 4 двоичных разряда.

Рис. 1

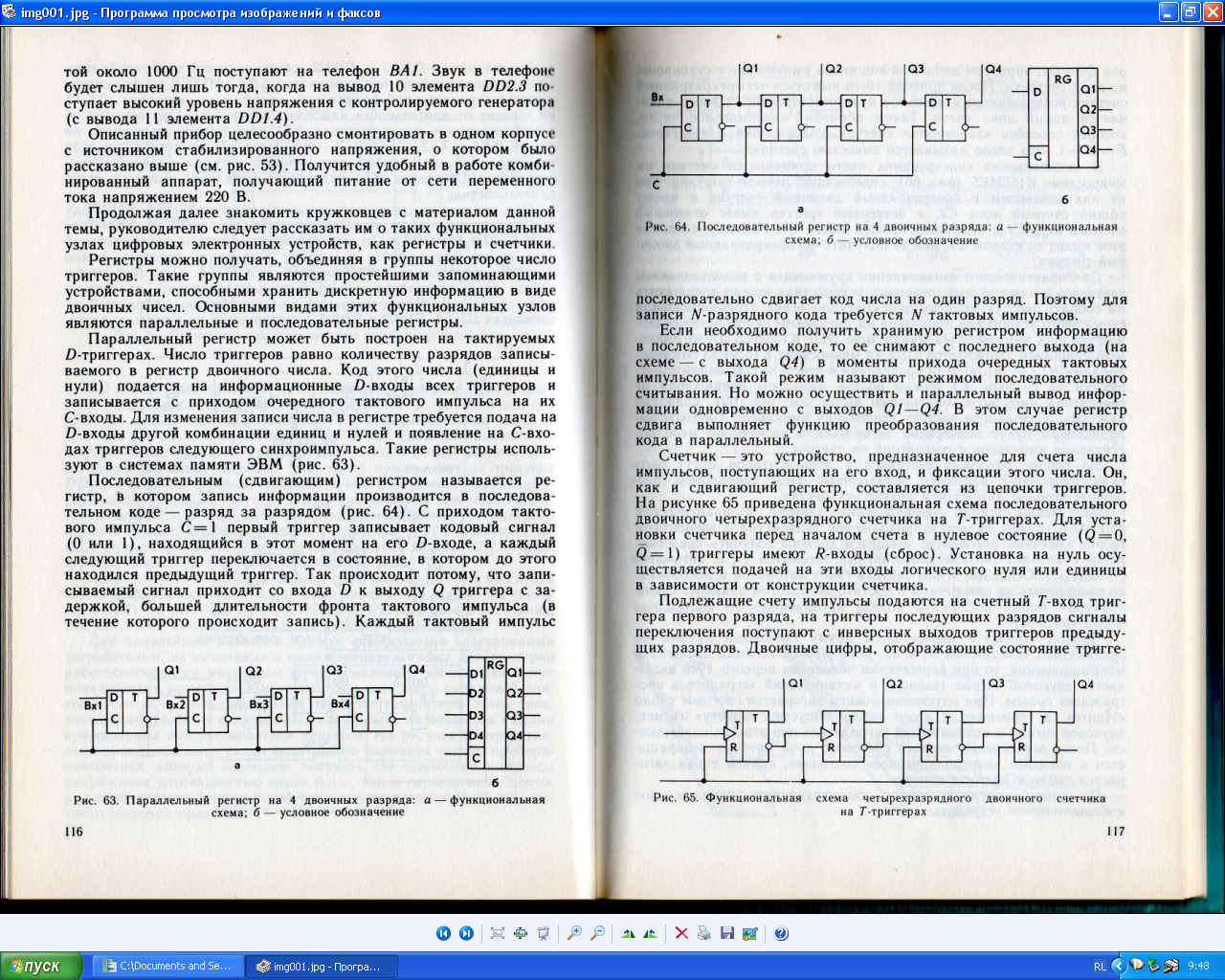

Последовательным (сдвигающим) регистром называется регистр, в котором запись информации производится в последовательном коде - разряд за разрядом. На рисунке 2 приведены функциональная схема и условное обозначение последовательного регистра на 4 двоичных разряда .

Рис. 2

С приходом тактового импульса C = 1 первый триггер записывает кодовый сигнал (0 или 1), находящийся в этот момент на его D - входе, а каждый следующий триггер переключается в состояние, в котором до этого находился предыдущий триггер. Так происходит потому, что записываемый сигнал приходит со входа D к выходу Q триггера с задержкой, большей длительности фронта тактового импульса (в течение которого происходит запись). Каждый тактовый импульс последовательно сдвигает код числа на один разряд. Поэтому для записи N - разрядного кода требуется N тактовых импульсов.

приходом тактового импульса C = 1 первый триггер записывает кодовый сигнал (0 или 1), находящийся в этот момент на его D - входе, а каждый следующий триггер переключается в состояние, в котором до этого находился предыдущий триггер. Так происходит потому, что записываемый сигнал приходит со входа D к выходу Q триггера с задержкой, большей длительности фронта тактового импульса (в течение которого происходит запись). Каждый тактовый импульс последовательно сдвигает код числа на один разряд. Поэтому для записи N - разрядного кода требуется N тактовых импульсов.

Если необходимо получить хранимую регистром информацию в последовательном коде, то ее снимают с последнего выхода ( на схеме - с выхода Q4) в моменты прихода очередных тактовых импульсов. Такой режим называют режимом последовательного считывания. Но можно осуществить и параллельный вывод информации одновременно с выходов Q1 - Q4. В этом случае регистр сдвига выполняет функцию преобразования последовательного кода в параллельный.

Порядок выполнения работы.

Задание 1. Исследование параллельного регистра.

-

Соберите схему параллельного регистра на тактируемых D - триггерах (рис. 1).

-

Запишите в регистр любое двоичное число.

-

Зарисуйте временные диаграммы на входе и на выходах регистра.

Задание 2. Исследование последовательного регистра.

-

Соберите схему последовательного регистра на 4 двоичных разряда (рис. 2).

-

Постройте таблицы переходов.

![]()

![]()

![]()

![]()

![]()

1

0

0

0

![]()

![]()

![]()

![]()

![]()

1

1

1

1

-

Постройте графы переходов.

-

Зарисуйте временные диаграммы на входе и на выходах регистра.

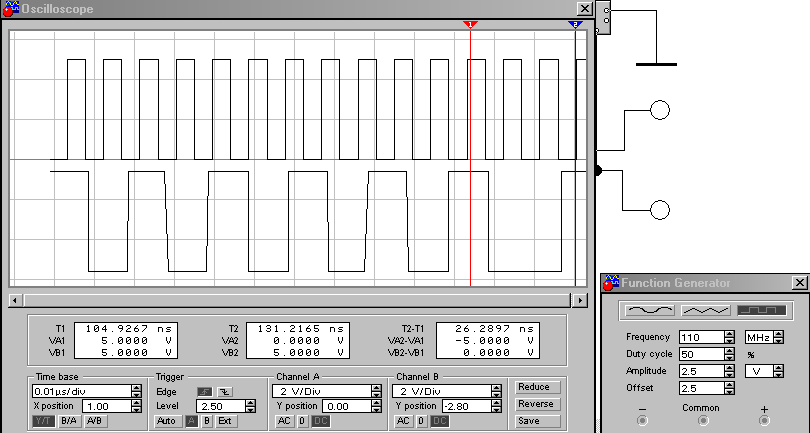

-

Определить интервал следования импульсов сдвига.

-

Определить максимальную рабочую частоту регистра сдвигов.

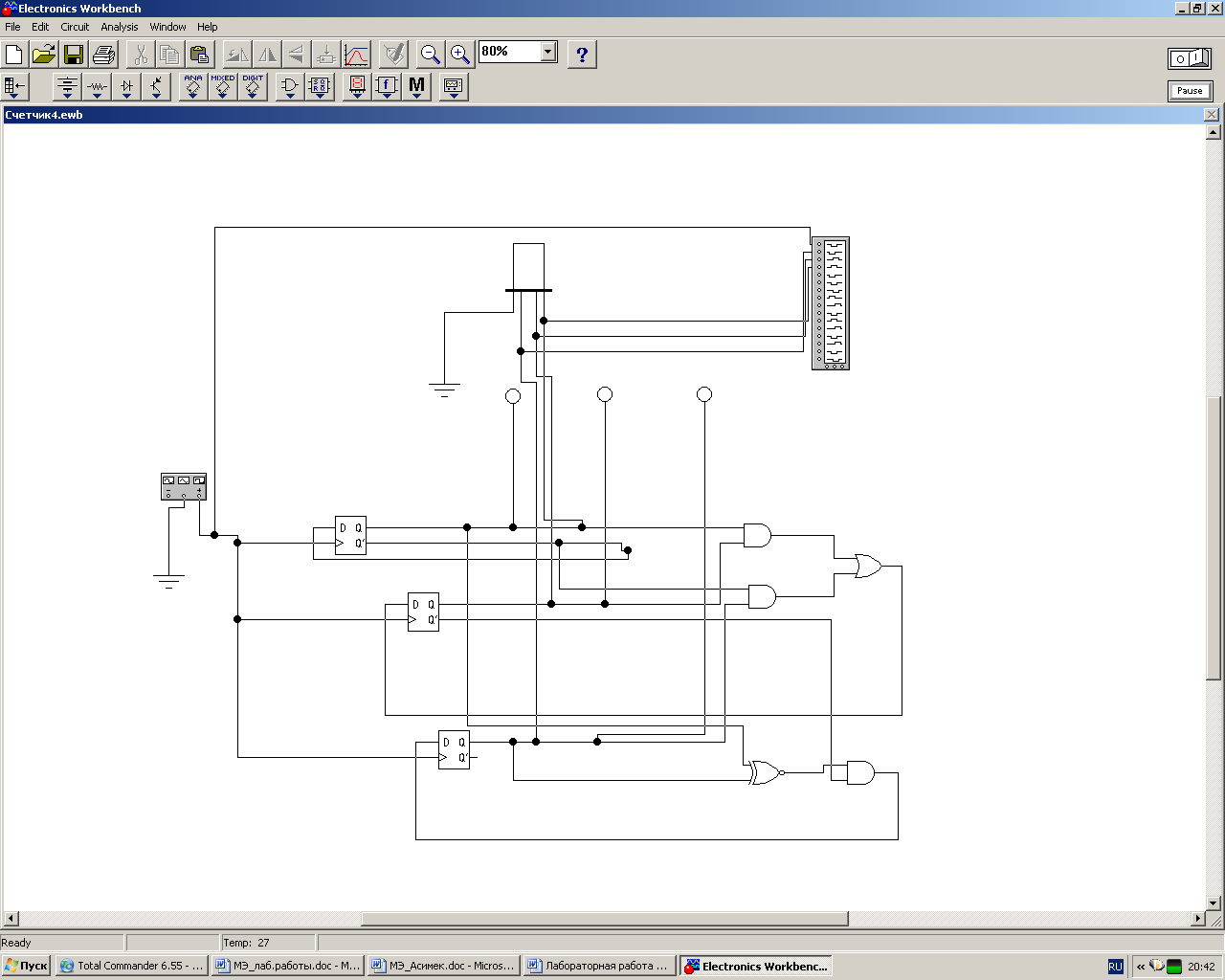

Практическая работа №6 «Исследования работы двоичных и двоично - десятичных счетчиков»

Цель: Изучение принципов построения и работы двоичных счетчиков, экспериментальное исследование графа переходов счетчиков и экспериментальная оценка динамических параметров счетчиков.

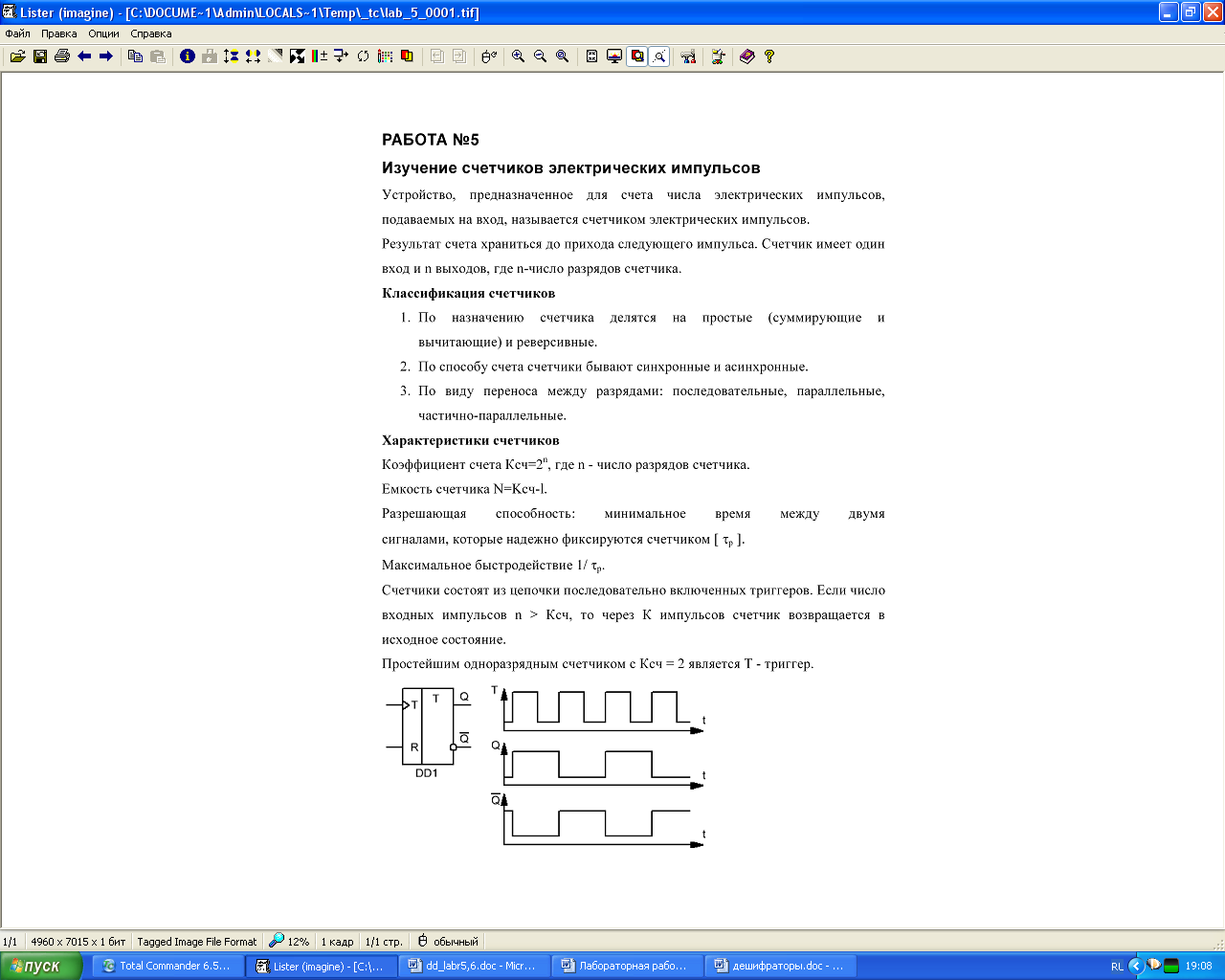

Теоретическая часть.

Счетчик - это устройство, предназначенное для счета числа импульсов, поступающих на его вход, и фиксации этого числа. Результат счета хранится до прихода следующего импульса. Счетчик имеет один вход и n выходов, где n - число разрядов счетчика.

Классификация счетчиков:

-

По назначению счетчики делятся на простые (суммирующие и вычитающие) и реверсивные.

-

По способу счета счетчики бывают синхронные и асинхронные.

-

По виду переноса между разрядами: последовательные, параллельные, частично - параллельные.

Характеристики счетчиков:

-

Коэффициент счета Ксч =

, где n - число разрядов счетчика.

, где n - число разрядов счетчика. -

Емкость счетчика N = Ксч - 1.

-

Разрешающая способность: минимальное время между двумя сигналами, которое надежно фиксируется счетчиком (

).

). -

Максимальное быстродействие

.

.

Счетчики состоят из цепочки последовательно включенных триггеров. Если число входных импульсов больше коэффициента счета, то через К импульсов счетчик возвращается в исходное состояние.

Порядок выполнения работы:

Задание 1. Исследование одноразрядного счетчика.

-

Соберите простейший одноразрядный счетчик. Т - триггер.

-

Проверьте работу счетчика, подключив к прямому выходу разряда световой индикатор.

-

Подайте на вход счетчика импульсы с выхода генератора.

-

Посмотреть на экране осциллографа диаграммы сигналов на входе и выходах счетчика, зарисовать их и измерить их параметры.

-

Определите характеристики счетчика.

-

Составьте таблицу переходов и граф переходов счетчика.

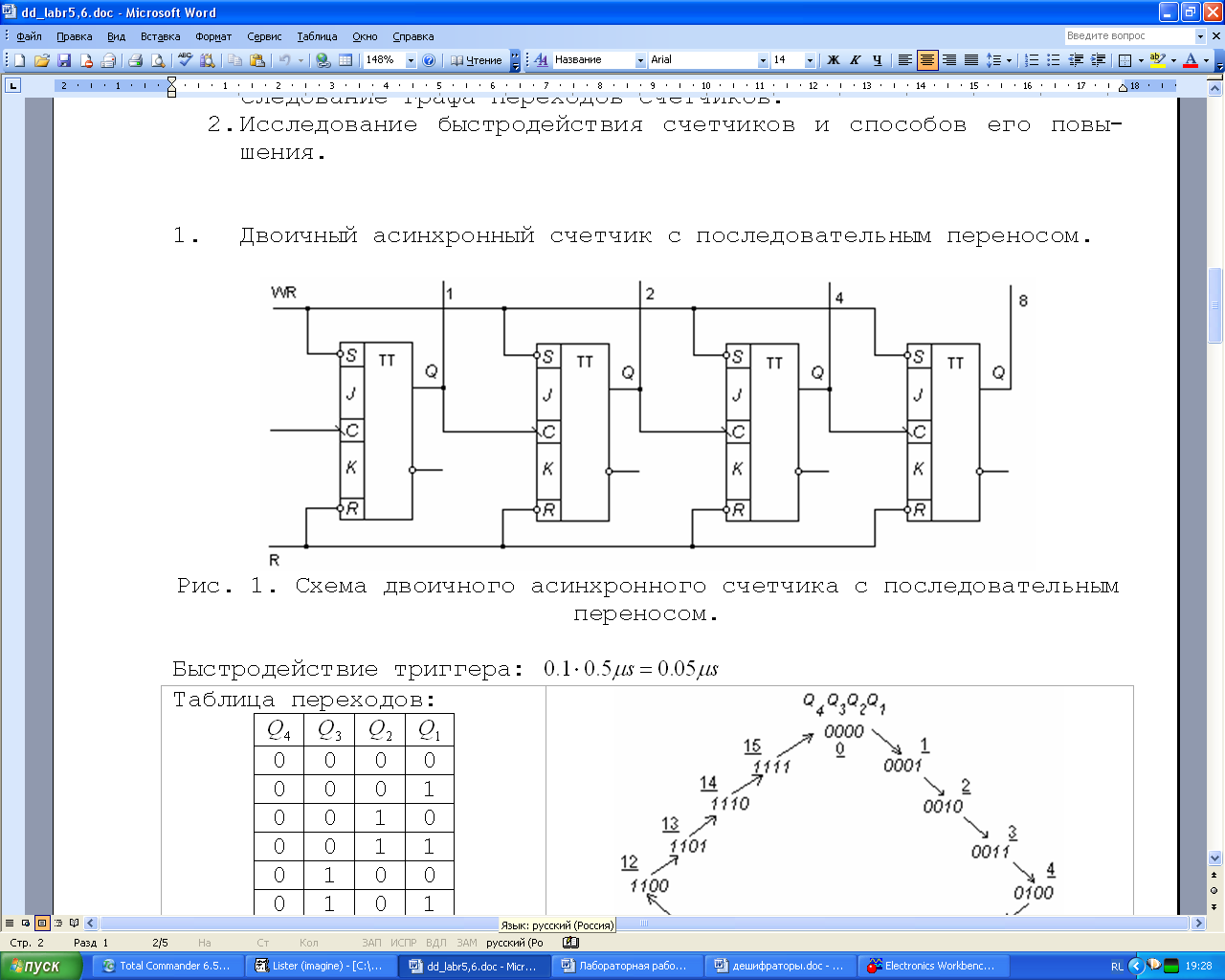

Задание 2. Исследование двоичного асинхронного счетчика с последовательным переносом.

-

Соберите четырехразрядный суммирующий счетчик с последовательным переносом.

-

На входы J и K подайте логическую единицу.

-

Проверьте работу счетчика, подключив к прямому выходу каждого разряда световые индикаторы.

-

Подайте на вход счетчика импульсы с выхода генератора.

-

Посмотреть на экране осциллографа диаграммы сигналов на входе и выходах счетчика, зарисовать их и измерить их параметры.

-

Определите характеристики счетчика.

-

Составьте таблицу переходов и граф переходов счетчика.

Задание 3. Исследование работы вычитающего счетчика.

-

Соберите вычитающий счетчик на D - триггерах.

-

Посмотреть на экране осциллографа диаграммы сигналов на входе и выходах счетчика, зарисовать их и измерить их параметры.

-

Составьте таблицу переходов и граф переходов счетчика.

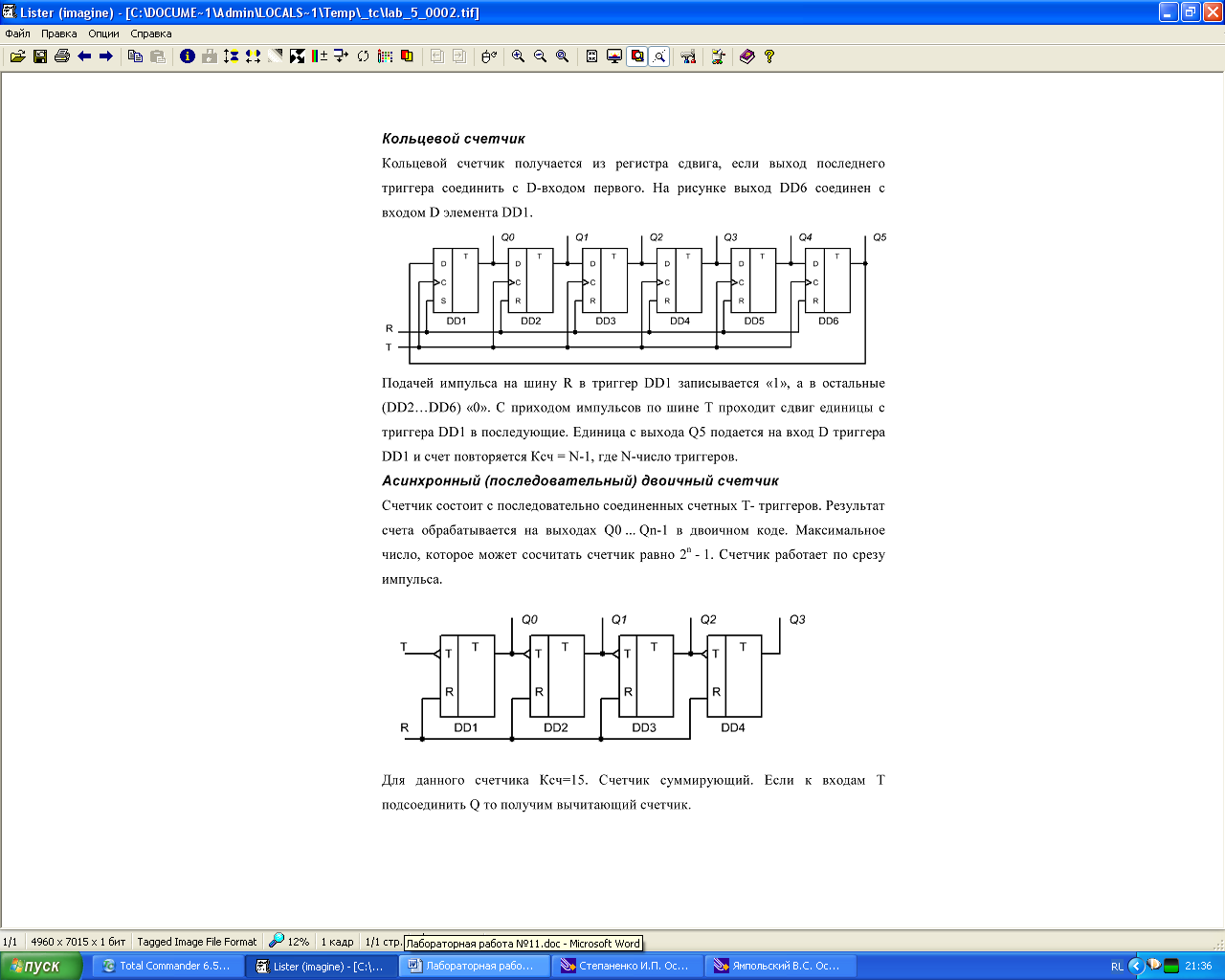

Задание 4. Исследование работы кольцевого счетчика.

1. Получите кольцевой счетчик из регистра сдвига, соединив выход последнего триггера с D - входом первого.

-

Проверьте работу счетчика, подключив к прямому выходу каждого разряда световые индикаторы.

-

Подайте на вход счетчика импульсы с выхода генератора.

-

Посмотреть на экране осциллографа диаграммы сигналов на входе и выходах счетчика, зарисовать их и измерить их параметры.

-

Определите коэффициент счета Ксч = N, где N - количество триггеров в цепочке.

-

Составьте таблицу переходов и граф переходов счетчика.

Задание 5. Исследование работы синхронного вычитающего счетчика.

1. Соберите синхронный вычитающий счетчик.

-

Проверьте работу счетчика, подключив к прямому выходу каждого разряда световые индикаторы.

-

Подайте на вход счетчика импульсы с выхода генератора.

-

Посмотреть на экране осциллографа диаграммы сигналов на входе и выходах счетчика, зарисовать их и измерить их параметры.

-

Определите коэффициент счета Ксч = N, где N - количество триггеров в цепочке.

-

Составьте таблицу переходов и граф переходов счетчика.

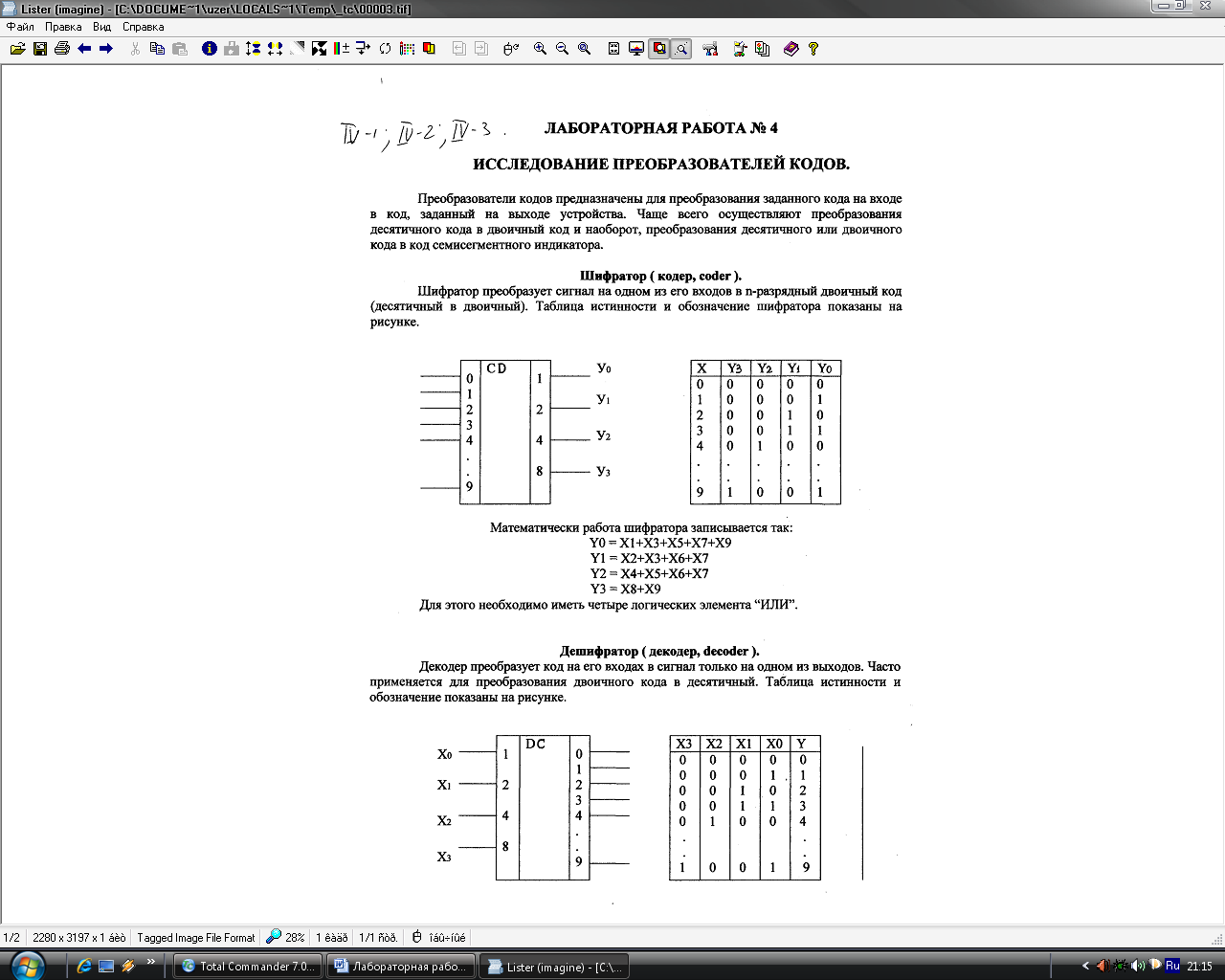

Практическая работа №7 «Исследование работы дешифраторов и шифраторов. Реализация логических функций на дешифраторах»

Изучение принципов построения и методов синтеза дешифраторов; макетирование и экспериментальное исследование дешифраторов.

Теоретическая часть.

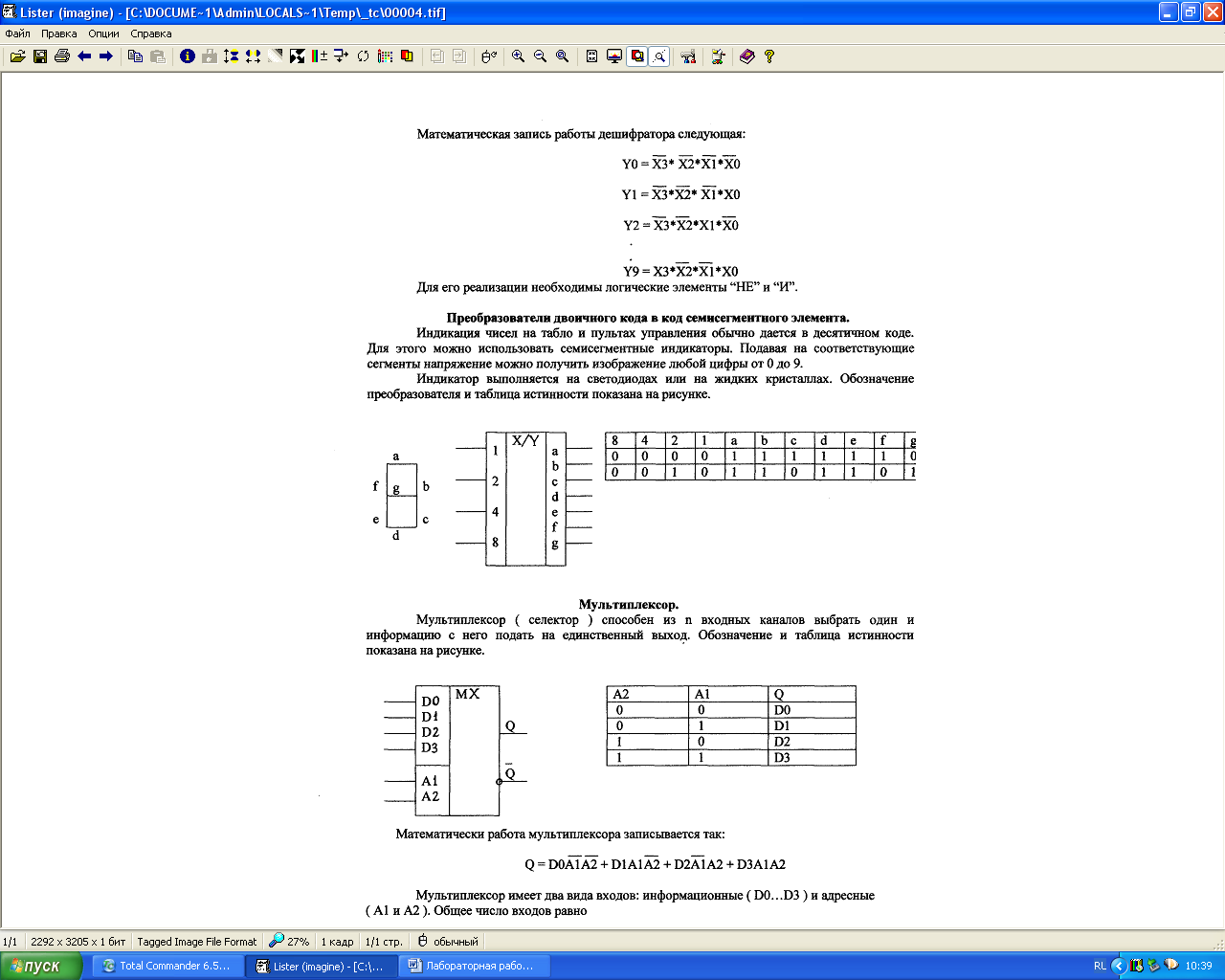

Дешифратор преобразует код на его входах в сигнал только на одном из выходов. Часто применяется для преобразования двоичного кода в десятичный. Таблица истинности и обозначение показаны на рисунке.

Математическая запись работы дешифратора следующая:

Для его реализации необходимы логические элементы «НЕ» и «И».

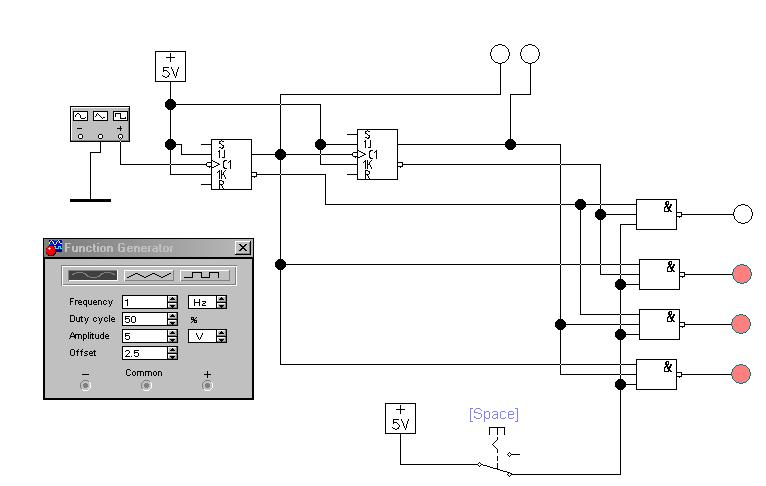

Порядок выполнения работы.

1. Исследование линейного двухвходового дешифратора.

1. Соберите схему линейного двухвходового дешифратора на элементах И-НЕ. Входные сигналы подавайте с выхода счетчика, построенного на JK-триггерах. Наблюдайте сигналы на выходе.

2. Постройте таблицу истинности дешифратора.

A0

A1

F0

F1

F2

F3

3. Увеличивая частоту, наблюдайте, что происходит в работе дешифратора.

4. Рассмотрите схему, изображенную на рисунке. Здесь используется линия задержки из трех элементов для того, чтобы разрешающий сигнал пришел на все элементы И-НЕ в тот момент, когда на них уже будут сформированы правильные сигналы.

5. Наблюдайте сигналы на выходе.

6. Определите с помощью осциллографа время задержки.

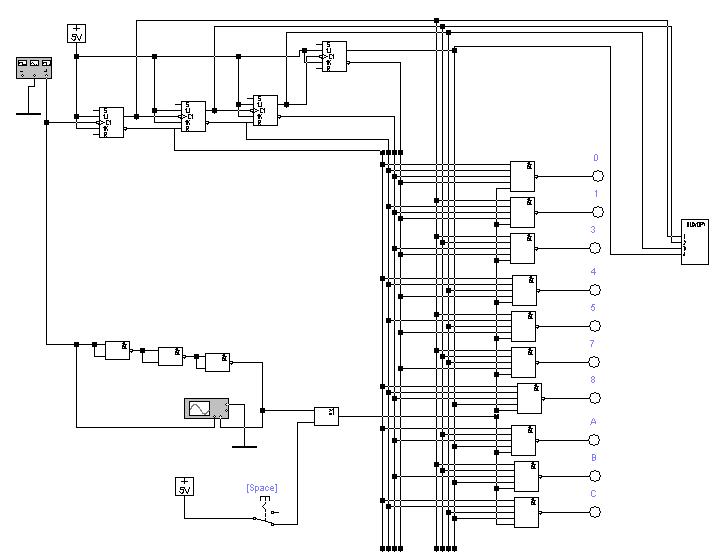

2. Исследование дешифратора двоично-десятичного кода.

1. Постройте схему дешифратора двоично-десятичного кода, разрешающего сигналы:

0, 1, 3, 4, 5, 7, 8, 10, 11, 12

Для проверки правильности работы используйте дисплей, показывающий значение двоичного кода на входе схемы.

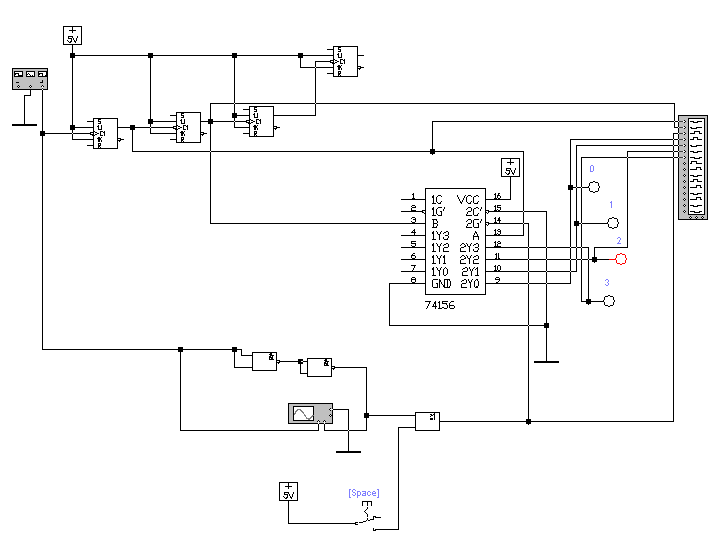

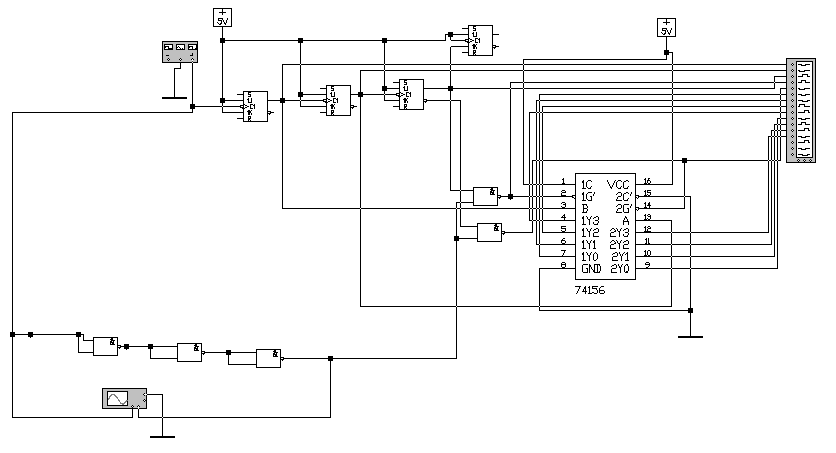

3. Исследование дешифратора К155ИД4.

1. Соберите схему, аналогично пункту 1, только заменив дешифратор на К155ИД4.

Данный дешифратор использует инверсный сигнал синхронизации, поэтому число элементов линии задержки должно быть четным.

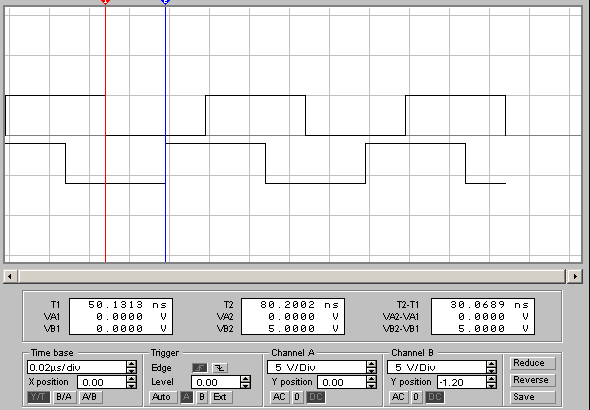

2. Наблюдайте сигналы на выходе, не используя линию задержки.

3. Включите два элемента И - НЕ в линию задержки. Наблюдайте пропадание гонки сигналов.

4. Измерьте время задержки.

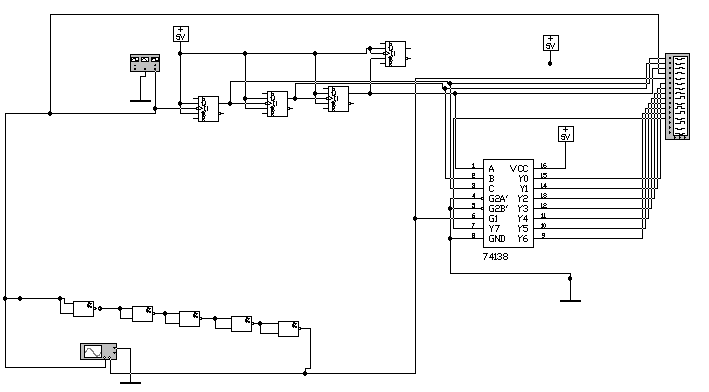

4. Исследование дешифратора К155ИД4 для схемы с тремя входами.

1. В схеме К155ИД4 находятся два дешифратора. Можно включить их таким образом, что они образуют дешифратор с тремя входами.

Происходит дополнительный выбор первой или второй схемы дешифратора из-за этого инвертируется синхросигнал и число элементов линии задержки должно быть нечетным.

2. Измерьте время задержки.

5. Исследование дешифратора К155ИД7.

1. Дешифратор схемы К155ИД7 имеет три входа.

Для нормальной работы необходимо 5 элементов И-НЕ в линии задержки.

Это требует уменьшения рабочей частоты до 1 МГц, чтобы задержанные сигналы не пересекались с незадержанными.

2. Измерьте время задержки.

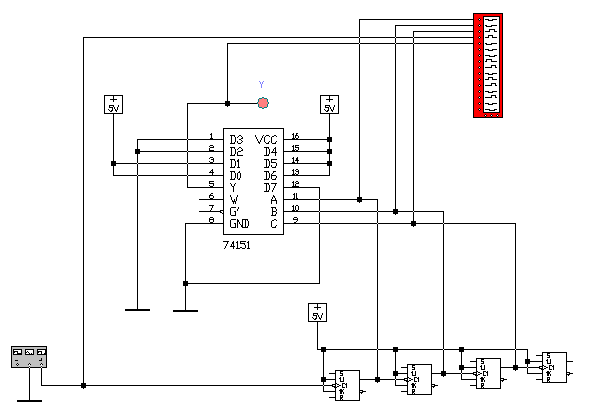

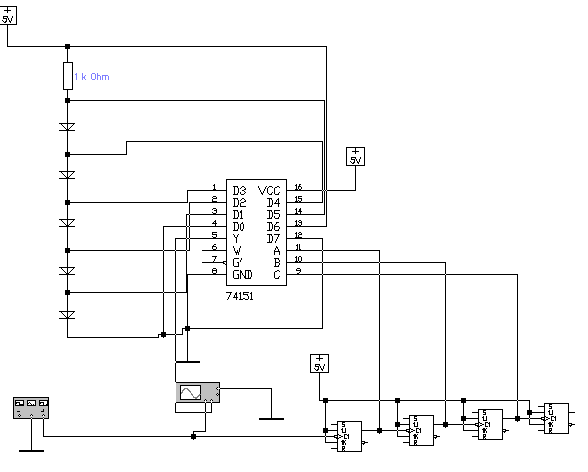

Практическая работа №8 «Исследование работы мультиплексоров и демультиплексоров»

Цель работы:

Изучение принципов построения и практического применения, макетирование и экспериментальные исследования мультиплексоров.

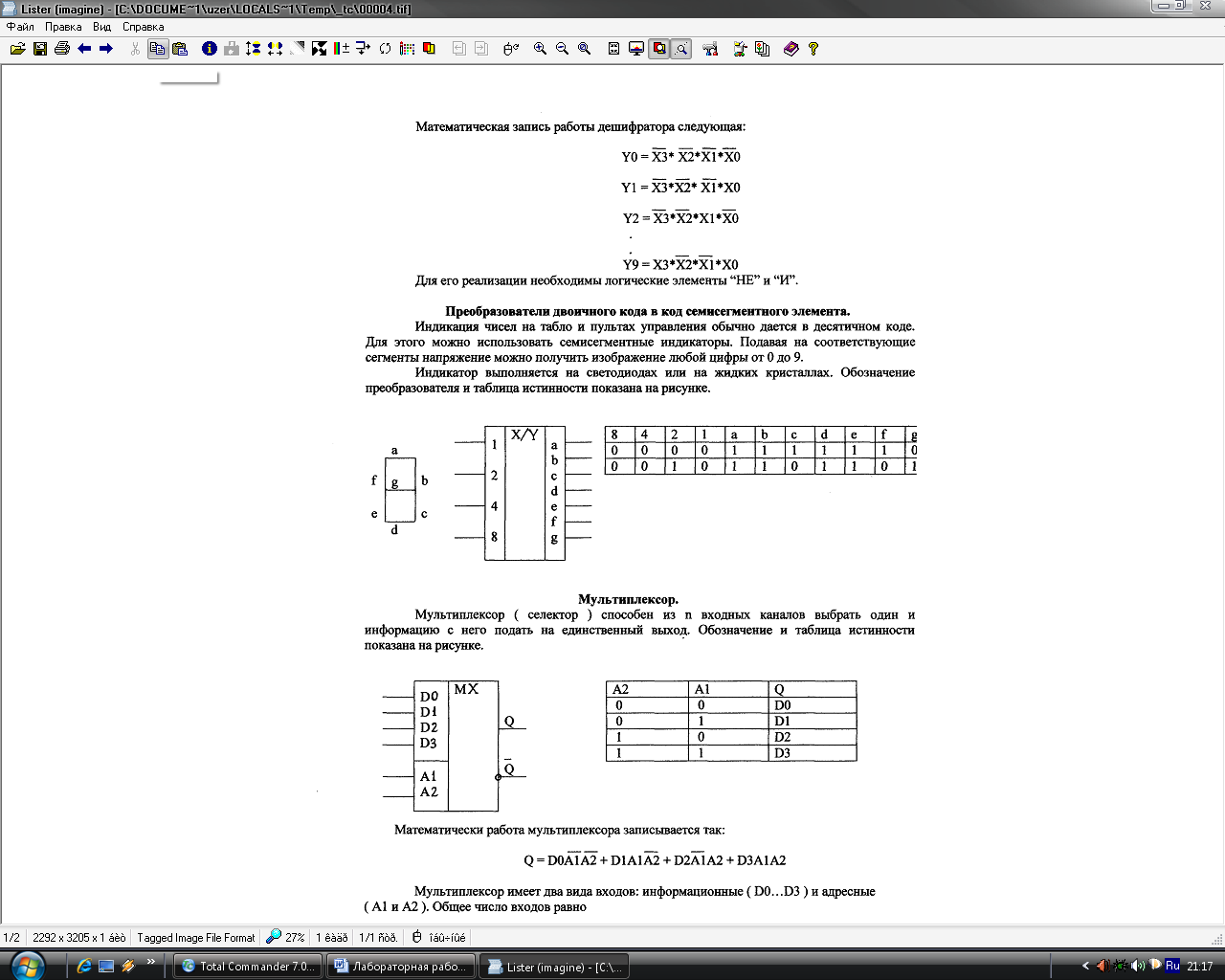

Теоретическая часть.

Мультиплексор (селектор) способен из n входных каналов выбрать один и информацию с него подать на единственный выход. Обозначение и таблица истинности показана на рисунке.

Математически работа мультиплексора записывается так

Мультиплексор имеет два вида входов: информационные (![]() ) и адресные (

) и адресные ( и

и  ). Общее число входов равно

). Общее число входов равно ![]() , где A - число адресных входов, 2 - число информационных входов. Если двоичный код на адресных входах совпадает с номером информационного входа, то он подключается к выходу

, где A - число адресных входов, 2 - число информационных входов. Если двоичный код на адресных входах совпадает с номером информационного входа, то он подключается к выходу  .

.

Порядок выполнения работы.

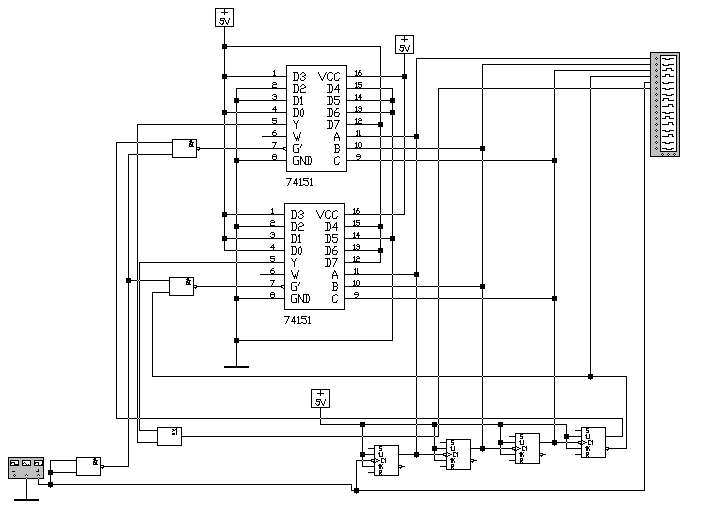

1. Исследование 564КП2 8-канального мультиплексора как преобразователя последовательного кода в параллельный.

1. Соберите схему, указанную на рисунке.

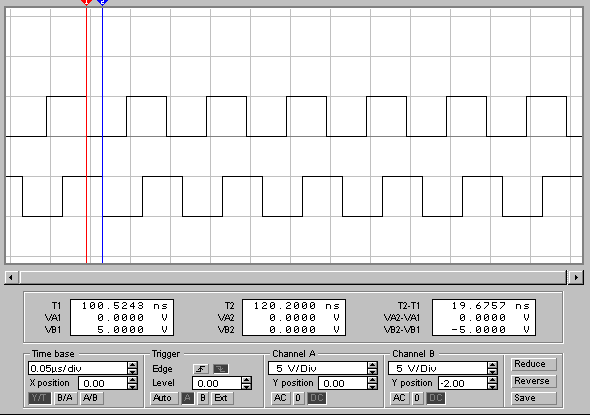

2. Установите частоту синхросигнала 10 КГц.

3. На вход подайте сигнал 11001110.

4. Наблюдайте последовательность сигналов на выходе. Рассмотрите временную диаграмму.

2. Исследование 564КП2 при меньшем уровне информационных сигналов.

1. Соберите схему.

2. Рассмотрите временную диаграмму.

3. Исследование 564КП2 в качестве генератора логической функции 4-х аргументов.

1. Соберите схему.

Данная схема состоит из двух каскадно-включенных мультиплексоров. Для более четкого выделения сигналов добавлено стробирование. Схема синтезирует логическую функцию (0, 3, 7, 8, 9, 11, 12, 14, 15).

2. Рассмотрите временную диаграмму для частоты 10 Гц (можно считать статическим режимом).

3. Постройте таблицу истинности.

A3

A2

A1

A0

C

F

4. Увеличивая рабочую частоту, следите за работой схемы.

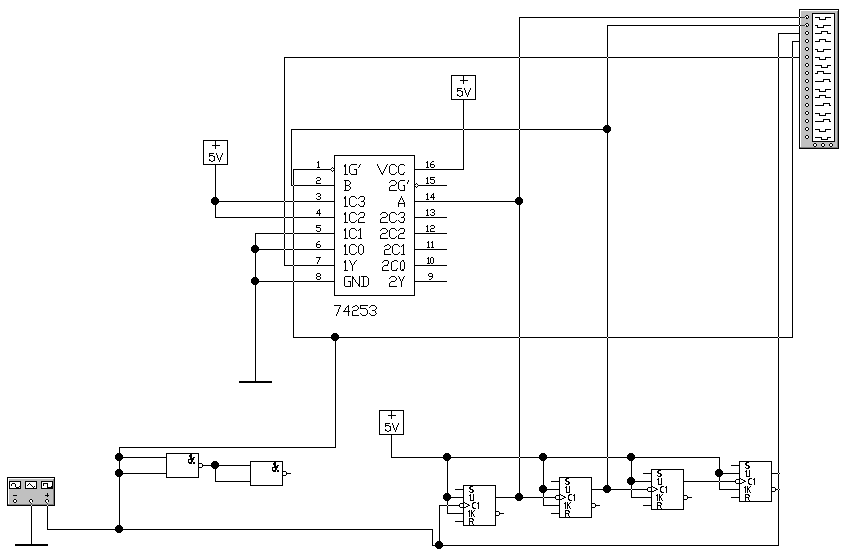

4. Исследование 533КП12 в качестве стробированного коммутатора цифровых сигналов.

1. Соберите схему.

Подключено стробирование без задержки.

Схема синтезирует логическую функцию (0, 0, 1, 1).

2. Рассмотрите временную диаграмму для частоты 10 МГц.

3. Наблюдайте ложные сигналы, вызванные задержками в схемы счетчика.

4. Добавьте линию задержки в линию стробирования. Рассмотрите временную диаграмму.

5. Измерьте время задержки.

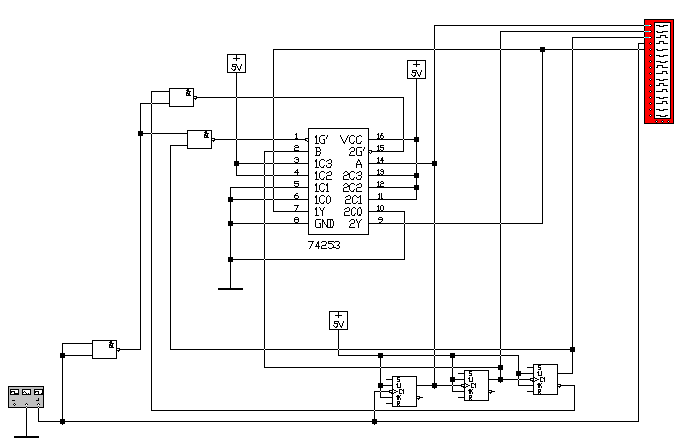

5. Построение мультиплексора 8-1 на базе 533КП12.

1. Соберите схему.

Схема требует минимум двух элементов в линии стробирования для выбора одного из двух мультиплексоров и для инвертирования сигнала для получения его правильной формы. Выходы в высокоимпедансном состоянии можно коммутировать непосредственно друг с другом, обеспечив при этом активность только одной входной линии. Схема выдает сигнал функции (0, 0, 1, 1, 0, 1, 1, 1).

2. Рассмотрите временные диаграммы.

Практическая работа №9 «Исследование работы сумматоров»

Цель: Изучить алгоритм работы полного одноразрядного двоичного сумматора.

Теоретическая часть.

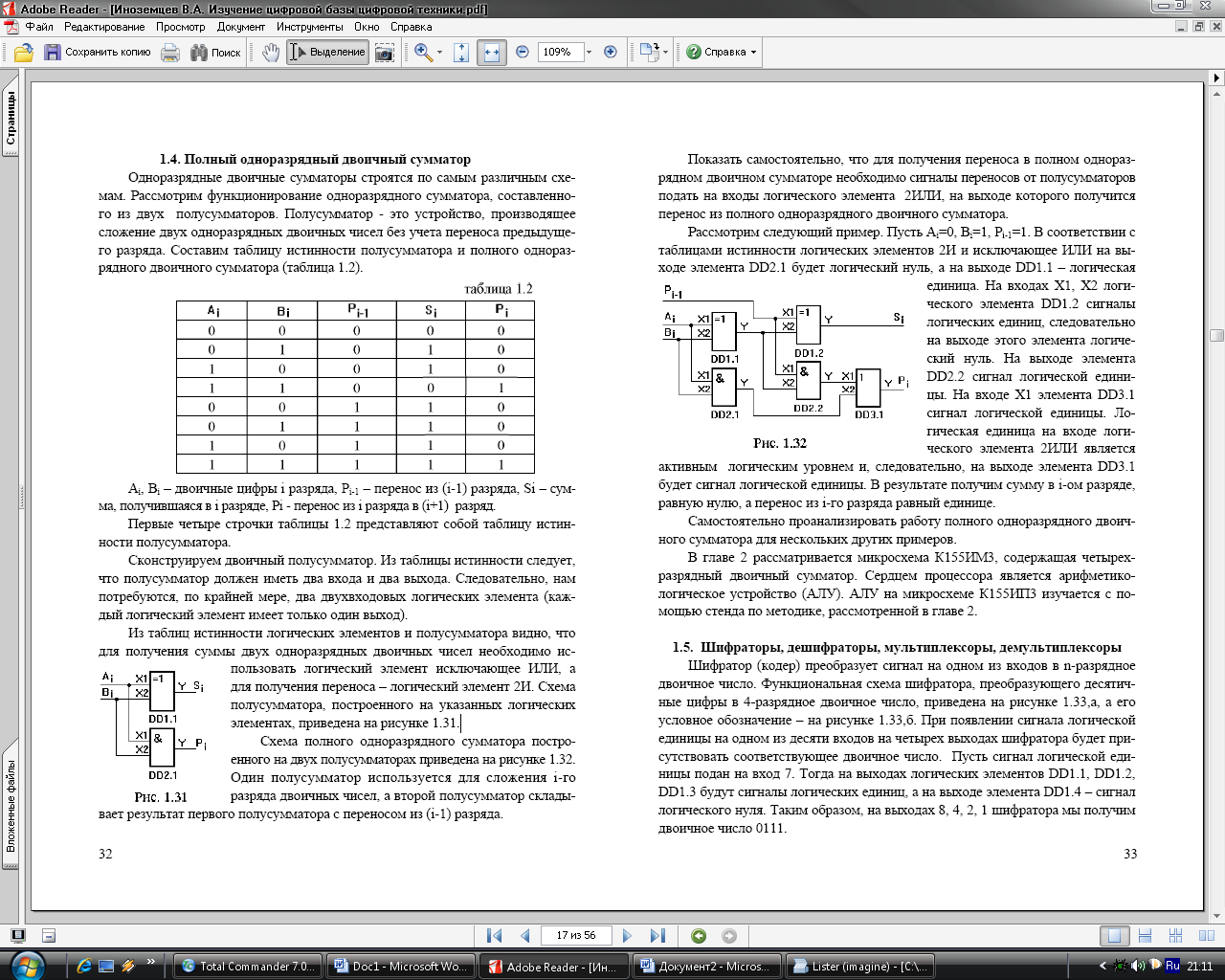

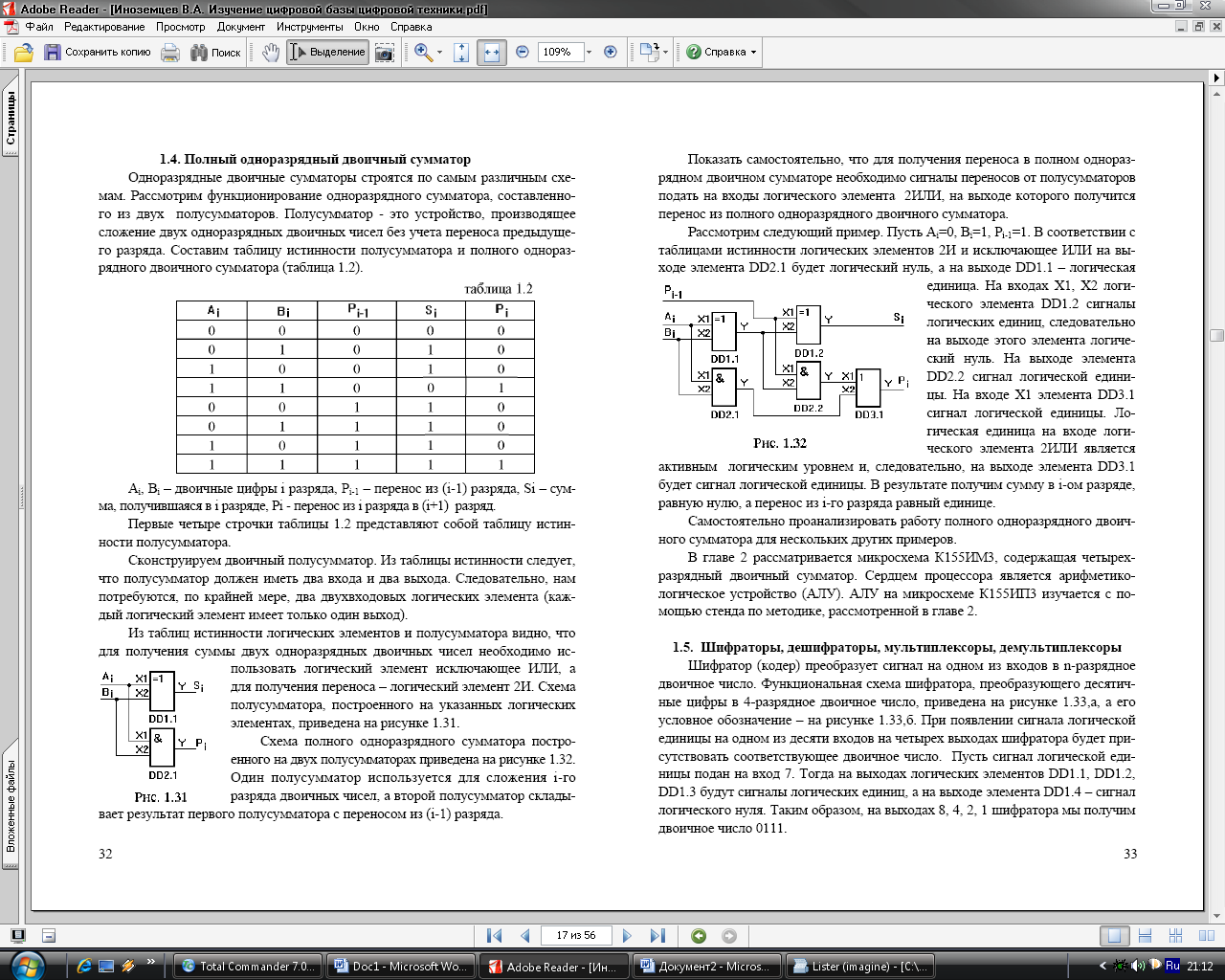

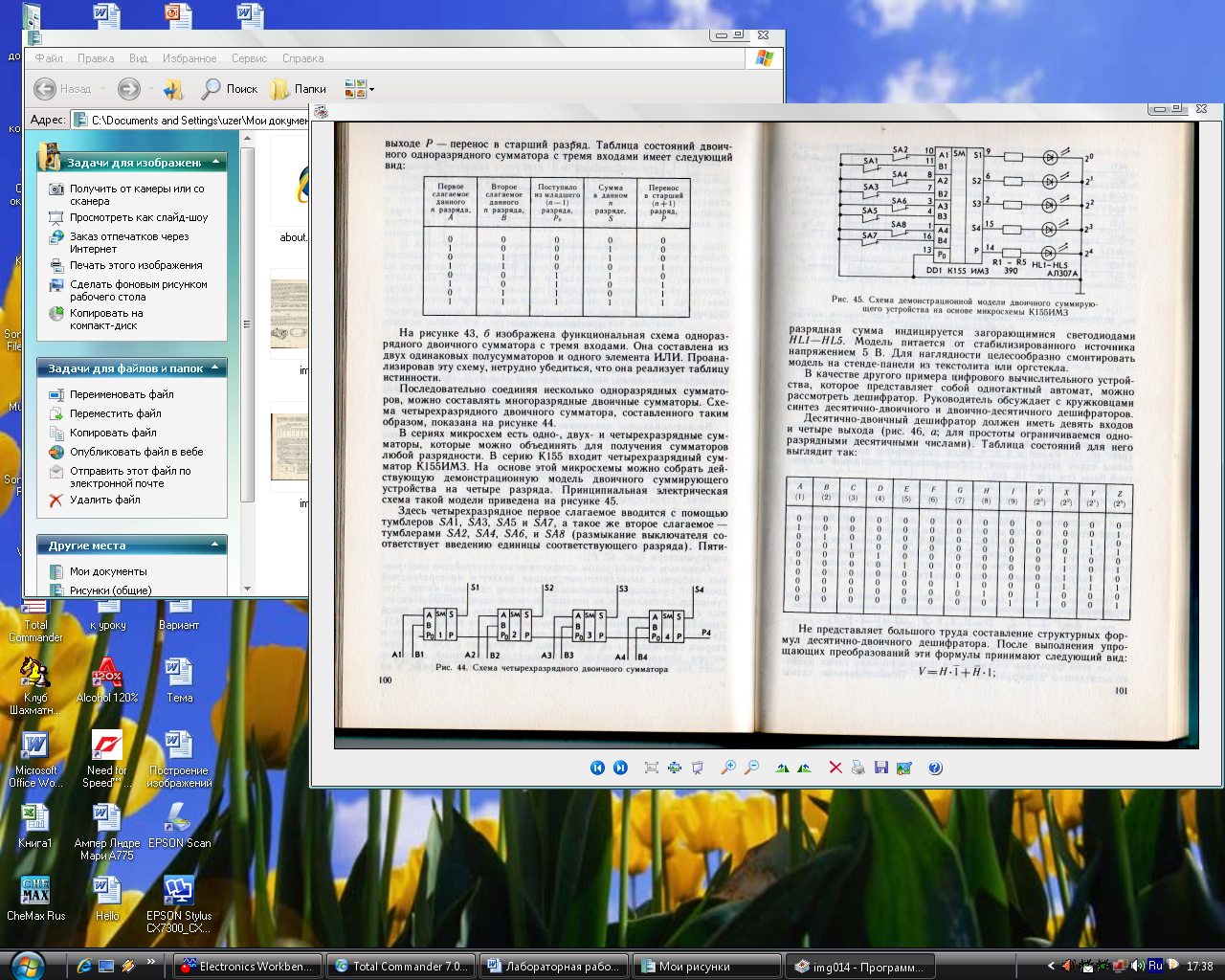

Одноразрядные двоичные сумматоры строятся по самым различным схемам. Рассмотрим функционирование одноразрядного сумматора, составленного из двух полусумматоров. Полусумматор - это устройство, производящее сложение двух одноразрядных двоичных чисел без учета переноса предыдущего разряда.

Сконструируем двоичный полусумматор. Из таблицы истинности следует, что полусумматор должен иметь два входа и два выхода. Следовательно, нам потребуются, по крайней мере, два двухвходовых логических элемента (каждый логический элемент имеет только один выход).

Из таблиц истинности логических элементов и полусумматора видно, что для получения суммы двух одноразрядных двоичных чисел необходимо использовать логический элемент исключающее ИЛИ, а для получения переноса - логический элемент 2И. Схема полусумматора, построенного на указанных логических элементах, приведена на рисунке 1.31.

Схема полного одноразрядного сумматора построенного на двух полусумматорах приведена на рисунке 1.32. Один полусумматор используется для сложения i-го разряда двоичных чисел, а второй полусумматор складывает результат первого полусумматора с переносом из (i-1) разряда.

Ai, Bi - двоичные цифры i разряда, Pi-1 - перенос из (i-1) разряда, Si - сумма, получившаяся в i разряде, Pi - перенос из i разряда в (i+1) разряд.

Рассмотрим следующий пример. Пусть Аi=0, Вi=1, Pi-1=1. В соответствии с таблицами истинности логических элементов 2И и исключающее ИЛИ на выходе элемента DD2.1 будет логический нуль, а на выходе DD1.1 - логическая единица. На входах Х1, Х2 логического элемента DD1.2 сигналы логических единиц, следовательно на выходе этого элемента логический нуль. На выходе элемента DD2.2 сигнал логической единицы. На входе Х1 элемента DD3.1 сигнал логической единицы. Логическая единица на входе логического элемента 2ИЛИ является активным логическим уровнем и, следовательно, на выходе элемента DD3.1 будет сигнал логической единицы. В результате получим сумму в i-ом разряде, равную нулю, а перенос из i-го разряда равный единице.

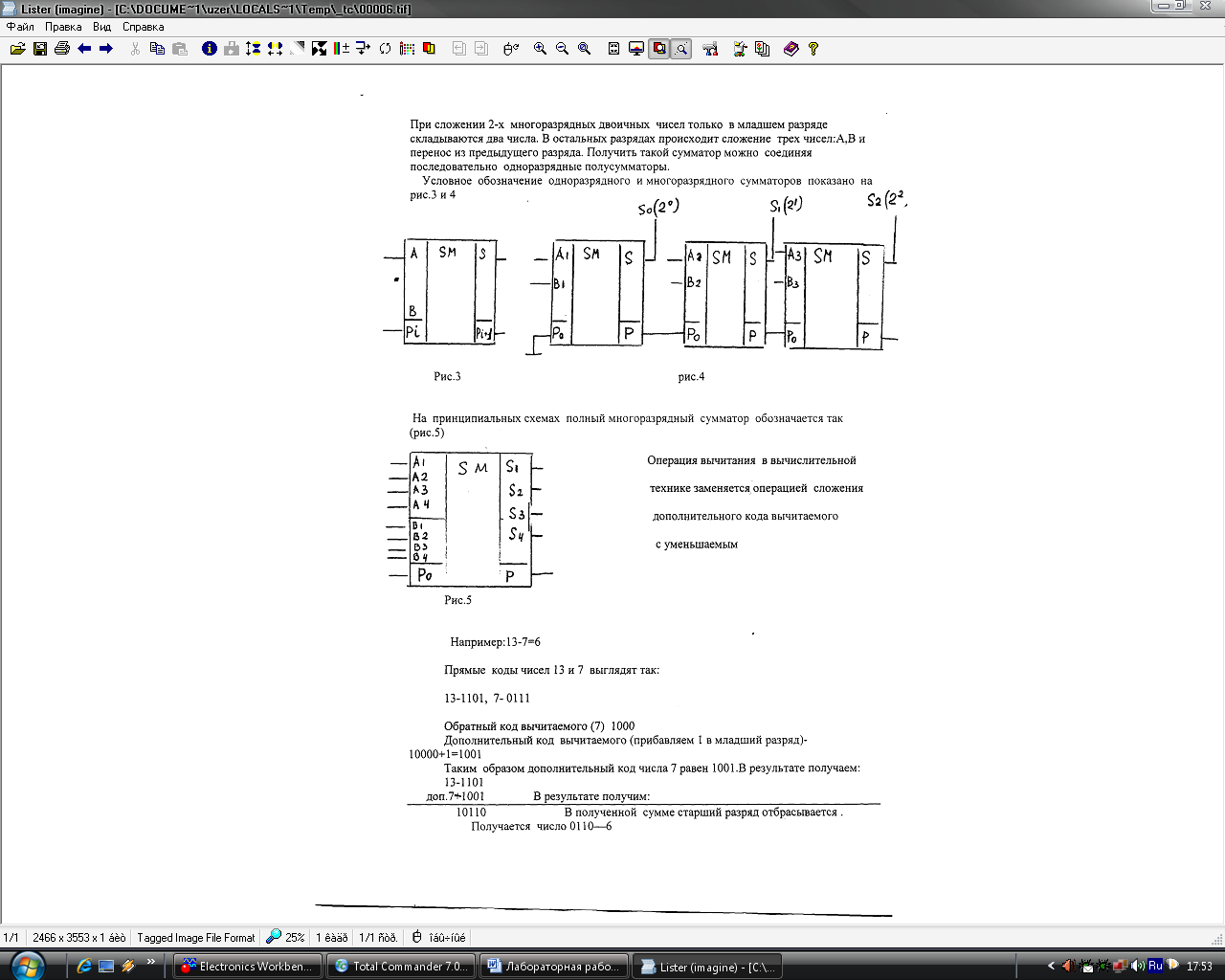

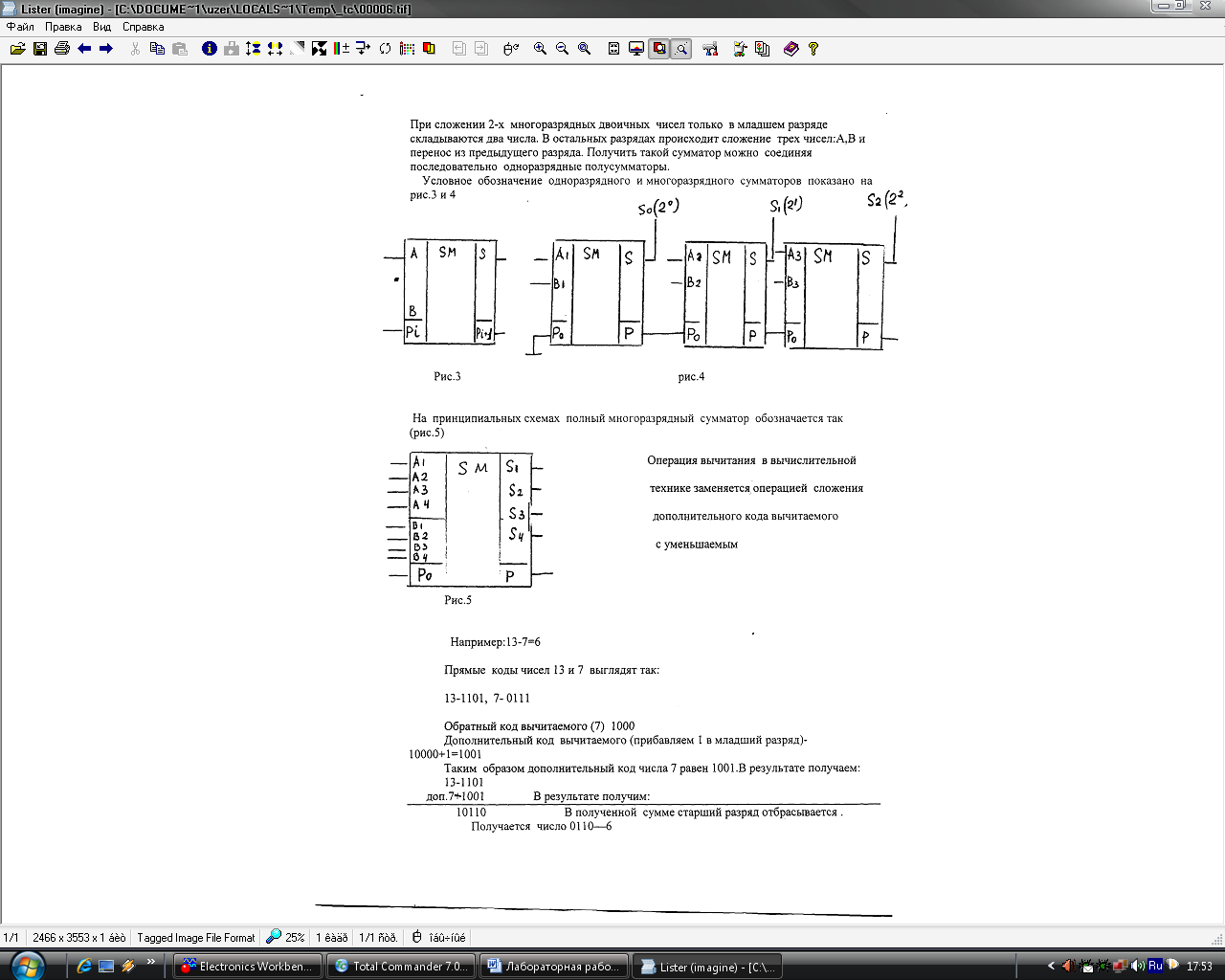

Последовательно соединяя несколько одноразрядных сумматоров, можно составлять многоразрядные двоичные сумматоры.

Условное обозначение одноразрядного и многоразрядного сумматоров показано на рисунках а) и б):

рис. а) рис. б)

На принципиальных схемах полный многоразрядный сумматор обозначается так:

Операция вычитания в вычислительной технике заменяется операцией сложения дополнительного кода вычитаемого с уменьшаемым. Например,

7 - 6 = 1

Прямые коды чисел 7 и 6 выглядят так:

7 - 0111, 6 - 0110.

Обратный код вычитаемого (6) - 1001 (заменяем единицы нулями и наоборот).

Дополнительный код вычитаемого (прибавляем единицу в младший разряд) - 1001 + 1 = 1010.

Таким образом, дополнительный код числа 6 равен 1010. В результате получаем:

0111 + 1010 = 10001.

Отбрасывая в полученной сумме старший разряд, получаем число:

0001 - 1.

Порядок выполнения работы.

Задание №1. Изучение работы полусумматора.

1. Соберите схему:

-

Составьте таблицу истинности полусумматора.

Ai

Bi

Si

Pi

Задание №2. Исследование работы полного одноразрядного двоичного сумматора.

-

Соберите схему, указанную на рисунке и зарисуйте ее в тетрадь.

-

Составьте таблицу истинности одноразрядного двоичного сумматора.

Ai

Bi

Pi-1

Si

Pi

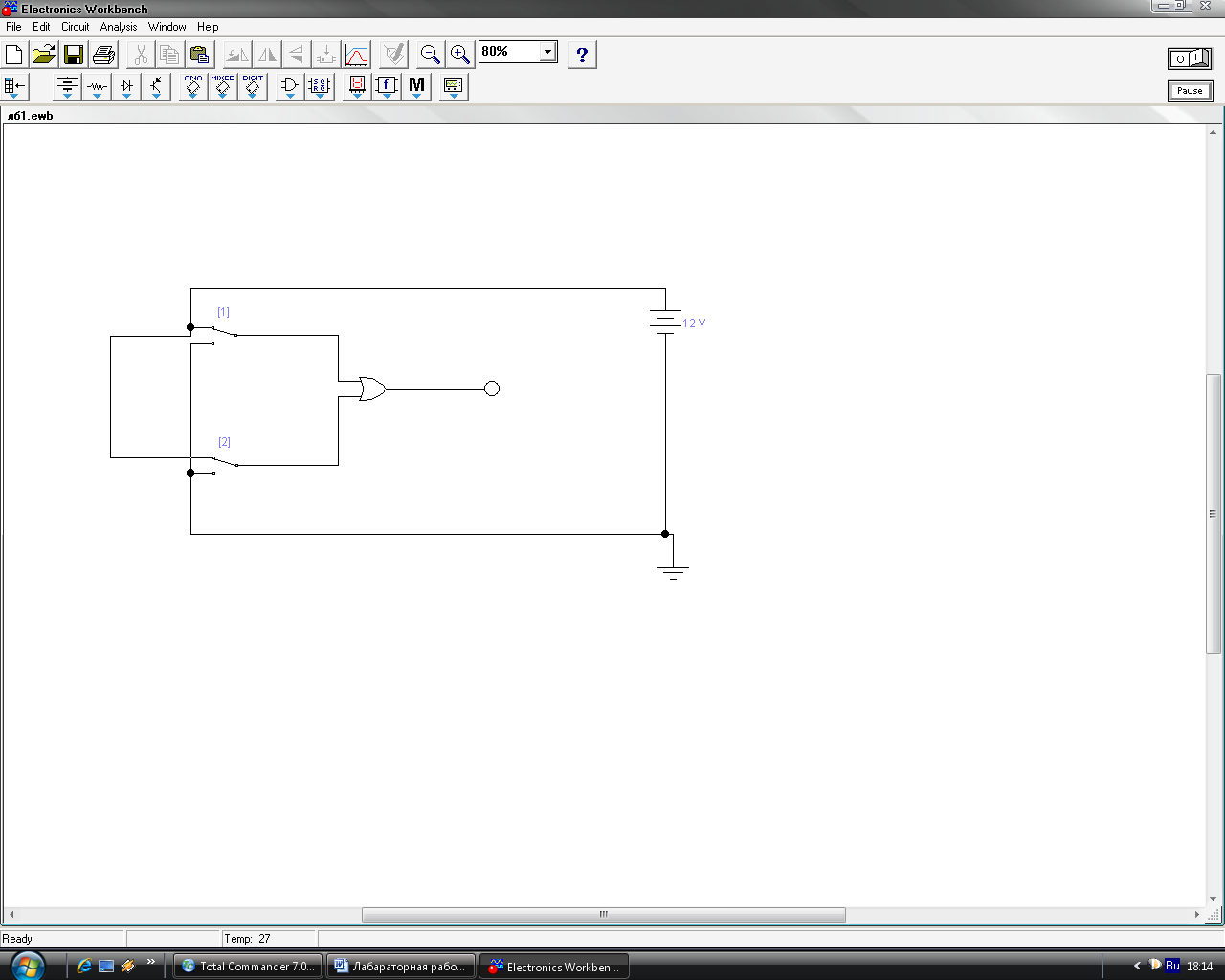

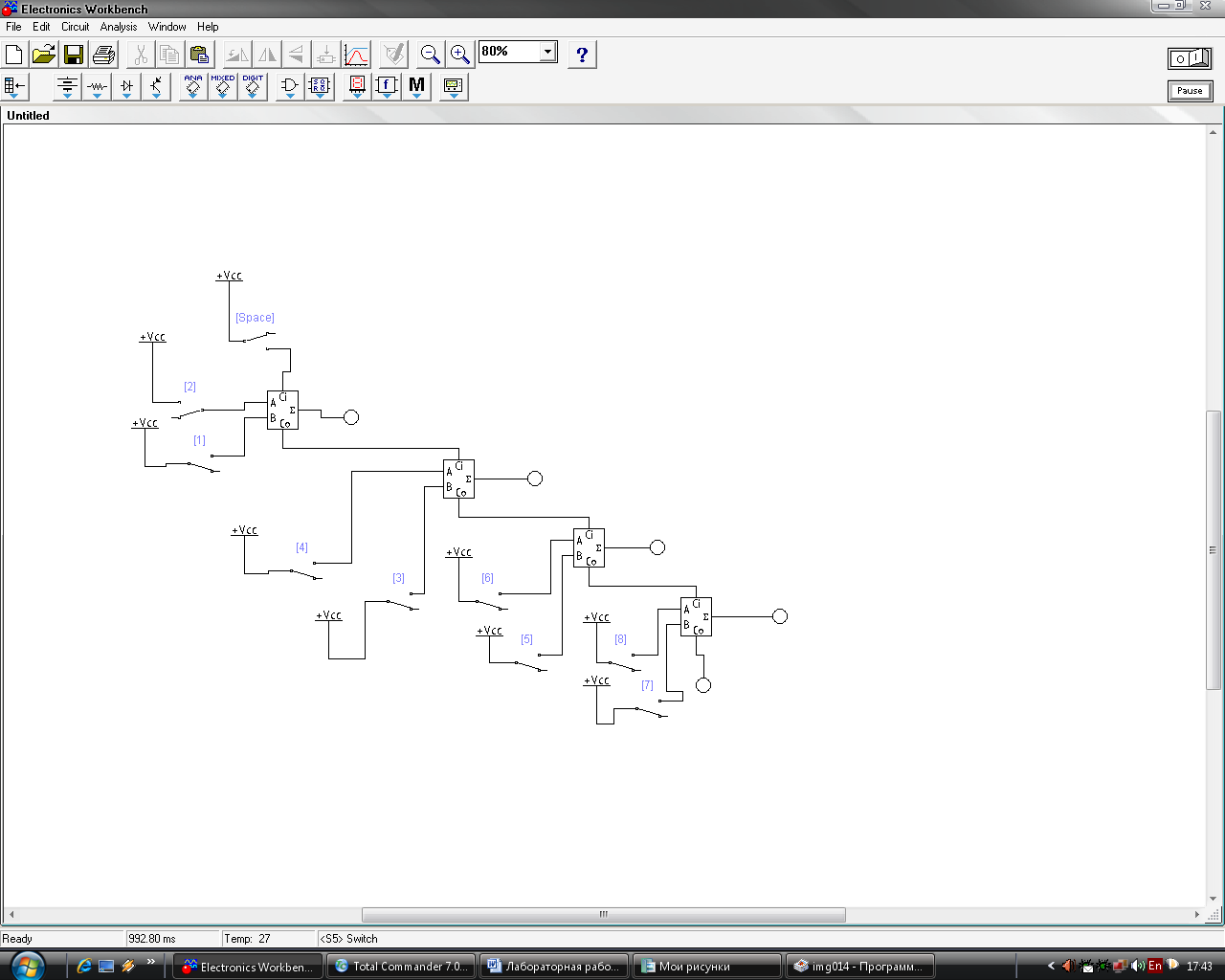

Задание №3. Исследование работы четырехразрядного двоичного сумматора.

Схема четырехразрядного двоичного сумматора показана на рисунке.

-

Соберите схему:

Здесь четырехразрядное первое слагаемое вводится с помощью ключей [1], [3], [5], [7], а такое же второе слагаемое - ключами [2], [4], [6], [8].

-

Выполнить в тетради суммирование четырехрядных чисел в двоичном коде. Результаты проверить на схеме.

Варианты 1 -10.

-

7 + 5, 8 +3

-

6 + 4, 5 + 8

-

2 +3, 3 + 4

-

4 + 5, 5 + 6

-

10 + 3, 3 + 9

-

4 + 11, 2 + 9

-

11 + 3, 10 + 2

-

9 +5 , 7 + 3,

-

7 + 7, 5 + 2

10) 8 +6, 2 + 4.

-

Выполнить в тетради операцию вычитания четырехрядных чисел в двоичном коде с применением для вычитаемого дополнительного кода.

Варианты 1 - 10.

-

12 -5, 11 - 3

-

13 - 10, 14 - 3

-

10 - 4, 13 - 8

-

7 - 4, 12 - 9

-

14 - 7, 5 - 2

-

13 - 2, 9 - 5

-

15 - 4, 14 - 9

-

11 - 5, 12 - 9

-

10 - 3, 12 - 3

10) 9 - 4, 7 - 3.

Лабораторная работа №2 «Исследование работы цифро-аналогового преобразователя (ЦАП)»

Цель работы: Исследовать различные типы преобразователей. Закрепить теоретические знания о различных типах ЦАП и АЦП, их назначении, устройстве и принципах работы.

Используемое оборудование и средства: персональный компьютер, программа Electronics Workbench

Работа выполняется студентами за два часа аудиторных занятий.

Краткие теоретические сведения.

Цифро-аналоговые преобразователи используются для преобразования цифрового кода в аналоговый сигнал, например, для управления в автоматических системах исполнительными органами (электродвигателями, соленоидами и т.п.).

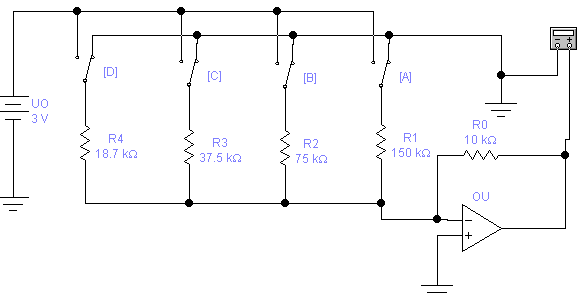

Наиболее простой ЦАП с весовыми резисторами (рис.1.) состоит из двух блоков. Резистивная схема (матрица) выполнена на резисторах R1…R4. Суммирующий усилитель включает в себя OU и резистор обратной связи R0. Опорное напряжение U0n (3 В) подключается к резисторам матрицы переключателями D, C, B и A, управляемым одноименными клавишами клавиатуры и имитирующими преобразуемый код. Выходное напряжение U0 измеряется мультиметром.

Рис. 15.1. Цап с весовыми резисторами

Если все переключатели замкнуты на "землю", как показано на рис.1, то напряжение на входе и выходе ОУ равно 0 В. Предположим теперь, что переключатель А установлен в положение, соответствующее логической 1.Тогда на вход ОУ через резистор R1 подается напряжение 3 B. Рассчитаем в этом случае коэффициент усиления напряжения по формуле:

K=R0/R1=10000/150000=0,066.

Отсюда получаем, что выходное напряжение U0=0,066*3=0.2 B соответствует двоичной комбинация 0001 на входе ЦАП.

Подадим теперь на входы ЦАП двоичную комбинацию 0010. Для этого установим переключатель B в положение, соответствующее логической единице, тем самым подадим на ОУ через резистор R2 напряжение 3 B. Для коэффициента усиления в данном случае получаем

К=R0/R2=10000/75000=0.535.

Умножив этот коэффициент усиления на величину входного напряжения, найдем, что выходное напряжение равно 0,4 B.

Таким образом, при переходе к каждому очередному двоичному числу, имитируемому ключами, выходное напряжение ЦАП увеличивается на 0,2 B. Это обеспечивается за счет увеличения коэффициента усиления напряжения ОУ при подключении различных по сопротивлению резисторов. Если в схеме на рис .1 мы подключили бы только один резистор R4 (с помощью переключателя D), то тем самым установили бы коэффициент усиления:

К=10000/18700=0.133

При этом выходное напряжение ОУ составит около 1,6 B.

Если все переключатели в схеме на рис. 1 установлены в положения, соответствующее логическим единицам, выходное напряжение ОУ равно U0n=3 B, поскольку коэффициент передачи в этом случае становится равным 1.

Схема цифро-аналогового преобразователя на рис. 1 имеет два недостатка: во-первых, в ней сопротивления резисторов изменяются в широких пределах, во-вторых, точность преобразования невысока из-за влияния конечного сопротивления транзисторных ключей в открытом и закрытом состояниях.

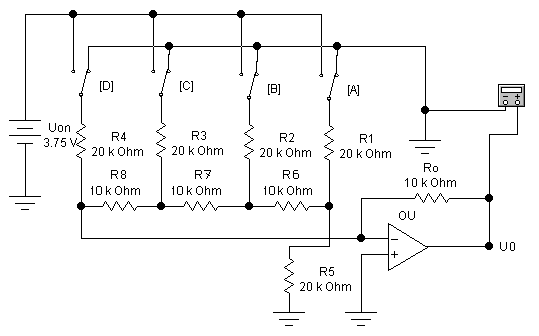

Схема ЦАП лестничного типа приведена на рис. 2. Она состоит из резистивной матрицы R-2R, напоминающей лестницу, и суммирующего усилителя. Преимущество такого соединения резисторов заключается в том, что используются резисторы только двух номиналов. Сопротивление каждого из резисторов R1…R5 равно 20кОм, а резисторов R6…R8,R0-10кОм.

Рис. 15.2. ЦАП лестничного типа.

ЦАП лестничного типа аналогичен ЦАП с весовыми резисторами. В рассматриваемом примере используется опорное напряжение 3,75 B. Переход к каждой следующей двоичной последовательности на входах приводит к увеличению аналогового выходного сигнала на 0,25 B. Опорное напряжение выбрано равным 3,75 B из соображения удобства сопряжения с ИМС семейства ТТЛ при замене ключей A…D такими ИМС.

Выходное напряжение ЦАП на рис. 2 определяется по формуле:

U0=U0nR0 [S12n-1 +S22n-2+…+Si2n-i+Sn2] /R2n , (1)

где Si - значение цифрового сигнала (0 или 1) на i-том входе, n-число разрядов преобразования (для схемы на рис.2 n = 4), R - сопротивление резистора матрицы R-2R (R = 10кОм для схемы на рис. 2).

Вариант ЦАП с использованием в качестве коммутирующего устройства двоично-десятичного счетчика 74160 (К155ИЕ9) показан на рис. 3.

Рис. 15.3. Четырехразрядный ЦАП лестничного типа на базе счетчика 74160.

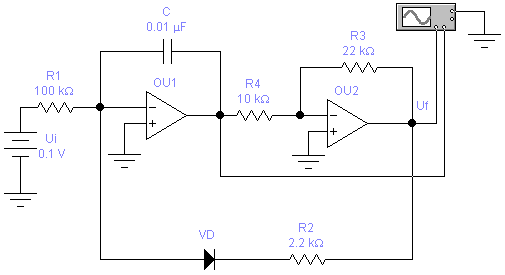

АЦП прямого преобразования являются наиболее простыми и часто встраиваются непосредственно в датчики. Рассмотрим в качестве примера преобразователь постоянного положительного напряжения в частоту (рис. 4).

Рис. 15.4. АЦП прямого преобразования.

АЦП выполнен на двух ОУ, усилитель OU1 включен в режиме интегратора, а усилитель OU2 - в режиме регенеративного компаратора с гистерезисом. Когда выходное напряжение компаратора Uf имеет максимальное положительное значение  , диод VD смещен в обратном направлении и напряжение Us на выходе OU1 уменьшается по линейному закону со скоростью, определяемой амплитудой входного положительного сигнала Ui, до тех пор, пока не достигнет значения

, диод VD смещен в обратном направлении и напряжение Us на выходе OU1 уменьшается по линейному закону со скоростью, определяемой амплитудой входного положительного сигнала Ui, до тех пор, пока не достигнет значения  R1/R2. В этот момент компаратор переключается в другое состояние, при котором напряжение на его выходе равно максимальному отрицательному значению

R1/R2. В этот момент компаратор переключается в другое состояние, при котором напряжение на его выходе равно максимальному отрицательному значению  , диод VD открывается и выходное напряжение интегратора быстро нарастает до значения

, диод VD открывается и выходное напряжение интегратора быстро нарастает до значения  R1/R2. При этом компаратор возвращается в первоначальное состояние и цикл повторяется.

R1/R2. При этом компаратор возвращается в первоначальное состояние и цикл повторяется.

Так как время нарастания выходного напряжения интегратора значительно меньше времени спада, которое обратно пропорционально амплитуде входного сигнала, частота циклов повторения F будет прямо пропорциональна входному напряжению. Пренебрегая собственным временем переключения компаратора, можно записать следующее выражение для частоты выходных импульсов:

F=UiR3 / [R1CR4 (U1-U2)]. (2)

Задание на подготовку к работе.

1.Изучить работу цифро-аналогового преобразователя.

2.Изучить работу аналого-цифрового преобразователя.

3.Изучить порядок выполнения работы и подготовить необходимые схемы и таблицы.

Порядок выполнения работы.

1. Исследование ЦАП с весовыми резисторами:

Соберите схему, изображенную на рис.1.

Все переключатели замкните на землю, как показано на рис. 1 и измерьте выходное напряжение

Переключатель A установите в положение логической 1 и измерьте выходное напряжение;

Устанавливайте переключатели В, C, D в положение логической 1 и измеряйте и записывайте выходное напряжение;

Используя данные, приведенные на схеме рис.1, рассчитайте выходное напряжение и сравните с измеряемыми, результаты запишите в таблицу 1.

Таблица 1

Ключ

A,B,C,D

A

A,B

A,B,C

A,B,C,D

Состояние

ключа

0

1

1

1

1

Uвых(изм.)

Uвых(рас.)

2. Исследование ЦАП лестничного типа:

Соберите схему, изображенную на рис.2;

Рассчитайте выходное напряжение для всех 16 комбинаций переключателей A,B,C,D по формуле (1) и запишите в таблицу 2, аналогичную табл.1.

Измерьте для всех 16 комбинаций переключателей A,B,C,D выходное напряжение ЦАП рис.2. Запишите в таблицу и сравните с расчетными величинами.

3. Исследование ЦАП лестничного типа на базе счетчика 74160:

Соберите схему, изображенную на рис. 3;

Используя формулу(1) и параметры схемы рис. 3, рассчитайте эквивалентное выходное напряжение;

Зарисуйте осциллограммы сигналов на счетном входе счетчика и выходе ЦАП и объясните полученные результаты.

Исследование АЦП прямого преобразования:

Соберите схему, изображенную на рис. 4;

Используя формулу 2 и параметры схемы рис. 4, рассчитайте частоту выходных импульсов;

Зарисуйте и объясните осциллограммы сигналов на выходе интегратора и компаратора.

Содержание отчета.

1.Наименование и цель лабораторной работы.

2.Наименование каждого пункта работы, схемы, результаты расчетов и измерений.

3.Выводы по результатам исследований

Лабораторная работа №3 «Исследование работы оперативного запоминающего устройства»

Цель работы: Закрепить теоретические знания об различных классах оперативных запоминающих устройствах (ОЗУ), их функциональном назначении и принципе работы.

Используемое оборудование и средства: персональный компьютер, программа Electronics Workbench.

Работа выполняется студентами за два часа аудиторных занятий

Краткие теоретические сведения.

Оперативные запоминающие устройства (ОЗУ) являются неотъемлемой частью микропроцессорных систем различного назначения. ОЗУ делятся на два класса: статические и динамические. В статических ОЗУ запоминание информации производится на триггерах, а в динамических - на конденсаторах емкостью порядка 0,5 пФ.

Длительность хранения информации в статических ОЗУ не ограничена, тогда как в динамических она ограничена временем саморазряда конденсатора, что требует специальных средств регенерации и дополнительных затрат времени на этот процесс.

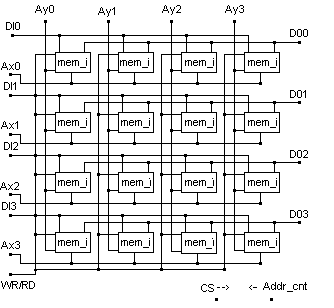

Рис. 14.1. Матрица 16-битного ОЗУ.

Конструктивно любое ОЗУ состоит из двух блоков - матрицы запоминающих элементов и дешифратора адреса. По технологическим соображениям матрица чаще всего имеет двухкоординатную дешифрацию адреса - по строкам и столбцам. На рис.1 показана матрица 16-битного статического ОЗУ. Матрица состоит из 16 ячеек памяти mem_i, схема которой приведена на рис.2. Каждая ячейка памяти адресуется по входам X,Y путём выбора дешифраторами адресных линий по строкам Ах0…Ах3 и по столбцам Ау0…Ау3 (см.рис.1) и подачи по выбранным линиям сигнала логической единицы. При этом в выбранной ячейке памяти срабатывает двухвходовой элемент И (U1), подготавливая цепи чтения-записи информации на входных D10…D13 или выходных DO0…DO3 разрядных шинах. Разрешающим сигналом для выдачи адреса является CS (chip select - выбор кристалла), который подаётся на вход разрешения счётчика адреса (Addr_cnt) или такой же вход дешифраторов, подключённых к выходам счётчика.

При записи в ячейку памяти (см. рис.2) на соответствующей разрядной шине устанавливается 1 или 0, на входе WR/RD устанавливается сигнал 1 и после стробирования счётчика или дешифратора адреса сигналом CS срабатывают элементы 2И U1, U2. Положительный перепад сигнала с элемента U2 поступает на тактовый вход D-триггера U4, в результате чего в нём записывается 1 или 0 в зависимости от уровня сигнала на его D-входе.

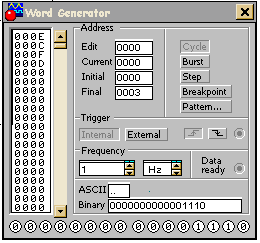

Рис. 14.2. Схема ячейки памяти mem_i.

Рис. 14.3. Лицевая панель генератора слова с установками для схемы на рис. 2.

При чтении из ячейки памяти на входе WR/RD устанавливается 0, при этом срабатывают элементы U1, U3,U5 и на вход РАЗРЕШЕНИЕ ВЫХОДА буферного элемента U6 поступает разрешающий сигнал, в результате чего сигнал с Q-выхода D-триггера передаётся на разрядную шину DO0…DO3. Для проверки функционирования ячейки памяти используется генератор слова рис. 3.

В микропроцессорных системах в качестве ОЗУ чаще всего используются динамические ОЗУ с запоминающим конденсатором, которые отличаются большим многообразием. Примером динамической памяти является FPM DRAM (Fast Page Mode DRAM -динамическая память с быстрым страничным доступом), активно используется в последнее время. Память со страничным доступом отличается от обычной динамической памяти тем , что после выбора строки матрицы и удержания сигнала RAS допускает многократную установку адреса столбца , стробируемого сигналом CAS , а также быструю регенерацию по схеме « CAS прежде RAS» . Первое позволяет ускорить блочные передачи, когда весь блок данных или его часть находятся внутри одной строки матрицы, называемой в этой системе страницей , а второе - снизить затраты времени на регенерацию памяти.

Кроме основного ОЗУ, устройством памяти снабжается и устройство отображения информации - видеодисплейная система. Такая память называется видеопамятью и располагается на плате видеоадаптера.